Professional Documents

Culture Documents

PDP 2006

PDP 2006

Uploaded by

Roberto De Leon MartinezCopyright:

Available Formats

You might also like

- Philips 32pw8422/77 Chassis L05laaDocument86 pagesPhilips 32pw8422/77 Chassis L05laaRicardo E. Roldán100% (1)

- Service: ManualDocument155 pagesService: Manualdennischauvin3973No ratings yet

- Relay Testing ProcedureDocument50 pagesRelay Testing ProcedureChandra Sekhar71% (7)

- Desktop Dell HNJFVDocument51 pagesDesktop Dell HNJFVjoao batistaNo ratings yet

- Understanding Electrical DrawingsDocument55 pagesUnderstanding Electrical DrawingsEl Comedor BenedictNo ratings yet

- Control Dirección y PWM Motor DC NIDocument21 pagesControl Dirección y PWM Motor DC NIEuler Deza FigueroaNo ratings yet

- HTS3500S DVD Receiver: Contents Page Contents PageDocument36 pagesHTS3500S DVD Receiver: Contents Page Contents PageAnonymous C6Vaod9100% (1)

- PCB Troubleshooting Techniques 818958Document3 pagesPCB Troubleshooting Techniques 818958Edgar Dauzon50% (2)

- 318 y h05vv F Bs en 50525 2 11 Flexible CableDocument3 pages318 y h05vv F Bs en 50525 2 11 Flexible CableAthanasius Kurniawan Prasetyo AdiNo ratings yet

- C&S LightingDocument28 pagesC&S LightingPrashant gaur100% (1)

- Thgbmbg5d1kbail A19nm 4gb E-Mmc Ver5.0 - e - Rev1.0 - 140807 - Pre-Loading Data ...Document32 pagesThgbmbg5d1kbail A19nm 4gb E-Mmc Ver5.0 - e - Rev1.0 - 140807 - Pre-Loading Data ...Rahmat HidayatNo ratings yet

- C-Band Dro LNB Teardown - Kf5obs - IpDocument8 pagesC-Band Dro LNB Teardown - Kf5obs - Ipkhanafzaal2576No ratings yet

- 01 Mon - Jun23 Trouble Shooting - Panel (Compatibility Mode)Document51 pages01 Mon - Jun23 Trouble Shooting - Panel (Compatibility Mode)بوند بوندNo ratings yet

- He390hh E51+auo T390XVN01 0 PDFDocument29 pagesHe390hh E51+auo T390XVN01 0 PDFLeudin Russo PedrozaNo ratings yet

- Hack 555 Toy Piano For Better Sound QualityDocument16 pagesHack 555 Toy Piano For Better Sound QualityIsabel Cesilia Reales HernandezNo ratings yet

- TroubleshootingDocument47 pagesTroubleshootingIsidro MendozaNo ratings yet

- Jtag Repair For Bricked Cloud Ibox 2 Plus & Cloud - Our Dreambox World - Japhar Sim Forum - HTTP - WWW - Japhar.com - SuperSimDocument4 pagesJtag Repair For Bricked Cloud Ibox 2 Plus & Cloud - Our Dreambox World - Japhar Sim Forum - HTTP - WWW - Japhar.com - SuperSimVladimir ZamuraevNo ratings yet

- Panasonic 2009 PDP TC-P54Z1 TC-P54V10 TC-P50V10 TC-P50G15 TC-P46G15 TC-P42G15 TC-P54G10 TC-P50G10 TC-P46G10 TC-P42G10 TC-P54S1 TC-P50S1 TC-P46S1 TC-P42S1 TCDocument46 pagesPanasonic 2009 PDP TC-P54Z1 TC-P54V10 TC-P50V10 TC-P50G15 TC-P46G15 TC-P42G15 TC-P54G10 TC-P50G10 TC-P46G10 TC-P42G10 TC-P54S1 TC-P50S1 TC-P46S1 TC-P42S1 TCedNo ratings yet

- Circuit Diagram For WS6908 PDFDocument6 pagesCircuit Diagram For WS6908 PDFdistefano67% (3)

- CCFL TesterDocument1 pageCCFL TesterSilvia LimaNo ratings yet

- LG Jig PDFDocument100 pagesLG Jig PDFPredrag NemcicNo ratings yet

- Manual de Servicio SONY KDL-55HX857Document53 pagesManual de Servicio SONY KDL-55HX857paelocom8550100% (1)

- Vizio Gv47l Fhdtv10a Service ManualDocument164 pagesVizio Gv47l Fhdtv10a Service Manualbrazamanzinho67% (3)

- Sony Play Station 2.service Manual - Level 1.SCPH 30000-50000Document27 pagesSony Play Station 2.service Manual - Level 1.SCPH 30000-50000zack9mm2003No ratings yet

- Samsung UN32EH5000FXZA Fast Track TroubleshootingDocument8 pagesSamsung UN32EH5000FXZA Fast Track TroubleshootingelelolNo ratings yet

- Example 3G Config - Option Globetrotter HSDPA USB ModemDocument23 pagesExample 3G Config - Option Globetrotter HSDPA USB ModemCristinel TanaseNo ratings yet

- Training Content SM-G7102 (Galaxy Grand2) HWDocument69 pagesTraining Content SM-G7102 (Galaxy Grand2) HWПаха КирьяновNo ratings yet

- Exploring Windows 10Document18 pagesExploring Windows 10api-277940890No ratings yet

- Toshiba UM 32E200U 37E200U 40E200U Chasis E200U Manual EntrenamientoDocument38 pagesToshiba UM 32E200U 37E200U 40E200U Chasis E200U Manual EntrenamientoPablo Acapulco GuerreroNo ratings yet

- Samsung Curve TrainingDocument33 pagesSamsung Curve Trainingautrera50% (2)

- Panasonic Ptxxlcx70lifilcdptv TrainingDocument56 pagesPanasonic Ptxxlcx70lifilcdptv Trainingvideoson100% (1)

- Panasonic TH l32c10s Km02 ChassisDocument126 pagesPanasonic TH l32c10s Km02 ChassisJanJan Cobarobias CorderoNo ratings yet

- 50HP81SVMDocument101 pages50HP81SVMClinton McDadeNo ratings yet

- TCL Led24c310a (Tsumv39lv t7s)Document6 pagesTCL Led24c310a (Tsumv39lv t7s)rammerDankovNo ratings yet

- TH L32X10MDocument130 pagesTH L32X10Mboroda2410No ratings yet

- Product Service Training 2015 - v3.0Document86 pagesProduct Service Training 2015 - v3.0Nicu LiviuNo ratings yet

- Talking Electronics Led TorchDocument27 pagesTalking Electronics Led TorchKalFowleNo ratings yet

- Service Manual: ChassisDocument130 pagesService Manual: ChassisEdwar Hernando VelásquezNo ratings yet

- Slim TV Service Manual - Sy33 ChassisDocument45 pagesSlim TV Service Manual - Sy33 ChassisUmar MajeedNo ratings yet

- LG Led 84LM9600 SMDocument111 pagesLG Led 84LM9600 SMFrancisco Orozco100% (1)

- 2 +India+LCD+SEMINAR+2007+-+for+panasonic PDFDocument114 pages2 +India+LCD+SEMINAR+2007+-+for+panasonic PDFCristea GabrielNo ratings yet

- DSB-B350S Training ManualDocument46 pagesDSB-B350S Training Manualax63naNo ratings yet

- Sony Kdl-32fa600 Chassis Az1-K Ver1.0Document24 pagesSony Kdl-32fa600 Chassis Az1-K Ver1.0Carlos Javier Cahuich BañosNo ratings yet

- NAND EngDocument16 pagesNAND EngPaulo TeixeiraNo ratings yet

- LG 37LH55 LCD TV Presentation Training ManualDocument81 pagesLG 37LH55 LCD TV Presentation Training Manualdann222No ratings yet

- Samsung Pd22eo Chassis Lw22a13w LCD TV SMDocument96 pagesSamsung Pd22eo Chassis Lw22a13w LCD TV SMchiru.stefan5869No ratings yet

- VDWALL LVP615S HD Video Processor For Super Large Pixel LED DisplayDocument112 pagesVDWALL LVP615S HD Video Processor For Super Large Pixel LED DisplayJc MartínezNo ratings yet

- 9619 Samsung Chassis U57E Chassis U57F Chassis U56G Televisor LED-LCD Manual de ServicioDocument91 pages9619 Samsung Chassis U57E Chassis U57F Chassis U56G Televisor LED-LCD Manual de Serviciocalderon64No ratings yet

- Service Manual: KLV-26L500A KLV-26L500A KLV-32L500A KLV-32L500A KLV-37L500A KLV-37L500ADocument87 pagesService Manual: KLV-26L500A KLV-26L500A KLV-32L500A KLV-32L500A KLV-37L500A KLV-37L500Apaelocom855050% (2)

- LVDS To Vga ConverterDocument26 pagesLVDS To Vga ConverterMark MorleyNo ratings yet

- LG 32lb620d DJ Chassis Lt43b Rev00Document74 pagesLG 32lb620d DJ Chassis Lt43b Rev00martijnkuipersNo ratings yet

- Tutorial para Fuentes de Poder LCDDocument37 pagesTutorial para Fuentes de Poder LCDioham4715100% (1)

- AOC Protron Pltv-1530a-E5 LCD TV-MonitorDocument59 pagesAOC Protron Pltv-1530a-E5 LCD TV-MonitorCaptain444No ratings yet

- Motherboard and BiosDocument26 pagesMotherboard and BiosJoseph Mediano PogoyNo ratings yet

- Toshiba 27wl56p 32wl56p 37wl56ptraining (ET)Document73 pagesToshiba 27wl56p 32wl56p 37wl56ptraining (ET)Mohamed SalahNo ratings yet

- Philips+HTS5500 CDocument56 pagesPhilips+HTS5500 CLuiz Roberto Honório Alves Filho100% (1)

- Haier 29T5A Service ID3602 PDFDocument64 pagesHaier 29T5A Service ID3602 PDFPedro Dueñas PiedraNo ratings yet

- L04a Ad 3122785158810Document96 pagesL04a Ad 3122785158810Вячеслав ЖигалкинNo ratings yet

- L05.1U - AA - .PDF - PHILIPS - 30PW9110D - Service ManualDocument97 pagesL05.1U - AA - .PDF - PHILIPS - 30PW9110D - Service Manualalvaradorivas22No ratings yet

- Tpm4.1ela 689Document64 pagesTpm4.1ela 689Anonymous 3SCkL0No ratings yet

- Aeg-Dvd4535 Service ManualDocument25 pagesAeg-Dvd4535 Service ManualSerp19720% (1)

- Training Material of RT49A-LA Chassis 20140612042844457Document37 pagesTraining Material of RT49A-LA Chassis 20140612042844457بوند بوندNo ratings yet

- 945GCT/GZT-M: Page Title of SchematicDocument33 pages945GCT/GZT-M: Page Title of SchematicJean GaroniNo ratings yet

- ASCO Transfer SwitchDocument20 pagesASCO Transfer SwitchdjibtapzNo ratings yet

- Arar-battery&Battery Charger 26.10.2004 CalDocument22 pagesArar-battery&Battery Charger 26.10.2004 Calsrigirisetty208No ratings yet

- Relai Reverse PowerDocument6 pagesRelai Reverse PowerFebby Hadi PrakosoNo ratings yet

- Andy Timmons MesaDocument1 pageAndy Timmons MesaJuliano Augusto MedeirosNo ratings yet

- HVDC Transmission Using Voltage Source Converters: AbstractDocument8 pagesHVDC Transmission Using Voltage Source Converters: AbstractVelu SamyNo ratings yet

- Conduit Fill Calc LatestDocument6 pagesConduit Fill Calc LatestThantZin111100% (1)

- GSK GR-L Series Servo Drive Unit ManualDocument131 pagesGSK GR-L Series Servo Drive Unit Manualjeovannyp100% (1)

- Maleta Demostrativa de MedidoresDocument12 pagesMaleta Demostrativa de MedidoresalfredNo ratings yet

- PN Junction DiodeDocument38 pagesPN Junction DiodeJairo TanyagNo ratings yet

- Sopan Pems Nayara (P) : CommentsDocument7 pagesSopan Pems Nayara (P) : CommentssidharthNo ratings yet

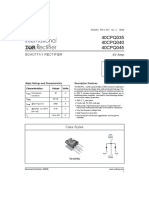

- 40CPQ045Document7 pages40CPQ045Giancarlo DilioNo ratings yet

- An 107Document7 pagesAn 107oscer959No ratings yet

- Esquema Hidráulico R1700k CarregadeiraDocument20 pagesEsquema Hidráulico R1700k CarregadeiraGlaycon AlanNo ratings yet

- Appendix 1 Transistor)Document6 pagesAppendix 1 Transistor)Achik SniperNo ratings yet

- DC Motor BrakingDocument15 pagesDC Motor BrakingSusmita DasNo ratings yet

- JR7000 ManualDocument165 pagesJR7000 Manualstt.bazilNo ratings yet

- RM 35 TF 30Document2 pagesRM 35 TF 30Marco GrijalbaNo ratings yet

- NomanDocument4 pagesNomanFaisal KhanNo ratings yet

- 4 - Fact Sheet CellD 300 enDocument3 pages4 - Fact Sheet CellD 300 enAhmedreyad35No ratings yet

- Pdc-Lab-Manual Transistor As A SwitchDocument2 pagesPdc-Lab-Manual Transistor As A SwitchappuamreddyNo ratings yet

- Surface Mount Transient Voltage Suppressor: Smb5.0 Thru Smb170CaDocument4 pagesSurface Mount Transient Voltage Suppressor: Smb5.0 Thru Smb170CaRaul CondorNo ratings yet

- Terasaki TemPower2 ACBDocument62 pagesTerasaki TemPower2 ACBMichelle ZancanellaNo ratings yet

- Code Device Manufactu Rer Base PackageDocument8 pagesCode Device Manufactu Rer Base PackageYousef HaeriNo ratings yet

- Internal Arc Testing of MV Switchgear IEC 62271-200 Part TwoDocument4 pagesInternal Arc Testing of MV Switchgear IEC 62271-200 Part TwodienlangchuNo ratings yet

- SE-Type 2 Co-Ordination Altivar 212Document1 pageSE-Type 2 Co-Ordination Altivar 212Krishna KumarNo ratings yet

- Cat WireSENSOR enDocument56 pagesCat WireSENSOR enJavier Del Pozo GarciaNo ratings yet

PDP 2006

PDP 2006

Uploaded by

Roberto De Leon MartinezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PDP 2006

PDP 2006

Uploaded by

Roberto De Leon MartinezCopyright:

Available Formats

1

1

PHILIPS TECHNICAL TRAINING

PLASMA PANEL REPAIR

2

3

ADDRESS ELECTRODES

BARRIER RIBS

4

DISPLAY ELECTRODES

5

FRONT GLASS PLATE

6

NEON XENON GAS

7

CHARGE / DISCHARGE CYCLE

Uses Neon Xenon gases

A voltage is applied between the Address

Electrodes and display electrodes to stimulate

ultraviolet radiation UV

UV stimulation causes color phosphors to glow

These form picture elements

7

8

PANEL Module Introduction PANEL Module Introduction

4. BLOCK DIAGRAM

8

9

10

11

12

SDI BUILT PANELS IN PHILIPS SETS ARE THE

ONLY PANELS FEATURED IN THIS TRAINING

12

13

13

14

14

15

15

16

16

17

18

PDP model name,

with or without PSU

10 1 3 03 26 0577

Type: 02 - 48

Line No: 1 -9

Year

Month: 01 - 12

Date: 01 - 31

Serial No: 0001 - 9999

Serial No

101303260577

Power supply

settings

18

PDP LABEL

19

20

21

22

23

42 INCH V4 PANEL USED IN BP SET WITH SSB REMOVED

Y DRIVER POWER SUPPLY

X-DRIVER LOGIC BOARD

E BOARDS

Y BUFFERS

24

50HDV3

25

50HDV4

26

Panel Location FM242 / FTP1.1 YD06 / YB04 Panels

42 INCH SDV2 MODULE LAYOUT

27

Panel module label Voltage label Serial No.

1 Logic Main

2 X-main

3 Y-main

8 Logic-buffer G

9 FFC Logic + Y-main

10 FFC Logic + X-main

4 Y-buffer upper

5 Y-buffer low

6 Logic-buffer E

7 Logic-buffer F

11 Logic + Logic buffer

12 Logic + Logic buffer

13 Logic + Logic buffer

1

2

3

4

5

6 7 8

9

10

11 12 13

PSU

SUB-

PSU

42 INCH SDV3 MODULE LAYOUT

28

SubL

PSU

Y-main Board

X-main board

Logic-buffer (E) Logic-buffer (F) Logic-buffer (G

Logic-buffer (H) Logic-buffer (I) Logic-buffer (J)

Y

-

b

u

f

f

e

r

u

p

Y

-

b

u

f

f

e

r

d

o

w

n

Logic-main board

SUB PSU

SubR

TCPs

50 INCH HD V3 MODULE LAYOUT

29

PICTURE OF 50 HD V3

29

30

.SMPS(Switching Mode Power Supply) : Supplies voltage and current to operate assemblies mounted to

each board and Panel.

.X Main Board : According to the timing provided from Logic board, switches FETs and generates driving

waveform which is provided to X electrode of Panel through Connector.

.Y Main Board :

According to the timing provided from Logic board, switches FETs and generate driving waveform which is

provided to Y electrode of Panel sequentially through Scan Driver IC of Scan Buffer.

.Logic Main Board : Processes image signal and generates Address driving output signal & XY driving

signal

.Logic Buffer Board(E,F,G) (+ Logic Buffer H, I, J if HD Display)

Transfers data signal and control signal to COF.

.Scan Buffer(Upper,Lower) : A board allows scan waveform to Y terminal, which is consisted of Upper

Board and Lower Board.

(Y-Buffer(Upper,Lower) )

.AC Noise Filter : Blocks noise and spikes and noise on the AC line.

.COF(Chip on Flexible) or (TCP Tape Carrier Package) : It allows Va pulse to address electrode within

address period and forms address discharge according to the electric potential difference between Va pulse

and the Scan pulse allowed to Y electrode. It is manufactured in COF form and one COF is consisted of four

DATA Drive IC .

30

31

TCP DRIVER

31

32

32

V2

33

PANEL DEFECTS

33

34

Defect : panel damage

Symptom : Panel crack or break. No image

appears in some cause depending on the

damaged parts and damage level.

Defect: Exhaust pipe damage

Symptom. : Crack in break if exhaust pipe an

image is partially lacking or the panel noise

occurs depending on the damaged parts and

after a certain time.

Or very loud noise from the panel.

Cause

Manufacturing : Flatness/palette pin

interruption

Operation : overload of panel corner /

careless handling

Panel : Flatness / assembly error

Cause : Carelessly panel handling

34

35

Check exhaust Tip for Cracks with naked eyes to check vacuum state.

If there is problem then replace the module by new one .

In case of vacuum breakdown, module makes a shaking noise because of inside gas ventilation.

(there may be a small crack which could not see with naked eyes. And this noise is different from Capacitor noise. )

1.2 Exhaust tip Crack

CRACKED NORMAL

35

36

Logic Main, Logic Buffer,

FFC, TCP

Some vertical lines appear to be

linked on Display

Address Short

Logic Main. Logic Buffer,

FFC, TCP

Some vertical lines dont exist on

the Display.

Address Open

Scan Buffer, FPC of X / Y Some horizontal lines appear to be

linked on Display.

Sustain Short

Scan Buffer, FPC of X / Y Some horizontal lines dont exist

on the Display

Sustain open

Y-Main, X-Main, Logic

Main

Abnormal Image (not open or

short) is on Display

Abnormal

Display

Y-Main, X-Main, Logic

Main, connections

Operating voltages exist, but no

Display

No Display

PSU Operating Voltages dont exist No voltage output

Related Board Description Symptom

36

37

Vertical stripe = Address open Vertical stripe = Address Short

Defect: Address output error

37

38

Defect horizontal stripe: Sustain Open Defect horizontal stripe: Sustain Short

Symptom : One or more line do not

light up in Sustain direction

Symptom : Combined or adjacent lines

are short in sustain direction. The line

appear brighter than other at Ramp

gradation pattern or low gradation patter

38

39

Address and Sustain Open Address Block and Line Open

Defect: Dielectric material layer damage

Symptom:

Phosphor damage caused by the damage of address bus dielectric layer

appears in the panel discharge/non discharge area. sustain also open/short

occurs by the damage of address sustain printout

Cause : layer uneven / abnormal voltage / foreign material repair failed.

39

40

Defect: Full White low discharge . Defect: Weak discharge

Symptom : Low discharge caused by unstable cells

occurring at full white pattern if high (60 degree) or

normal temperature.

Symptom : Normal discharge but cells appear

darker due to weak light emission occurring

mainly at low (5 degree) Full White/ Red/

Green/ Blue pattern or gradation pattern

40

41

DEFECTIVE TCP

42

42

DISASSEMBLY TIPS

43

CONNECTOR BETWEEN Y

UPPER AND LOWER ON

42HDV4 PANEL

42HDV4 PANEL

43

44

Removal

Pull out the FPC from connector by holding

the lead of the FPC with hands

Assembling

Push the lead of FPC with same strength until to be connected

completely.

Be careful do not damage the connector pin during connecting

DISASSEMBLY OF THE Y BUFFER

45

Disassembling

Pull out the connector clamp Pull Flat cable out press down lightly Move away from connector

Assembling

Put the Flat cable into the connector press down lightly until locking click

45

X BOARD CONNECTION

46

46

47

PRESS ON THE RIBBON CONNECTOR TO ENSURE

THAT IT IS PROPERLY SEATED

48

1 2 3 4 5 6 7

1) Remove the screws in order of 2-3-5-6-7-1-4 from

heat sink and then get rid of heat sink.

2) Remove the TPC, FFC and power cable from the

connectors.

3) Remove all of the screws from defected board.

4) Remove the defected board.

5) Replace the new board and then screw tightly.

6) Get rid of the foreign material from the connector.

7) Connect the TCP,FFC and power cable to the

connector.

8) Reassemble the TCP heat sink.

9) Screw in order of 4-1-7-6-5-3-2.

If you screw too tightly, it is possible to get damage

on the Driver IC of TCP.

Be care when using electric Screwdriver!

48

49

42HDV3 SCREW REMOVAL AND REPLACEMENT

50

Disassembling of TCP

Assembling of TCP

Open the clamp carefully Lift the TCP out from connector

Put the TCP into the connector carefully and check alignment Close the clamp completely, until locking click

50

51

TCP DRIVER

51

52

TROUBLESHOOTING

52

FIRST DETERMINE IF THE PROBLEM IS THE

THE SMALL SIGNAL BOARD OR THE PDP

PANEL PROBLEM

OPERATE PANEL IN INTERNAL (STAND ALONE)

CHECK POWER SUPPLY VOLTAGES

CHECK Y-BUFFER AND X-BOARD OUTPUTS

53

Trouble Shooting on No Display and Abnormal Display 42SDV2

53

SCOPE WITH DUAL TIME BASE DELAYED SWEEP REQUIRED

HIGH FREQUENCY REJ ECTION SWITCH MAY BE NEEDED TO

TRIGGER ON THE V-SYNC

54

V2 PANEL IN SERVICE POSITION WITH SSB/SCAVIO REMOVED

54

55

SHORT PINS 1 AND 2 OF CN8002

SHORT PIN 11(STANDBY) TO

GROUND TO SWITCH THE SET ON

OR

USE TEST JIG 3122 785 90760

55

V2

56

SHORT J8002 TO SWITCH

THE POWER SUPPLY VA

AND VS SUPPLIES.

56

V2

57

TP 13 V-SYNC

57

This test point location may change with a different logic board.

V-SYNC IS NECESSARY TO TRIGGER THE SCOPE

THE SCOPE MAY NOT TRIGGER WITHOUT A

HF REJ ECTION SWITCH

V2

58

V3

58

WITHOUT ADAPTER

CONNECT PIN 9 CN9005 TO PIN10 CN9004

CONNECT PIN 4 TO PIN 7 OF CN9005

59

1. Check Input Voltage Range of the defect

occurrence area is between 100V AC ~ 240V AC

2. Insert Jumper at J8003, J8004 BJ8902

3. Insert Power (AC) at CN8001

4. Check if the LED turn on or not as sequence.

(LED8001LED8002BD8903)

5. If all the LEDs (LED8001, LED8002, BD8903)

are ON, the PSU is not defective.

6. If one of the LEDs (LED8001, LED8002,

BD8903) is OFF, the PSU is defective.

CN8001

J8003

J8004

Right Position

BJ8902

LED8002

BD8903

LED8001

Protection & LED indication for Fault Finding

CHECKING THE V4 POWER SUPPLY UNLOADED

60

BJ 8902

BJ 8901

Alarm led

61

PSU troubleshoot

As verification, this is possible to disable

protection: by puting jumper BJ 8901 (on alarm

board)

This disables the protection circuits so that the

power supply operation can be checked

Caution: in this case there is a risk of more damages

61

V4

62

BJ 8902

SWITCHES ON THE VS SUPPLY WHEN THE LOGIC BOARD IS

NOT CONNECTED

63

Error codes can be read by counting the blinking rate of BD8903 LED located on the Alarm board.

BD8903

63

V4

64

13 TIMES D5VL OVP, UVP

4 TIMES D3V3 OVP, UVP

3 TIMES VSCAN OVP, UVP

2 TIMES 12V OVP, UVP

11 TIMES 5V2 OVP or Active DC_PROT

10 TIMES PFC_OK UVP (>330V)

9 TIMES Over Temperature (<105)

8 TIMES VE OVP, UVP

7 TIMES VSET OVP, UVP

6 TIMES VG OVP, UVP

5 TIMES VS OVP, UVP

1 TIME VA OVP, UVP

LED Signature Detect Error condition

64

V4

65

DC VOLTAGES AND CURRENTS 42SDV4 ONLY

65

V4

66

PLACE J UMPER HERE ON THE LOGIC BOARD TO

TURN THE SCREEN WHITE

V4

66

67

67

TEST WAVEFORMS

68

V Sync on Channel A CN201 2ms/Div/2V 5

6 Y Output on Out 4 100V/Div

X-Output TP Out 7

By use of Delayed Time Base

68

SCOPE SETTINGS 42SDV2

69

UPPER PULSE IS SYNC

LOWER IS OUTPUT OF Y

BUFFER

69

42SDV2

70

Y-BUFFER

X-BOARD

42HDV4 Y BUFFER USING x100 PROBE

71

71

ALIGNMENTS

72

72

NO ALIGNMENTS ARE NECESSARY WHEN REPLACING

THE FOLLOWING PANELS

X-BOARD

Y-BUFFER BOARDS

LOGIC BOARD

LOGIC DRIVER BOARDS (E)

73

73

POWER SUPPLY

THE POWER SUPPLY SHOULD BE CHECKED AND

ADJ USTED IF NECESSARY ACCORDING TO THE CHART

LOCATED ON THE PLASMA PANEL

EACH POWER SUPPLY IS SET TO OPTIMIZE EACH PANEL

74

VOLTAGE CHART

LOCATED IN THE UPPER RIGHT HAND CORNER

VIEW FROM THE BACK OF THE SET

SOME PANELS HAVE A DIFFERENT LOCATION

75

POWER BOARD ALIGNMENTS 42SDV4

SUB POWER BOARD

D3V3 VR9005 CHECK CHART

D6V VR9004 CHECK CHART

MAIN POWER BOARD

VSCAN VR8005 CHECK CHART

VSET VR8003 CHECK CHART

D3V3 VR8006 CHECK CHART

VSB VR8002 CHECK CHART

VE VR8008 CHECK CHART

VS VR8004 CHECK CHART

PFC VR8001 DO NOT ADJ UST

VA VR8007 CHECK CHART

75

76

After changing PSU, Check and

Adjust the

voltage of 8 points.

If turn right, voltage up

If turn left, voltage down

1.VS

2.VA

3.VSET

4.VSCAN

5.VE

6.D3V3

7.D5V

8.12VL

VSCAN

VE

Voltage

Up

VSET

VS

VA

12V

D5VL D3V3

Voltage

Down

76

V4

77

CONDITION CAUSED BY MISADJ USTED POWER SUPPLY

78

78

Y-DRIVER BOARD

THE Y-DRIVER ADJ USTMENTS SHOULD BE CHECKED

AND ADJ USTED IF NECESSARY TO OPTIMIZE PICTURE

PERFORMANCE

A DUAL TIME BASE OSCILLOSCOPE IS REQUIRED TO

MAKE ACCURATE ADJ USTMENTS

TO OBTAIN A STABLE WAVEFORM, SYNC THE

SCOPE TO THE V-SYNC ON THE LOGIC PANEL

THE Y-DRIVER MAY HAVE CHANGED IN PRODUCTION

MATCH THE PICTURE OF YOURS WITH THE ONE IN

THE SERVICE MANUAL TO VERIFY THAT THE

CORRECT ADJ USTMENTS ARE BEING PERFORMED

79

HIGHLIGHT THE WAVEFORM TO EXPAND

80

80

THE PREVIOUS EXAMPLE IS A WAVEFORM VIEWED

WITH A TEKTRONIX

OSCILLOSCOPE

EACH OSCILLOSCOPE WORKS A LITTLE

DIFFERENT

81

1) Make Full White on Screen.

2) Observe waveform using Oscilloscope.

check OUT4 TP in Y-buffer(upper).

Observe the waveform of the third waveform of 1TV-

Field.

Adjust the division of oscilloscope like the left picture

Adjust the period of Vset as 10S,

that of -Vsc(1) as 20s,

that of -Vsc(2) as 5s,

turning VR (Variable Resistor)

(only,when you adjust each period of -Vsc(1) & -Vsc(2)

adjust Vertical Division of oscilloscope as '2V or 5V')

VR for Vset : VR5003 (Y_main)

VR for -Vsc(1) : VR5001 (Y_main)

VR for -Vsc(2) : VR5002 (Y_main)

81

42SDV2

82

82

83

VR5002

Raising Ramp Flat Time

VR5003

Falling Ramp Flat Time

VR5004

VSCH

V Scan High

VR5001

3th Falling Ramp Flat Time

Y test point

V-Sync test point

83

84

1. VR5004 Adjustment : Vsch TP => 40volt

2. VR5002 Adjustment : Rising Ramp flat time: Typ. 10usec

4. VR5001 Adjustment : 3th SF Falling Ramp flat time => Typ. 30usec

3. VR5003 Adjustment : Falling Ramp flat time => Typ. 30usec

TP:Vsch

VR5004

84

42SDV3

85

10 VR5001 Falling_Ramp_3rd

20 VR5003 Falling_Ramp_1st

10 VR5002 Rising_Ramp 42HDV3

10 (10 ~ 15) Falling_Ramp_3rd

10 (10 ~ 15) Falling_Ramp_1st

30 (30 ~ 40) Rising_Ramp 37SDV4

30 VR5001 Falling_Ramp_3rd

30 VR5003 Falling_Ramp_1st

10 VR5002 Rising_Ramp 42SDV3

20 Falling_Ramp_3rd

35 Falling_Ramp_1st

50 Rising_Ramp 50HDV3

Default Adjusting Location No Wave Form

85

86

PLACE J UMPER HERE ON THE LOGIC BOARD TO

TURN THE SCREEN WHITE

VSYNC

OR VTOGG

GND

42HDV4

87

Y DRIVE TEST POINT

42HDV4

88

42HDV4

89

90

15V

RISING ADJ

X100 PROBE USED

91

92

50uS

100V

VR5002 FALLING ADJ

93

REFER TO THE PDP REPAIR MANUAL FOR ALL ADJ USTMENTS

93

94

WHEN REPLACING THE SSB, BE SURE TO

SET THE SCREEN NUMBER AND TYPE

THESE SHOULD BE LISTED IN THE SCREEN

SERVICE MANUAL

95

95

SCREEN DIVERSITY

WHEN CHANGING THE SSB, IT IS IMPORTANT TO

PROGRAM THE SCREEN DIVERSITY CODE AS SHOWN

ON THE OPTION CODE LABEL.

IF THE WRONG CODE HAS BEEN ENTERED CAUSING

THE SCREEN TO BE BLANK, THE DIVERSITY CODE

CAN BE RESET BY ENTERING 0 6 2 5 9 8 MENU FOLLOWED

BY THE CORRECT CODE.

96

97

You might also like

- Philips 32pw8422/77 Chassis L05laaDocument86 pagesPhilips 32pw8422/77 Chassis L05laaRicardo E. Roldán100% (1)

- Service: ManualDocument155 pagesService: Manualdennischauvin3973No ratings yet

- Relay Testing ProcedureDocument50 pagesRelay Testing ProcedureChandra Sekhar71% (7)

- Desktop Dell HNJFVDocument51 pagesDesktop Dell HNJFVjoao batistaNo ratings yet

- Understanding Electrical DrawingsDocument55 pagesUnderstanding Electrical DrawingsEl Comedor BenedictNo ratings yet

- Control Dirección y PWM Motor DC NIDocument21 pagesControl Dirección y PWM Motor DC NIEuler Deza FigueroaNo ratings yet

- HTS3500S DVD Receiver: Contents Page Contents PageDocument36 pagesHTS3500S DVD Receiver: Contents Page Contents PageAnonymous C6Vaod9100% (1)

- PCB Troubleshooting Techniques 818958Document3 pagesPCB Troubleshooting Techniques 818958Edgar Dauzon50% (2)

- 318 y h05vv F Bs en 50525 2 11 Flexible CableDocument3 pages318 y h05vv F Bs en 50525 2 11 Flexible CableAthanasius Kurniawan Prasetyo AdiNo ratings yet

- C&S LightingDocument28 pagesC&S LightingPrashant gaur100% (1)

- Thgbmbg5d1kbail A19nm 4gb E-Mmc Ver5.0 - e - Rev1.0 - 140807 - Pre-Loading Data ...Document32 pagesThgbmbg5d1kbail A19nm 4gb E-Mmc Ver5.0 - e - Rev1.0 - 140807 - Pre-Loading Data ...Rahmat HidayatNo ratings yet

- C-Band Dro LNB Teardown - Kf5obs - IpDocument8 pagesC-Band Dro LNB Teardown - Kf5obs - Ipkhanafzaal2576No ratings yet

- 01 Mon - Jun23 Trouble Shooting - Panel (Compatibility Mode)Document51 pages01 Mon - Jun23 Trouble Shooting - Panel (Compatibility Mode)بوند بوندNo ratings yet

- He390hh E51+auo T390XVN01 0 PDFDocument29 pagesHe390hh E51+auo T390XVN01 0 PDFLeudin Russo PedrozaNo ratings yet

- Hack 555 Toy Piano For Better Sound QualityDocument16 pagesHack 555 Toy Piano For Better Sound QualityIsabel Cesilia Reales HernandezNo ratings yet

- TroubleshootingDocument47 pagesTroubleshootingIsidro MendozaNo ratings yet

- Jtag Repair For Bricked Cloud Ibox 2 Plus & Cloud - Our Dreambox World - Japhar Sim Forum - HTTP - WWW - Japhar.com - SuperSimDocument4 pagesJtag Repair For Bricked Cloud Ibox 2 Plus & Cloud - Our Dreambox World - Japhar Sim Forum - HTTP - WWW - Japhar.com - SuperSimVladimir ZamuraevNo ratings yet

- Panasonic 2009 PDP TC-P54Z1 TC-P54V10 TC-P50V10 TC-P50G15 TC-P46G15 TC-P42G15 TC-P54G10 TC-P50G10 TC-P46G10 TC-P42G10 TC-P54S1 TC-P50S1 TC-P46S1 TC-P42S1 TCDocument46 pagesPanasonic 2009 PDP TC-P54Z1 TC-P54V10 TC-P50V10 TC-P50G15 TC-P46G15 TC-P42G15 TC-P54G10 TC-P50G10 TC-P46G10 TC-P42G10 TC-P54S1 TC-P50S1 TC-P46S1 TC-P42S1 TCedNo ratings yet

- Circuit Diagram For WS6908 PDFDocument6 pagesCircuit Diagram For WS6908 PDFdistefano67% (3)

- CCFL TesterDocument1 pageCCFL TesterSilvia LimaNo ratings yet

- LG Jig PDFDocument100 pagesLG Jig PDFPredrag NemcicNo ratings yet

- Manual de Servicio SONY KDL-55HX857Document53 pagesManual de Servicio SONY KDL-55HX857paelocom8550100% (1)

- Vizio Gv47l Fhdtv10a Service ManualDocument164 pagesVizio Gv47l Fhdtv10a Service Manualbrazamanzinho67% (3)

- Sony Play Station 2.service Manual - Level 1.SCPH 30000-50000Document27 pagesSony Play Station 2.service Manual - Level 1.SCPH 30000-50000zack9mm2003No ratings yet

- Samsung UN32EH5000FXZA Fast Track TroubleshootingDocument8 pagesSamsung UN32EH5000FXZA Fast Track TroubleshootingelelolNo ratings yet

- Example 3G Config - Option Globetrotter HSDPA USB ModemDocument23 pagesExample 3G Config - Option Globetrotter HSDPA USB ModemCristinel TanaseNo ratings yet

- Training Content SM-G7102 (Galaxy Grand2) HWDocument69 pagesTraining Content SM-G7102 (Galaxy Grand2) HWПаха КирьяновNo ratings yet

- Exploring Windows 10Document18 pagesExploring Windows 10api-277940890No ratings yet

- Toshiba UM 32E200U 37E200U 40E200U Chasis E200U Manual EntrenamientoDocument38 pagesToshiba UM 32E200U 37E200U 40E200U Chasis E200U Manual EntrenamientoPablo Acapulco GuerreroNo ratings yet

- Samsung Curve TrainingDocument33 pagesSamsung Curve Trainingautrera50% (2)

- Panasonic Ptxxlcx70lifilcdptv TrainingDocument56 pagesPanasonic Ptxxlcx70lifilcdptv Trainingvideoson100% (1)

- Panasonic TH l32c10s Km02 ChassisDocument126 pagesPanasonic TH l32c10s Km02 ChassisJanJan Cobarobias CorderoNo ratings yet

- 50HP81SVMDocument101 pages50HP81SVMClinton McDadeNo ratings yet

- TCL Led24c310a (Tsumv39lv t7s)Document6 pagesTCL Led24c310a (Tsumv39lv t7s)rammerDankovNo ratings yet

- TH L32X10MDocument130 pagesTH L32X10Mboroda2410No ratings yet

- Product Service Training 2015 - v3.0Document86 pagesProduct Service Training 2015 - v3.0Nicu LiviuNo ratings yet

- Talking Electronics Led TorchDocument27 pagesTalking Electronics Led TorchKalFowleNo ratings yet

- Service Manual: ChassisDocument130 pagesService Manual: ChassisEdwar Hernando VelásquezNo ratings yet

- Slim TV Service Manual - Sy33 ChassisDocument45 pagesSlim TV Service Manual - Sy33 ChassisUmar MajeedNo ratings yet

- LG Led 84LM9600 SMDocument111 pagesLG Led 84LM9600 SMFrancisco Orozco100% (1)

- 2 +India+LCD+SEMINAR+2007+-+for+panasonic PDFDocument114 pages2 +India+LCD+SEMINAR+2007+-+for+panasonic PDFCristea GabrielNo ratings yet

- DSB-B350S Training ManualDocument46 pagesDSB-B350S Training Manualax63naNo ratings yet

- Sony Kdl-32fa600 Chassis Az1-K Ver1.0Document24 pagesSony Kdl-32fa600 Chassis Az1-K Ver1.0Carlos Javier Cahuich BañosNo ratings yet

- NAND EngDocument16 pagesNAND EngPaulo TeixeiraNo ratings yet

- LG 37LH55 LCD TV Presentation Training ManualDocument81 pagesLG 37LH55 LCD TV Presentation Training Manualdann222No ratings yet

- Samsung Pd22eo Chassis Lw22a13w LCD TV SMDocument96 pagesSamsung Pd22eo Chassis Lw22a13w LCD TV SMchiru.stefan5869No ratings yet

- VDWALL LVP615S HD Video Processor For Super Large Pixel LED DisplayDocument112 pagesVDWALL LVP615S HD Video Processor For Super Large Pixel LED DisplayJc MartínezNo ratings yet

- 9619 Samsung Chassis U57E Chassis U57F Chassis U56G Televisor LED-LCD Manual de ServicioDocument91 pages9619 Samsung Chassis U57E Chassis U57F Chassis U56G Televisor LED-LCD Manual de Serviciocalderon64No ratings yet

- Service Manual: KLV-26L500A KLV-26L500A KLV-32L500A KLV-32L500A KLV-37L500A KLV-37L500ADocument87 pagesService Manual: KLV-26L500A KLV-26L500A KLV-32L500A KLV-32L500A KLV-37L500A KLV-37L500Apaelocom855050% (2)

- LVDS To Vga ConverterDocument26 pagesLVDS To Vga ConverterMark MorleyNo ratings yet

- LG 32lb620d DJ Chassis Lt43b Rev00Document74 pagesLG 32lb620d DJ Chassis Lt43b Rev00martijnkuipersNo ratings yet

- Tutorial para Fuentes de Poder LCDDocument37 pagesTutorial para Fuentes de Poder LCDioham4715100% (1)

- AOC Protron Pltv-1530a-E5 LCD TV-MonitorDocument59 pagesAOC Protron Pltv-1530a-E5 LCD TV-MonitorCaptain444No ratings yet

- Motherboard and BiosDocument26 pagesMotherboard and BiosJoseph Mediano PogoyNo ratings yet

- Toshiba 27wl56p 32wl56p 37wl56ptraining (ET)Document73 pagesToshiba 27wl56p 32wl56p 37wl56ptraining (ET)Mohamed SalahNo ratings yet

- Philips+HTS5500 CDocument56 pagesPhilips+HTS5500 CLuiz Roberto Honório Alves Filho100% (1)

- Haier 29T5A Service ID3602 PDFDocument64 pagesHaier 29T5A Service ID3602 PDFPedro Dueñas PiedraNo ratings yet

- L04a Ad 3122785158810Document96 pagesL04a Ad 3122785158810Вячеслав ЖигалкинNo ratings yet

- L05.1U - AA - .PDF - PHILIPS - 30PW9110D - Service ManualDocument97 pagesL05.1U - AA - .PDF - PHILIPS - 30PW9110D - Service Manualalvaradorivas22No ratings yet

- Tpm4.1ela 689Document64 pagesTpm4.1ela 689Anonymous 3SCkL0No ratings yet

- Aeg-Dvd4535 Service ManualDocument25 pagesAeg-Dvd4535 Service ManualSerp19720% (1)

- Training Material of RT49A-LA Chassis 20140612042844457Document37 pagesTraining Material of RT49A-LA Chassis 20140612042844457بوند بوندNo ratings yet

- 945GCT/GZT-M: Page Title of SchematicDocument33 pages945GCT/GZT-M: Page Title of SchematicJean GaroniNo ratings yet

- ASCO Transfer SwitchDocument20 pagesASCO Transfer SwitchdjibtapzNo ratings yet

- Arar-battery&Battery Charger 26.10.2004 CalDocument22 pagesArar-battery&Battery Charger 26.10.2004 Calsrigirisetty208No ratings yet

- Relai Reverse PowerDocument6 pagesRelai Reverse PowerFebby Hadi PrakosoNo ratings yet

- Andy Timmons MesaDocument1 pageAndy Timmons MesaJuliano Augusto MedeirosNo ratings yet

- HVDC Transmission Using Voltage Source Converters: AbstractDocument8 pagesHVDC Transmission Using Voltage Source Converters: AbstractVelu SamyNo ratings yet

- Conduit Fill Calc LatestDocument6 pagesConduit Fill Calc LatestThantZin111100% (1)

- GSK GR-L Series Servo Drive Unit ManualDocument131 pagesGSK GR-L Series Servo Drive Unit Manualjeovannyp100% (1)

- Maleta Demostrativa de MedidoresDocument12 pagesMaleta Demostrativa de MedidoresalfredNo ratings yet

- PN Junction DiodeDocument38 pagesPN Junction DiodeJairo TanyagNo ratings yet

- Sopan Pems Nayara (P) : CommentsDocument7 pagesSopan Pems Nayara (P) : CommentssidharthNo ratings yet

- 40CPQ045Document7 pages40CPQ045Giancarlo DilioNo ratings yet

- An 107Document7 pagesAn 107oscer959No ratings yet

- Esquema Hidráulico R1700k CarregadeiraDocument20 pagesEsquema Hidráulico R1700k CarregadeiraGlaycon AlanNo ratings yet

- Appendix 1 Transistor)Document6 pagesAppendix 1 Transistor)Achik SniperNo ratings yet

- DC Motor BrakingDocument15 pagesDC Motor BrakingSusmita DasNo ratings yet

- JR7000 ManualDocument165 pagesJR7000 Manualstt.bazilNo ratings yet

- RM 35 TF 30Document2 pagesRM 35 TF 30Marco GrijalbaNo ratings yet

- NomanDocument4 pagesNomanFaisal KhanNo ratings yet

- 4 - Fact Sheet CellD 300 enDocument3 pages4 - Fact Sheet CellD 300 enAhmedreyad35No ratings yet

- Pdc-Lab-Manual Transistor As A SwitchDocument2 pagesPdc-Lab-Manual Transistor As A SwitchappuamreddyNo ratings yet

- Surface Mount Transient Voltage Suppressor: Smb5.0 Thru Smb170CaDocument4 pagesSurface Mount Transient Voltage Suppressor: Smb5.0 Thru Smb170CaRaul CondorNo ratings yet

- Terasaki TemPower2 ACBDocument62 pagesTerasaki TemPower2 ACBMichelle ZancanellaNo ratings yet

- Code Device Manufactu Rer Base PackageDocument8 pagesCode Device Manufactu Rer Base PackageYousef HaeriNo ratings yet

- Internal Arc Testing of MV Switchgear IEC 62271-200 Part TwoDocument4 pagesInternal Arc Testing of MV Switchgear IEC 62271-200 Part TwodienlangchuNo ratings yet

- SE-Type 2 Co-Ordination Altivar 212Document1 pageSE-Type 2 Co-Ordination Altivar 212Krishna KumarNo ratings yet

- Cat WireSENSOR enDocument56 pagesCat WireSENSOR enJavier Del Pozo GarciaNo ratings yet