Professional Documents

Culture Documents

OpAmp - LF351 (NatSem - Wideband Opamp)

OpAmp - LF351 (NatSem - Wideband Opamp)

Uploaded by

Ludwig SchmidtCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

OpAmp - LF351 (NatSem - Wideband Opamp)

OpAmp - LF351 (NatSem - Wideband Opamp)

Uploaded by

Ludwig SchmidtCopyright:

Available Formats

TLH5648

L

F

3

5

1

W

i

d

e

B

a

n

d

w

i

d

t

h

J

F

E

T

I

n

p

u

t

O

p

e

r

a

t

i

o

n

a

l

A

m

p

l

i

f

i

e

r

December 1995

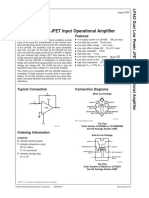

LF351 Wide Bandwidth JFET Input Operational Amplifier

General Description

The LF351 is a low cost high speed JFET input operational

amplifier with an internally trimmed input offset voltage

(BI-FET II

TM

technology) The device requires a low supply

current and yet maintains a large gain bandwidth product

and a fast slew rate In addition well matched high voltage

JFET input devices provide very low input bias and offset

currents The LF351 is pin compatible with the standard

LM741 and uses the same offset voltage adjustment circuit-

ry This feature allows designers to immediately upgrade the

overall performance of existing LM741 designs

The LF351 may be used in applications such as high speed

integrators fast DA converters sample-and-hold circuits

and many other circuits requiring low input offset voltage

low input bias current high input impedance high slew rate

and wide bandwidth The device has low noise and offset

voltage drift but for applications where these requirements

are critical the LF356 is recommended If maximum supply

current is important however the LF351 is the better

choice

Features

Y

Internally trimmed offset voltage 10 mV

Y

Low input bias current 50 pA

Y

Low input noise voltage 25 nV0Hz

Y

Low input noise current 001 pA0Hz

Y

Wide gain bandwidth 4 MHz

Y

High slew rate 13 Vms

Y

Low supply current 18 mA

Y

High input impedance 10

12

X

Y

Low total harmonic distortion A

V

e10

k

002%

R

L

e10k V

O

e20 Vp-p BWe20 Hz20 kHz

Y

Low 1f noise corner 50 Hz

Y

Fast settling time to 001% 2 ms

Typical Connection

TLH564811

Simplified Schematic

TLH564812

Connection Diagrams

Dual-In-Line Package

TLH564813

Order Number LF351M or LF351N

See NS Package Number M08A or N08E

C1995 National Semiconductor Corporation RRD-B30M125Printed in U S A

Absolute Maximum Ratings

If MilitaryAerospace specified devices are required

please contact the National Semiconductor Sales

OfficeDistributors for availability and specifications

Supply Voltage g18V

Power Dissipation (Notes 1 and 6) 670 mW

Operating Temperature Range 0C to a70C

T

j(MAX)

115C

Differential Input Voltage g30V

Input Voltage Range (Note 2) g15V

Output Short Circuit Duration Continuous

Storage Temperature Range b65C to a150C

Lead Temp (Soldering 10 sec)

Metal Can 300C

DIP 260C

i

jA

N Package 120CW

M Package TBD

Soldering Information

Dual-In-Line Package

Soldering (10 sec) 260C

Small Outline Package

Vapor Phase (60 sec) 215C

Infrared (15 sec) 220C

See AN-450 Surface Mounting Methods and Their Effect

on Product Reliability for other methods of soldering sur-

face mount devices

ESD rating to be determined

DC Electrical Characteristics (Note 3)

Symbol Parameter Conditions

LF351

Units

Min Typ Max

V

OS

Input Offset Voltage R

S

e 10 kX T

A

e 25C 5 10 mV

Over Temperature 13 mV

DV

OS

DT Average TC of Input Offset R

S

e10 kX

10 mVC

Voltage

I

OS

Input Offset Current T

j

e 25C (Notes 3 4) 25 100 pA

T

j

s

70C 4 nA

I

B

Input Bias Current T

j

e 25C (Notes 3 4) 50 200 pA

T

j

s g70C 8 nA

R

IN

Input Resistance T

j

e25C 10

12

X

A

VOL

Large Signal Voltage Gain V

S

eg15V T

A

e25C 25 100 VmV

V

O

eg10V R

L

e2 kX

Over Temperature 15 VmV

V

O

Output Voltage Swing V

S

eg15V R

L

e10 kX g12 g135 V

V

CM

Input Common-Mode Voltage a15 V

Range V

S

eg15V g11

b12 V

CMRR Common-Mode Rejection Ratio R

S

s

10 kX 70 100 dB

PSRR Supply Voltage Rejection Ratio (Note 5) 70 100 dB

I

S

Supply Current 18 34 mA

2

AC Electrical Characteristics (Note 3)

Symbol Parameter Conditions

LF351

Units

Min Typ Max

SR Slew Rate V

S

eg15V T

A

e25C 13 Vms

GBW Gain Bandwidth Product V

S

eg15V T

A

e25C 4 MHz

e

n

Equivalent Input Noise Voltage T

A

e25C R

S

e100X

25 nV0Hz

fe1000 Hz

i

n

Equivalent Input Noise Current T

j

e25C fe1000 Hz 001 pA0Hz

Note 1 For operating at elevated temperature the device must be derated based on the thermal resistance i

JA

Note 2 Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage

Note 3 These specifications apply for V

S

eg15V and 0CsT

A

sa70C V

OS

I

B

and I

OS

are measured at V

CM

e0

Note 4 The input bias currents are junction leakage currents which approximately double for every 10C increase in the junction temperature T

j

Due to the limited

production test time the input bias currents measured are correlated to junction temperature In normal operation the junction temperature rises above the ambient

temperature as a result of internal power dissipation P

D

T

j

eT

A

ai

jA

P

D

where i

jA

is the thermal resistance from junction to ambient Use of a heat sink is

recommended if input bias current is to be kept to a minimum

Note 5 Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice From

g15V to g5V

Note 6 Max Power Dissipation is defined by the package characteristics Operating the part near the Max Power Dissipation may cause the part to operate

outside guaranteed limits

3

Typical Performance Characteristics

Input Bias Current Input Bias Current Supply Current

Positive Common-Mode

Input Voltage Limit

Negative Common-Mode

Input Voltage Limit Positive Current Limit

Negative Current Limit Voltage Swing Output Voltage Swing

Gain Bandwidth Bode Plot Slew Rate

TLH56482

4

Typical Performance Characteristics (Continued)

Distortion vs Frequency

Undistorted Output

Voltage Swing

Open Loop Frequency

Response

Common-Mode

Rejection Ratio

Power Supply

Rejection Ratio

Equivalent Input

Noise Voltage

Open Loop Voltage

Gain (VV) Output Impedance Inverter Settling Time

TLH56483

5

Pulse Response

Small Signal Inverting

TLH56484

Small Signal Non-Inverting

TLH56485

Large Signal Inverting

TLH56486

Large Signal Non-Inverting

TLH56487

Current Limit (R

L

e100X)

TLH56488

Application Hints

The LF351 is an op amp with an internally trimmed input

offset voltage and JFET input devices (BI-FET II

TM

) These

JFETs have large reverse breakdown voltages from gate to

source and drain eliminating the need for clamps across the

inputs Therefore large differential input voltages can easily

be accommodated without a large increase in input current

The maximum differential input voltage is independent of

the supply voltages However neither of the input voltages

should be allowed to exceed the negative supply as this will

cause large currents to flow which can result in a destroyed

unit

Exceeding the negative common-mode limit on either input

will force the output to a high state potentially causing a

reversal of phase to the output

Exceeding the negative common-mode limit on both inputs

will force the amplifier output to a high state In neither case

does a latch occur since raising the input back within the

6

Application Hints (Continued)

common-mode range again puts the input stage and thus

the amplifier in a normal operating mode

Exceeding the positive common-mode limit on a single input

will not change the phase of the output however if both

inputs exceed the limit the output of the amplifier will be

forced to a high state

The amplifier will operate with a common-mode input volt-

age equal to the positive supply however the gain band-

width and slew rate may be decreased in this condition

When the negative common-mode voltage swings to within

3V of the negative supply an increase in input offset voltage

may occur

The LF351 is biased by a zener reference which allows nor-

mal circuit operation on g4V power supplies Supply volt-

ages less than these may result in lower gain bandwidth and

slew rate

The LF351 will drive a 2 kX load resistance to g10V over

the full temperature range of 0C to a70C If the amplifier

is forced to drive heavier load currents however an in-

crease in input offset voltage may occur on the negative

voltage swing and finally reach an active current limit on

both positive and negative swings

Precautions should be taken to ensure that the power supply

for the integrated circuit never becomes reversed in polarity

or that the unit is not inadvertently installed back-

wards in a socket as an unlimited current surge through the

resulting forward diode within the IC could cause fusing of

the internal conductors and result in a destroyed unit

As with most amplifiers care should be taken with lead

dress component placement and supply decoupling in or-

der to ensure stability For example resistors from the out-

put to an input should be placed with the body close to the

input to minimize pick-up and maximize the frequency of

the feedback pole by minimizing the capacitance from the

input to ground

A feedback pole is created when the feedback around any

amplifier is resistive The parallel resistance and capaci-

tance from the input of the device (usually the inverting in-

put) to AC ground set the frequency of the pole In many

instances the frequency of this pole is much greater than

the expected 3 dB frequency of the closed loop gain and

consequently there is negligible effect on stability margin

However if the feedback pole is less than approximately 6

times the expected 3 dB frequency a lead capacitor should

be placed from the output to the input of the op amp The

value of the added capacitor should be such that the RC

time constant of this capacitor and the resistance it parallels

is greater than or equal to the original feedback pole time

constant

Detailed Schematic

TLH56489

7

Typical Applications

Supply Current IndicatorLimiter

V

OUT

switches high when R

S

I

S

l V

D

Hi-Z

IN

Inverting Amplifier

Parasitic input capacitance C1 j (3 pF for LF351

plus any additional layout capacitance) interacts

with feedback elements and creates undesirable

high frequency pole To compensate add C2 such

that R2C2 j R1C1

Ultra-Low (or High) Duty Cycle

Pulse Generator

t

OUTPUT HIGH

R1C n

48 b 2V

S

48 b V

S

t

OUTPUT LOW

R2C n

2V

S

b 78

V

S

b 78

where V

S

e V

a

a

l

V

b

l

low leakage capacitor

Long Time Integrator

Low leakage capacitor

50k pot used for less sensitive V

OS

adjust

TLH564810

8

Physical Dimensionsinches (millimeters)

SO Package (M)

Order Number LF351M

NS Package Number M08A

9

L

F

3

5

1

W

i

d

e

B

a

n

d

w

i

d

t

h

J

F

E

T

I

n

p

u

t

O

p

e

r

a

t

i

o

n

a

l

A

m

p

l

i

f

i

e

r

Physical Dimensionsinches (millimeters) (Continued)

Molded Dual-In-Line Package (N)

Order Number LF351N

NS Package Number N08E

LIFE SUPPORT POLICY

NATIONALS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL

SEMICONDUCTOR CORPORATION As used herein

1 Life support devices or systems are devices or 2 A critical component is any component of a life

systems which (a) are intended for surgical implant support device or system whose failure to perform can

into the body or (b) support or sustain life and whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system or to affect its safety or

with instructions for use provided in the labeling can effectiveness

be reasonably expected to result in a significant injury

to the user

National Semiconductor National Semiconductor National Semiconductor National Semiconductor

Corporation Europe Hong Kong Ltd Japan Ltd

1111 West Bardin Road Fax (a49) 0-180-530 85 86 13th Floor Straight Block Tel 81-043-299-2309

Arlington TX 76017 Email cnjwgetevm2nsccom Ocean Centre 5 Canton Rd Fax 81-043-299-2408

Tel 1(800) 272-9959 Deutsch Tel (a49) 0-180-530 85 85 Tsimshatsui Kowloon

Fax 1(800) 737-7018 English Tel (a49) 0-180-532 78 32 Hong Kong

Franais Tel (a49) 0-180-532 93 58 Tel (852) 2737-1600

Italiano Tel (a49) 0-180-534 16 80 Fax (852) 2736-9960

National does not assume any responsibility for use of any circuitry described no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications

You might also like

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- lm386 PDFDocument11 pageslm386 PDFNicolás MoraNo ratings yet

- LF353Document13 pagesLF353cromus_9000No ratings yet

- TL081Document9 pagesTL081Vero PorrasNo ratings yet

- OpAmp - LF451Document8 pagesOpAmp - LF451Ludwig SchmidtNo ratings yet

- LF444 Quad Low Power JFET Input Operational Amplifier: General Description FeaturesDocument11 pagesLF444 Quad Low Power JFET Input Operational Amplifier: General Description FeaturesJohn PachecoNo ratings yet

- Opamp - Lf147 Lf347 - NatsemDocument13 pagesOpamp - Lf147 Lf347 - NatsemLudwig SchmidtNo ratings yet

- TL082 EqualizerDocument16 pagesTL082 EqualizerMecabot DzibNo ratings yet

- Tl082cp Datasheet de National Semiconductor para Sustituir Ci de Etapa Pre Amplificador Bunker Mx2400 2Document12 pagesTl082cp Datasheet de National Semiconductor para Sustituir Ci de Etapa Pre Amplificador Bunker Mx2400 2Jess AJNo ratings yet

- tl082cp DatasheetDocument15 pagestl082cp DatasheetHeriberto Flores AmpieNo ratings yet

- Datasheet LF 353Document14 pagesDatasheet LF 353Anggridho MeilandanuNo ratings yet

- Datasheet LF412CNDocument14 pagesDatasheet LF412CNJose Fernando Perdomo BolañosNo ratings yet

- LF442Document14 pagesLF442atavachronNo ratings yet

- Lm386 DatasheetDocument7 pagesLm386 DatasheetJM Carrasco HottmanNo ratings yet

- LM 1875Document13 pagesLM 1875pblhnrqNo ratings yet

- LM108A/LM208A/LM308A Operational Amplifiers: General DescriptionDocument8 pagesLM108A/LM208A/LM308A Operational Amplifiers: General DescriptioncrizerNo ratings yet

- LM3900Document20 pagesLM3900Wilfredo MarquezNo ratings yet

- LF442CNDocument13 pagesLF442CNFSNo ratings yet

- tl082 Op Amp DatasheetDocument23 pagestl082 Op Amp DatasheetnurburgNo ratings yet

- Boost Controller With Power Factor CorrectionDocument14 pagesBoost Controller With Power Factor CorrectionChiseledPrawnNo ratings yet

- LF347n PDFDocument13 pagesLF347n PDFDiego PeñuelaNo ratings yet

- LF155Document24 pagesLF155Brzata PticaNo ratings yet

- Tda 8143Document9 pagesTda 8143Luis Arturo Leiva MonjarasNo ratings yet

- Act 4065Document9 pagesAct 4065bob75No ratings yet

- LM1875TDocument11 pagesLM1875TEdgar RodriguezNo ratings yet

- Unisonic Technologies Co.,: Low Voltage Audio Power AmplifierDocument7 pagesUnisonic Technologies Co.,: Low Voltage Audio Power Amplifierantonio_forgioneNo ratings yet

- LM1875T PDFDocument14 pagesLM1875T PDFAnang SurotoNo ratings yet

- LF347BNDocument15 pagesLF347BNDavid Emmanuel Contreras MadrigalNo ratings yet

- LM358 PDFDocument14 pagesLM358 PDFChetan KotwalNo ratings yet

- Data SheetDocument10 pagesData SheetselocaNo ratings yet

- Tda 1904Document11 pagesTda 1904Adrian PérezNo ratings yet

- PT1301Document9 pagesPT1301dcastrelos2000No ratings yet

- LM78S40 Universal Switching Regulator Subsystem: General Description FeaturesDocument9 pagesLM78S40 Universal Switching Regulator Subsystem: General Description FeaturesgusguicorNo ratings yet

- TDF8591TH: 1. General DescriptionDocument34 pagesTDF8591TH: 1. General DescriptionJoel T LardizábalNo ratings yet

- 3A, 24V Asynchronous Step Down DC/DC Converter: Description FeaturesDocument10 pages3A, 24V Asynchronous Step Down DC/DC Converter: Description FeaturesMax NiNo ratings yet

- LM138, LM338 5-Amp Adjustable Regulators: General DescriptionDocument14 pagesLM138, LM338 5-Amp Adjustable Regulators: General DescriptionrrebollarNo ratings yet

- LF 351Document14 pagesLF 351Ivan PetrovicNo ratings yet

- TE CH: Features General DescriptionDocument10 pagesTE CH: Features General DescriptionJuan VillanuevaNo ratings yet

- OpAmp - LM308AN - National Semiconductor - 49173 - DSDocument9 pagesOpAmp - LM308AN - National Semiconductor - 49173 - DSLudwig SchmidtNo ratings yet

- Wide Bandwidth Dual J-Fet Operational Amplifiers: LF153 LF253 - LF353Document10 pagesWide Bandwidth Dual J-Fet Operational Amplifiers: LF153 LF253 - LF353JOSELVCNo ratings yet

- LF 353Document10 pagesLF 353Ylv Csar Mñz MdoNo ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- High Power Class D Audio Power Amplifier Using IR2011SDocument22 pagesHigh Power Class D Audio Power Amplifier Using IR2011SAbubakar SidikNo ratings yet

- Iraudamp1 - High Power Class D Audio Power Amplifier Using IR2011SDocument24 pagesIraudamp1 - High Power Class D Audio Power Amplifier Using IR2011SChuYurNo ratings yet

- LM148/LM248/LM348 Quad 741 Op Amps: General DescriptionDocument4 pagesLM148/LM248/LM348 Quad 741 Op Amps: General DescriptionJunedy Pandapotan SaragihNo ratings yet

- LM2727/LM2737 N-Channel FET Synchronous Buck Regulator Controller For Low Output VoltagesDocument22 pagesLM2727/LM2737 N-Channel FET Synchronous Buck Regulator Controller For Low Output VoltagesselocaNo ratings yet

- Unisonic Technologies Co., LTD: Low Noise Quad J-Fet Operational AmplifierDocument5 pagesUnisonic Technologies Co., LTD: Low Noise Quad J-Fet Operational Amplifiergaldos08No ratings yet

- General Description Features: Wide Input 3A Step-Down ConverterDocument10 pagesGeneral Description Features: Wide Input 3A Step-Down Converterban4444No ratings yet

- LM 833Document11 pagesLM 833Pablo ZajariasNo ratings yet