Professional Documents

Culture Documents

Design of FPGA-based All Digital PID Controller For Dynamic Systems

Uploaded by

123kailashOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design of FPGA-based All Digital PID Controller For Dynamic Systems

Uploaded by

123kailashCopyright:

Available Formats

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 64

Design of FPGA-based All Digital PID

Controller for Dynamic Systems

Vipul B. Patel

1

, Virendra singh

2

, Ravi H.Acharya

3

Dept. of Electronics and Communication Engineering, Sagar Institute of Research and Technology, Bhopal,

Madhaya Pradesh, India

1,2,3

vbpatel678@gmail.com

1

, virendrasingh1180@gmail.com

2

, raviacharya7@gmail.com

3

Abstract: In this paper implementation of All digital PID controller using Field Programmable Gate array (FPGA) is

presented. Nowadays embedded control applications requires low power and fast acting PID controllers with a closed

loop performance using less resources, resulting in cost reduction. In digital PID controller error signal is generated by

using comparator which is analog in nature. By using ADC it is converted in to digital. Digital output of FPGA is

converted in to analog signal to drive any system using DAC, but potential output ripple in the baseline system due to

quantization and other related errors. There is no need to use ADC or DAC in ADPID. The controller algorithm is

synthesized, simulated using Xilinx Spartan3e XC3S100E board with XilinxISE 10.1i as a tool.

Keywords: FPGA, ADPID, ADC, Verilog

I. Introduction

The development of PID (Proportional-Integral-Derivative) control theories has already 60 years so far, PID

control has been one of the control system design method of the longest history. However, this method is still

extensively used now [1, 2]. PID-controller and its modifications are the most common controllers in the

industry. It is robust and simple to design, its operation is well known, it has a good noise tolerance, it is

inexpensive and it is commercially available [2].

Implementation of digital PID controller has gone through several stages of evolution, from the early

mechanical and pneumatic designs to the microprocessor based systems but these systems have the drawback

of demanding control requirements of modern power conditioning systems will overload most of the

microprocessors and the computing speed limits the use of microprocessor in complex algorithms.

Microprocessors, Microcontrollers and Digital Signal Processors (DSPs) can no longer keep pace with the

new generation of applications that requires more flexible and higher performance without increasing cost and

resources. Furthermore the tasks are executed sequentially which takes longer processing time to accomplish

the same task in Microcontrollers and DSPs. Recently, Field Programmable Gate Arrays (FPGA) has

becoming alternative solution for the realization of digital control systems. The FPGA based controllers offer

advantages such as high speed computation, complex functionality, real time processing capabilities and low

power consumption [3]. In this paper we consider All digital PID controller and is implemented in a dedicated

FPGA. Following the standard digital design practices, the controller functionality is described in Verilog.

Using synthesis tool, the design is then targeted to the FPGA board.The FPGA is a superior alternative to

mask programmed ASICs. FPGAs avoid the high initial cost, the lengthy development cycles, and the

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 65

inherent inflexibility of conventional ASICs. Also, FPGA programmability permits design upgrades in the

field with no hardware replacement necessary, an impossibility with ASICs. Section II give structure of PID

controller, Section III includes advantages of FPGA based system, Section IV and V give basic idea about

Digital systems and ADPID controller and Section VI application of PID controller.

II.PID Controller

PID control, shown in fig. 1, is one of the earlier control strategies .

Figure 1 Block diagram of simple PID feedback control system

Its early implementation was in pneumatic devices, followed by vacuum and solid state analog electronics,

before arriving at todays digital implementation via microprocessors or FPGA. It has a simple control

structure which was understood by plant operators which they found relatively easy to tune. Since many

control systems using PID control have proved its satisfactory performance, it still has a wide range of

applications in industrial control [8] and it has been an active research topic for many years. Mathematically,

..(1)

III. Advantages of FPGA based Designs

Field Programmable Gate Arrays (FPGA) has become an alternative solution for the realization of digital

control systems, previously dominated by the general-purpose microprocessor systems [4,5]. The FPGA-

based controllers offer advantages such as high speed, complex functionality, and low power consumption.

These are attractive features from the embedded systems design point of view. Previous work has reported the

use of FPGAs in digital feedback control systems such as magnetic bearings, PWM inverters, induction

motors, AC/DC converters, variable-speed drives, and anti-windup compensation of controllers.

FPGA offers the most preferred way of designing ADPID controller for temperature control application. They

are basically interconnection between different logic blocks. When design is implemented on FPGA they are

designed in such a way that they can be easily modified if any need arise in future. We have to just change the

interconnection between these logic blocks. This feature of Reprogramming capability of FPGA makes it

suitable to make your design using FPGA. Also using FPGA we can implement design within a short time.

Thus FPGA is the best way of designing digital PID controller. Also implementation of FPGA-based digital

control schemes proves less costly and hence they are economically suitable for small designs.

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 66

IV.Digital control system

In todays scenario of globalization the implementation of production innovation and highly stable operation

is the main objective of the process industry in Japan. A recent survey [2] shows that the ratio of applications

of PID control, conventional advanced control (feed forward, override, valve position control, gain scheduled

PID, etc.) and model predictive control is about 100:10:1.One important activity is improvement in the control

performance of PID control systems. The aims of this improvement activity in which controllers are retuned

appropriately are [2].

1) To realize stable operation by reducing the influence of disturbances

2) To realize automatic rapid transition of operating conditions such as production rate.

3) To gain the ability to achieve economical operation.

4) To allow operators to be released from taking care of PID controllers.

Obviously, modern advanced control plays an important role to achieve this target but it is emphasize that a

key to success is the maximum utilization of PID control and conventional advanced control. The digital

Proportional Integral Derivative (PID) controller is one of the most common types of feedback controllers

used in dynamic systems. This controller has been widely used in many different areas such as aerospace,

process control, manufacturing, robotics, automation, and transportation systems. Implementation of PID

controllers has gone through several stages of evolution from the early mechanical and pneumatic designs to

the microprocessor based systems.

A. I dentify Problem Category of analog PI D based controller

This is the first step in which consider whether evaluation involves an existing analog PID controller problem

or one that could result from a new design or from proposed changes to the system. In addition different

factors are involves for decide the accuracy and stability problem Category like, overshoot, steady state error,

internal noise of analog component, signal distortion.

B. Evaluate Solution

Solutions that are not technically viable get thrown out, and the rest of the alternatives are compared on an

economic basis. Digital PID based control system consist of ADC at input side to convert comparator based

generated error signal in to digital signal. This digital signal is process by FPGA. Digital output signal from

FPGA is given to DAC. Which converts digital signal in to analog to drive any system like speed control of

DC motor, liquid level control in tank, temperature control, flow control of valve etc. in automation industries.

C. Evaluate Solution

One concept in digital PID based control system consist of ADC at input side to convert error signal in to

digital signal and DAC at output side to convert signal in to analog to drive any system like speed control of

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 67

DC motor, liquid level control in tank, temperature control, flow control of valve etc. in automation industries.

Another concept is instead of converting error signal in to digital using ADC, convert incoming input signal in

to frequency which is basically a digital signal using 555 timer. So in this concept we do not require ADC as

well as DAC which can be costly and may introduce error and delay into the system and this system is known

as ALL DIGITAL PID CONTROL SYSTEM (ADPID).

V.All Digital PID Controllers

To design an ADPID requires the knowledge to generate a proportional digital signal of the error, an integral

digital signal for the errors over time, and a derivative digital signal for the change in error. These three

separate signals need to be combined together to form a PWM control signal. An ADPID is mainly

constructed by digital logic devices, such as 4-bit up/down counters, JK flip-flop, D flip-flop, multiplexer, and

digital gates (i.e. AND, OR, EXOR). In general, the error between the reference and encoded output is

counted up or down by counters. The speed of counting depends on frequencies fP, fI and fD. Then, the

summation of the counters is counted to zero at frequency fA. The control signal generated by an ADPID is in

PWM form, and the corresponding direction is determined by the most significant bit of the adders.

Figure 2 Block Diagram of ADPID

It is totally frequency base method of PID control. The gain of the P, I, D term can be adjust by simply setting

the appropriate frequency of the counter for the P, I, D term and the frequency of the final summation

counter[7].

The gain of the Proportional

P

K , integral

I

K and derivatives

D

K are define by using the frequency of the

counters.

P

P

A

f

K

f

.(2)

I

I

A

f

K

f

.(3)

D

D

A

f

K

f

(4)

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 68

The base frequency, fA, is the counting frequency for the combined counters. It is directly related to fP, fI and

fD. It can be determined after any one of the proportional, integral or derivative frequencies is known.

Technically, low frequencies cause inaccurate counting, whereas extremely high counting frequencies create

problems such as integrator windup. As a result, more hardware is needed to prevent counting overflow.

Hence it is crucial to design a proper counting frequency, to obtain an accurate model yet reduce the hardware

to the minimum.

Figure 3 Basic structure of ADPID

1.Error signal

To generate the error signal we need the reference signal and the feedback signal from the system. By

comparing these two signals we can generate the error signal.

A. Generate Reference signal

Generated reference is a set of pulse trains that represents the desired output of the encoder. The resolution of

the encoder used in the system determines the frequency of the pulses. For example, if a linear encoder

represents 1 Volt with one hundred and fifty pulses, the frequency of the reference will be the desired voltage

multiplied by one hundred fifty. The conversion from analog voltage to digital pulse train can be done by

crystal, 555 Timer, or a Voltage-Controlled-Oscillator (VCO).In our application we use timer 555 timer to

generate the reference signal.

B. Feedback Signal

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 69

Feedback signal is the raw system output transformed into digital pulses by an encoder. Among the many

encoders, encoder strips and encoder disks are commonly installed in systems. In our system we use the

encoder disk which is mounted on the motor shaft. The disc passes through the opto-coupler and gives the

train of pulses.

Figure 4 Pulse train of desired output, system output, error, error magnitude and error Direction signals

Table 1 Summary of proportional counting action

Generated

Reference

Feedback

Signal

Error

Error

Direction

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

2. All Digital PI D signal

An all digital PID signal composed of mainly three terms:

1) Proportional Error signal

2) Integral Error signal

3) Derivative Error signal

Addition of the three terms (P, I, D)

As the error signal transitions from high to low, the count-down counter (CA) loads the results from the adder

(CP+ CI + (CD-R)). The counting direction depends on the result from the adder. If the most significant bit

(MSB) of the adder is 1, the summation of the three terms is negative; thus the combined counter will count

up at frequency fA to zero. On the other hand, if the MSB of the adder is 0, the summation of the three terms

is positive; then the combined counter counts down at frequency fA to zero. However, the counting sequence is

interrupted when load is activated. In this case, the combined counters discontinue the previous counting and

pick up the new loaded number.

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 70

The whole logic operation of the combine counter is summarized in the below truth table with

respect to the state of error signal and MSB of the summation.

Table 2 Summary of combine counting action

Error MSB

from

adder

Operation of

combine counter

0 0 Load the summation

from the adder and

countdown @ f

A

until

zero is reached

0 1 Load the summation

from the adder and

countdown @ f

A

until

zero is reached

1 0 Continue countdown

if zero is not reached

1 1 Continue count up if

zero is not reached

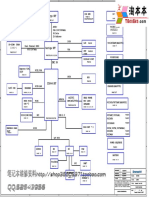

VI. Proposed design of combine PID

Figure 5 Proposed design of 12 bit combine up/down counter

VII.Proposed System architecture

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 71

Figure 6 Proposed System architecture

Proposed architecture is shown in Fig. 6

VIII.Conclusion

There are lots of research is going on PID implementation using FPGAs.PID is mostly used

controller in industry from last several years. FPGAs are reconfigurable device which can be

programmed by user as per their need, so this advantage is very useful for online tuning of the

PID while implementing it on FPGAs. All Digital PID is the new aspect in the industrial

controller. It is totally base on the frequency. The row data from the system can be directly given

to the system and the controllers output can directly given to the system. This avoids the use of

analog to digital converter, Which reduce the error and the cost of the system design.

REFERENCES

[1] Fakhrulddin H. Ali, Mohammed Mahmood Hussien, Siman M.B. ISmel, Labview FPGA Implementation Of a PID Controller for D.C.

Motor Speed Control, 2010 1

ST

International Conference on Energy, Power and Control(EPC-IQ), College of Engineering, University of Basrah,

Iraq, November 30- Dec 2010.

[2] Wang Yu, Jiang Cunbo, Wang Sheng, Improvement and Simulation of Temperature Parameter Identification, 2011 Third International

Conference on Measuring Technology and Mechatronics Automation,ISSN 978-0-7695-4296-6/11

[3] Sreenivasappa.B.V, Dr. Udaykumar.R.Y, Design and Implementation of FPGA Based Low Power Digital PID Controllers, Fourth

International Conference on Industrial and Information Systems, ICIIS 2009, 28 - 31December 2009,Page No.568-573, ISSN:978-1-4244-4837-

1/09,Sri Lanka

[4] T. Nandha Kumar, Tarek Mohd A.K AL Saleh, SRS.Prabaharan, Haider A.F. Mohamed, An FPGA Based Temperature Controller for

Differential Thermal Analyzer, ICROS-SICE International Joint Conference 2009 August 18-21, 2009, Fukuoka International Congress Center,

Japan

[5] M. Sultan. M. Siddiqui, A.H.Sajid and D.G.Chougule, FPGA Based Efficient Implementation of PID Control Algorithm,

INTERNATIONAL CONFERENCE ON CONTROL,AUTOMATION, COMMUNICATION AND ENERGY CONSERVATION -2009, 4th-

6th June 2009

[6] Hai-bo LIN, A Kind of Intelligent Temperature Controller Use PID Algorithm to Realize,IEEE conference ,Page no.2338-2340,ISSN:978-

1-4244-8165-1/11,2011

[7] Chin, Hui Hui, All Digital Design and Implementation of Propotional-Integral-Derivaive Comtroller, Master thesis.

Biography

Vipul B. Patel

1

did his B.E. in Electronics and Communication Engineering from North Gujarat

University, Patan, Gujarat. He is doing M.Tech. in Electronics and Communication at Sagar

ISSN 2278 - 8875

International J ournal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

Vol. 1, Issue 2, August 2012

Copyright to IJAREEIE www.ijareeie.com 72

Institute of Research and Technology, Bhopal, Madhaya Pradesh from Rajiv

Gandhi Technological University, Bhopal, Madhya Pradesh. His research areas

are VLSI design and Technology also in Semiconductor and Electronics field.

Virendra Singh

2

is Assistant Professor in Sagar Institute of Science and

Technology, Bhopal. He is a member of Vigyan Bharti. He has masters degree in

Micro electronics and VLSI design. Two of his papers are published in IEEE

Explorer on Image processing.

Ravi H. Acharya

3

did his B.E. in Electronics and Telecommunication

Engineering from North Maharashtra University, Jalgaon, Maharashtra. He is

doing M.Tech. in Electronics and Communication at Sagar Institute of Research

and Technology, Bhopal, Madhaya Pradesh from Rajiv Gandhi Technological

University, Bhopal, Madhya Pradesh. His research areas are VLSI design and

Technology also in Digital Image Processing..

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5796)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Poly Ultra Nails Construction Adhesive-Aus SdsDocument7 pagesPoly Ultra Nails Construction Adhesive-Aus SdsGavin PintoNo ratings yet

- Fuelmiser Engine ManagementDocument431 pagesFuelmiser Engine ManagementGavin PintoNo ratings yet

- Kingspan Insulation Concrete Wall ApplicationDocument8 pagesKingspan Insulation Concrete Wall ApplicationGavin PintoNo ratings yet

- Bosch 43li Service ManualDocument4 pagesBosch 43li Service ManualGavin Pinto0% (1)

- Product Overview: Tl494: PWM Controller (Up To 200 KHZ)Document2 pagesProduct Overview: Tl494: PWM Controller (Up To 200 KHZ)Gavin PintoNo ratings yet

- Presentation Thomas A LipoDocument69 pagesPresentation Thomas A LipoGavin PintoNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (589)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Resurrection of My MC6800-based MicrocomputerDocument12 pagesResurrection of My MC6800-based MicrocomputerRandom73No ratings yet

- Emas Ik If It CatalogueDocument6 pagesEmas Ik If It CatalogueGerardo Andres Cañaveral ArenasNo ratings yet

- Valcom Paging GuideDocument12 pagesValcom Paging GuideJose Maria IlizaliturriNo ratings yet

- SDNDocument3 pagesSDNkjmadniNo ratings yet

- AlphaDocument158 pagesAlphaMuhamad HanifNo ratings yet

- Blackdiamond 8800 Series Switches Hardware Installation GuideDocument202 pagesBlackdiamond 8800 Series Switches Hardware Installation GuidesbalaguruNo ratings yet

- LM339 LM239 LM2901 DatasheetDocument8 pagesLM339 LM239 LM2901 DatasheetEza RezaNo ratings yet

- Commisioning Report of House of Fashion FinalDocument9 pagesCommisioning Report of House of Fashion FinalSanjeewa ChathurangaNo ratings yet

- Astra Install GuideDocument20 pagesAstra Install GuideColbert JohnesNo ratings yet

- TV TrainerDocument2 pagesTV TrainerFederico EstradaNo ratings yet

- 20-F 2007 PDFDocument1,502 pages20-F 2007 PDFNihan GunawanNo ratings yet

- CM-340CCT4320C Conductivity Controller Operation ManualDocument2 pagesCM-340CCT4320C Conductivity Controller Operation ManualBimesh WaterbirdNo ratings yet

- ASUS X51RL Rev2.0 Schematic DiagramDocument64 pagesASUS X51RL Rev2.0 Schematic DiagramLégrádi ZoltánNo ratings yet

- Acer Back To School PromoDocument9 pagesAcer Back To School PromoAubrey CaballeroNo ratings yet

- 04 WN - SP2010 - E01 - 1 ZXWN CS Signaling and Interface-66Document66 pages04 WN - SP2010 - E01 - 1 ZXWN CS Signaling and Interface-66Iyesusgetanew100% (1)

- IoT Lab 2Document15 pagesIoT Lab 2Arshad KhanNo ratings yet

- Use Case Diagram ShopeeDocument6 pagesUse Case Diagram ShopeeAtmayantiNo ratings yet

- Industrial Control: Solutions GuideDocument32 pagesIndustrial Control: Solutions GuideAmet koko TaroNo ratings yet

- Compresor y Limitador TL Audio de ValvulasDocument12 pagesCompresor y Limitador TL Audio de ValvulasNicolas ZuluagaNo ratings yet

- ARM7 UM10139 - LPC214xDocument354 pagesARM7 UM10139 - LPC214xnilmak2u2No ratings yet

- 6RA80 Fault Diagnostics enDocument78 pages6RA80 Fault Diagnostics enRavindra Angal100% (2)

- BMS Spec For WL48-100FT16Document18 pagesBMS Spec For WL48-100FT16Roberto Antonio Yance Hemer100% (2)

- Locker SystemDocument31 pagesLocker SystemAyush SinghNo ratings yet

- Panasonic DriveDocument24 pagesPanasonic DriveEmmanuel Ebere ObiNo ratings yet

- 6d767 Lenovo X301.schematicsDocument102 pages6d767 Lenovo X301.schematicsboy1 bghyjNo ratings yet

- S Cubed DatasheetDocument2 pagesS Cubed DatasheetGulf JobzNo ratings yet

- CPUDocument7 pagesCPUWerry sudiwijayaNo ratings yet

- Implementation of Pid Controller by Microcontroller of Pic 18F SeriesDocument4 pagesImplementation of Pid Controller by Microcontroller of Pic 18F Seriespedroh95No ratings yet

- Onyxworks® Gateways: NFN Fire MonitoringDocument2 pagesOnyxworks® Gateways: NFN Fire MonitoringMinhthien NguyenNo ratings yet