Professional Documents

Culture Documents

Secx5018

Secx5018

Uploaded by

nksarathy0 ratings0% found this document useful (0 votes)

4 views2 pagesSathyabama Univ QP

Original Title

201273-45659-SECX5018

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentSathyabama Univ QP

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

4 views2 pagesSecx5018

Secx5018

Uploaded by

nksarathySathyabama Univ QP

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 2

Register Number

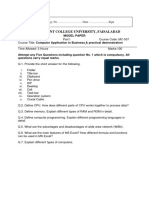

SATHYABAMA UNIVERSITY

(Established under section 3 of UGC Act, 1956)

Course & Branch: M.E/M.Tech-EMBED/VLSI

Title of the Paper: VLSI Design

Sub. Code: SECX5018

Date: 11/12/2010

Max. Marks: 80

Time: 3 Hours

Session: FN

______________________________________________________________________________________________________________________

PART - A

(6 X 5 = 30)

Answer ALL the Questions

1.

Draw the small signal model for MOS transistor and explain the

different parameters. Write the expression for transconductance.

2.

Explain the noise margin of CMOS circuit with neat diagram.

3.

Draw the layout diagram for Half adder.

4.

Design a 3:1 Mux using CMOS logic.

5.

Explain the structure of Barrel shifter with diagram.

6.

Explain the operation of Six transistor Static CMOS Memory

Cell structure.

7.

8.

PART B

(5 x 10 = 50)

Answer ALL the Questions

Explain the energy band diagram of MOS structure while

conducting with energy work function and derive the expression

for threshold voltage.

(or)

Explain all the secondary effects of MOSFET with necessary

diagram and expressions.

9.

What is DRC? Explain the n-well rules with neat diagram.

(or)

10. Explain n/p ratio. Explain how the characteristics differ in

saturated and depleted load inverter.

11. Draw the SUM part of the full adder in dynamic CMOS and

Clocked CMOS logic.

(or)

12. What is PLA? Draw the structure of PLA for the following using

MOS structure.

(a) Z1 = a + b

(b) Z2 = ab + cd

(c) Z3 = (a+b) (c+d)

13. Explain the characteristics of Gate, diffusion and routing

capacitance in CMOS.

(or)

14. Draw 4 bit dynamic shift register with CMOS arrangement and

draw stick diagram for shift register cells.

15. Explain the carry select and carry skip adder structure with neat

diagram.

(or)

16. Explain the structure of 2s complement Multiplication using

Baugh Wooley method.

You might also like

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumbernksarathyNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberlavanyachandranNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Monica MorinNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberVijay VivegananthanNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberBalaji RakeshNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberGoverdhan GovaNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberVinoth SudalaiNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberVinoth SudalaiNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumbervempadareddyNo ratings yet

- Sathyabama University Question PaperDocument2 pagesSathyabama University Question PaperamiestudentNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)1balamanianNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Vidya MuthukrishnanNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberAmmuRaNo ratings yet

- Elements of Aeronatics Sathyabama PDFDocument2 pagesElements of Aeronatics Sathyabama PDFsenthilkumareceNo ratings yet

- sathyabama-IIsem-Advanced Internet Technology-683203-783202Document2 pagessathyabama-IIsem-Advanced Internet Technology-683203-783202ShankarNo ratings yet

- Satthyabama-Isem-Data Comunication and Computer Networks 6C0500-7C0500Document2 pagesSatthyabama-Isem-Data Comunication and Computer Networks 6C0500-7C0500ShankarNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)yaswanthmalaikaniNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberAshok KumarNo ratings yet

- 5.principles of Communication EngineeringDocument3 pages5.principles of Communication Engineeringnimesheng111111111No ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Anonymous TxPyX8cNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Mahendranath RamakrishnanNo ratings yet

- Vlsi Internal Question Paper Mtech.Document5 pagesVlsi Internal Question Paper Mtech.Vinay ReddyNo ratings yet

- (WWW - Entrance-Exam - Net) - Sathyabama University-B.E in Aeronautical Engineering-5th Sem Aerodynamics - II Sample Paper 5Document2 pages(WWW - Entrance-Exam - Net) - Sathyabama University-B.E in Aeronautical Engineering-5th Sem Aerodynamics - II Sample Paper 5Mohamed ArifNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)1balamanianNo ratings yet

- 18-M.Tech (VLSI Design and Embedded System) PDFDocument31 pages18-M.Tech (VLSI Design and Embedded System) PDFAhilan AppathuraiNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Mahendranath RamakrishnanNo ratings yet

- VLSI Lab CompendiumDocument52 pagesVLSI Lab CompendiumSaad Ali Khan SherwaniNo ratings yet

- Full Custom Mask Layout DesignDocument15 pagesFull Custom Mask Layout DesignBharathNo ratings yet

- WWW - Entrance Exam - Net Sathyabama University Aeronautical Engineering 7th Sem Industrial Aerodynamics Sample Paper 1Document2 pagesWWW - Entrance Exam - Net Sathyabama University Aeronautical Engineering 7th Sem Industrial Aerodynamics Sample Paper 1Natesan MahendranNo ratings yet

- Part A: (Answer All The Questions) (7 2 14)Document1 pagePart A: (Answer All The Questions) (7 2 14)Selvanathan RathinamNo ratings yet

- Karunya University: M.B.A. Trimester Examination - April/May 2010Document1 pageKarunya University: M.B.A. Trimester Examination - April/May 2010daksh shuklaNo ratings yet

- Lab3 PDFDocument34 pagesLab3 PDFVõ Bá Quang Duy100% (1)

- Arunai College of Engineering: Velu Nagar, Mathur, TiruvannamalaiDocument4 pagesArunai College of Engineering: Velu Nagar, Mathur, TiruvannamalaisathishNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)johnarulrajNo ratings yet

- A Seminar Report On: Seminar Guide: Submitted byDocument21 pagesA Seminar Report On: Seminar Guide: Submitted bySravan VannadiNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumberneelagandanNo ratings yet

- COMSATS University Islamabad: Sahiwal Campus (Department of Computer Science)Document3 pagesCOMSATS University Islamabad: Sahiwal Campus (Department of Computer Science)Binte ZahraNo ratings yet

- Cmos LayoutDocument13 pagesCmos LayoutshastryNo ratings yet

- Terminal Test ISO FormatDocument1 pageTerminal Test ISO FormatnagarajSankarNo ratings yet

- Vlsi Tut-3Document1 pageVlsi Tut-3Bhavana H NNo ratings yet

- MicroelectronicsDocument39 pagesMicroelectronicsArun Av0% (1)

- LP 4Document5 pagesLP 4etasureshNo ratings yet

- Government College University, Faisalabad: Model PaperDocument1 pageGovernment College University, Faisalabad: Model PapernaeemakhtaracmaNo ratings yet

- Course Plan VLSI Design July 2013Document4 pagesCourse Plan VLSI Design July 2013HacraloNo ratings yet

- DSP Expt - DT Sinusoidals and Sampling - 2020Document3 pagesDSP Expt - DT Sinusoidals and Sampling - 2020Noh NaimNo ratings yet

- Vignan'S Institute of Technology & Aeronautical EngineeringDocument1 pageVignan'S Institute of Technology & Aeronautical EngineeringSsgn SrinivasaraoNo ratings yet

- Rtu Front PageDocument3 pagesRtu Front PageCreative CapturesNo ratings yet

- American International University-Bangladesh: Analog Electronics LabDocument10 pagesAmerican International University-Bangladesh: Analog Electronics LabRashedul IslamNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register Number1balamanianNo ratings yet

- Dr. Paul's Engineering College CIA Test - 1Document2 pagesDr. Paul's Engineering College CIA Test - 1Kalaimani ThirugnanamNo ratings yet

- Wireless Comm ProjectDocument3 pagesWireless Comm ProjectZuru Raya EthioNo ratings yet

- CS Syllabus 2012 Admissions OnwardsDocument78 pagesCS Syllabus 2012 Admissions OnwardsAnurag DeterminedNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document3 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Anushya RavikumarNo ratings yet

- (Oxford Series in Electrical and Computer Engineering) Allen, Phillip E. - Holberg, Douglas R-CMOS Analog Circuit Design-Oxford University Press, USA (2011)Document783 pages(Oxford Series in Electrical and Computer Engineering) Allen, Phillip E. - Holberg, Douglas R-CMOS Analog Circuit Design-Oxford University Press, USA (2011)ASDFER100% (1)

- M.E VlsiDocument25 pagesM.E VlsiDurai SelvanNo ratings yet

- Seminar On CmosDocument8 pagesSeminar On CmosRoberto HoodNo ratings yet

- Number LineDocument10 pagesNumber Lineshawn1loweNo ratings yet

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsFrom EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikNo ratings yet

- Wireless Lans and Ieee 802.11 Mac: Cse 6590 Winter 2012Document59 pagesWireless Lans and Ieee 802.11 Mac: Cse 6590 Winter 2012nksarathyNo ratings yet

- SPDP Scheme Document - SC ST StudentsDocument2 pagesSPDP Scheme Document - SC ST StudentsnksarathyNo ratings yet

- Introduction and Overview: - Course ContentDocument20 pagesIntroduction and Overview: - Course ContentnksarathyNo ratings yet

- Sathyabama University: Register NumberDocument2 pagesSathyabama University: Register NumbernksarathyNo ratings yet