Professional Documents

Culture Documents

Comparison Sheet Between W5100 and W5300 V1 (1) .1 Eng

Comparison Sheet Between W5100 and W5300 V1 (1) .1 Eng

Uploaded by

sunny007_mOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Comparison Sheet Between W5100 and W5300 V1 (1) .1 Eng

Comparison Sheet Between W5100 and W5300 V1 (1) .1 Eng

Uploaded by

sunny007_mCopyright:

Available Formats

Comparison Sheet between W5100 and W5300

Comparison Sheet

Between W5100 and W5300

Version 1.1

2008 WIZnet Co., Inc. All Rights Reserved.

For more information, visit our website at http://www.wiznet.co.kr

Copyright 2008 WIZnet Co., Inc. All rights reserved.

Comparison Sheet between W5100 and W5300

Document History Information

Version

Date

Descriptions

Ver. 0.9

Mar. 11, 2008

Release with W5300 launching

Ver. 1.0

May, 15, 2008

Replace W5300 image on front page.

Modify the phase Register >> Expansion, Refer to P.4

Modify the <Note 1> description

Add Sn_DPORTR description to the phase Register >>

Expansion, Refer to P.4.

Add <Note 2>

V1.1

Mar. 8, 2010

Delete item related with Interrupt assert time register

Copyright 2008 WIZnet Co., Inc. All rights reserved.

Comparison Sheet between W5100 and W5300

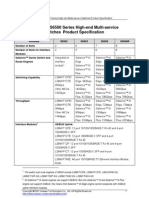

W5100 vs W5300

As W5300 is based on TCP/IP Core of W5100, it follows basic functions of W5100. One of the

main differences between W5100 and W5300 is the data bus. W5100 supports 8bit data bus,

but W5300 does not only 8 bit but also 16 bit data bus. With this data bus expansion, the

registers of W5300 are also based on 16 bit.

n

Host Interface

W5100

Address Bus

Data Bus

Interface Mode

Interrupt PIN(/INT)

W5300

15 PINs, ADDR[14:0]

10PINs, ADDR[9:0]

Only 8 Bit,

16/8 Bit, DATA[15:8]/DATA[7:0]

DATA[7:0]

Direct/Indirect, SPI

Direct/Indirect

No configuration of next assert

Configurable next assert time 2

time

Buffer Ready PIN

None

Monitoring the buffer Depth of

(BRDY[3:0])

selected SOCKET.

<Note> 1. By setting MR of W5300, the Fetch Timing of Host-Write-Data or Hold Timing of

Host-Read-Data can be configurable.

Network Interface

W5100

Link LED(LINKLED)

External MII

W5300

Blink

No Blink (Hold Low)

No

MII_TXEN, MII_TXD[3:0], MII_TXC, MII_CRS,

MII_COL, MII_RXDV, MII_RXD[3:0]

<Note> 1. MII_TXEN and MII_TXD[3:0] are Alternate Function PINs to be used for Network

Indicator LED signal. This PINs are used for MII signals according to TEST_MODE[3:0] PIN

Configuration. As W5300 supports MII signals, the PHY chips from 3rd party can be interfaced

instead of using the PHY embedded in W5300.

Register

The registers of W5300 are almost same as W5100. The differences in register usage are as

Copyright 2008 WIZnet Co., Inc. All rights reserved.

Comparison Sheet between W5100 and W5300

below.

Expansion

W5100

MR

1 Byte

W5300

2 Bytes

Host I/F Timing and FIFO swap are added

TMSR

1 Byte (2bit per SOCKET)

2 Bytes X 4 (1 Byte per SOCKET)

RMSR

1 Byte (2 bit per SOCKET)

2 Bytes X 4 (1 Byte per SOCKET)

Sn_MR

1 Byte

2 Bytes

TCP Alignment Bit is added

Sn_TX_FSR

2 Bytes

Sn_RX_RSR

2 Bytes

PSIDR

Use S0_DPORTR

PDHAR 1

4 Bytes

4 Bytes

2

Use S0_DHAR

S0_DPORTR 2 & PSIDR

S0_DHAR & PHAR

<Note> 1. Session ID and PPPoE server hardware address are used for PPPoE mode.

At the W5100, Session ID and PPPoE server hardware address can be gotten

or set through S0_DPORTR and S0_DHAR which are supported both Host-Read

and Host-Write. But at the W5300, Session ID and PPPoE server hardware

address can be gotten only through PSIDR and PDHAR, and can be set

through S0_DPORTR and Sn_DHAR such as W5100.

2. At the W5100, Sn_DPORTR supports both Host-Read and Host-Write. But, At

the W5300, Sn_DPORTR supports only Host-Write.

Addition

MTYPER

Set the Internal memory block Type(TX/RX)

FMTUR

Process the ICMP(Fragment MTU) Packet

Pn_BRDYR

Set the BRDYn PIN

Pn_DPTHR

SOCKET n Buffer Depth Monitoring

IDR

Sn_IMR

W5300 Identification

SOCKET n Interrupt MASK

Sn_KPALVTR

TCP Keep-Alive Timer

Sn_TX_WRSR

Write Size of TX memory

Sn_FRAGR

Configure the fragment field in IP Header

Sn_TX_FIFOR

The only access to TX memory

Sn_RX_FIFOR

The only access to RX memory

Copyright 2008 WIZnet Co., Inc. All rights reserved.

Comparison Sheet between W5100 and W5300

Removal

Sn_TX_RD

Only use in W5100.

Sn_TX_WR

Sn_RX_RD

Memory for data communication

W5100

Access

Size

Manipulation

W5300

Directly addressing

Only through Sn_TX_FIFOR/Sn_RX_FIFOR

Fixed Size. Total 16KBytes

Configurable 1. Total 128KBytes

TX : 8KBytes, RX : 8Kbytes

TX : 0~128KBytes, RX : 0~128KBytes

Calculate the Pointer Registers

No Calculation

(Sn_TX_RD,Sn_TX_WR,Sn_RX_RD)

No exist the pointer Register.

<Note> 1. The internal memory of W5300 is configurable for TX and RX buffer in the range of

128Kbyte by using TSMR, RMSR, and MTYPER. The TX/RX buffer size should be set

as the value, multiple of 8. According to the size, each bit of MTYPER is

configurable.

n

SOCKET

W5100

Count

W5300

TX memory

Allocable 1/2/4/8 KBytes

Allocable from 0 to 64Kbytes

RX memory

Allocable 1/2/4/8 KBytes

Allocable from 0 to 64Kbytes

<Note> 1. TX/RX memory of each socket can be set as the value ranged from 0Kbytes to

64Kbytes through TMSRn and RMSRn.

Data Transmit Size

W5100

Transmit Size

No need

W5300

Need to set transmit size to Sn_TX_WRSR

At the W5100, the host calculates and updates memory related Pointer Registers (Sn_TX_RD,

Sn_TX_WR), and access the memory in Byte unit. Therefore it is possible to get the

information of real TX data size by using Sn_TX_RD and Sn_TX_WR.

W5300 does not have those Pointer Register, and memory access can be done in Word(2 Bytes)

unit. Therefore, real TX data size should be set in the Sn_TX_WRSR.

Copyright 2008 WIZnet Co., Inc. All rights reserved.

Comparison Sheet between W5100 and W5300

Check Data Reception

W5100

Check RX

W5300

Interrupt(Sn_IR(RECV))

Interrupt(Sn_IR(RECV))

Received Size(Sn_RX_RSR)

Received Size(Sn_RX_RSR)

BRDYn PINs

<Note> 1. W5300 checks data reception in the same method of W5100. In addition, W5300

supports 4 BRDYn PINs to monitor the Buffer Depth of SOCKET n. BRDYn can select

SOCKET Num, Signal Polarity and Memory Type (TX/RX), and is assert when the

Buffer Depth of SOCKET n is same as or bigger than the value of Pn_BDPTHR. The

host could monitor the BRDYn PIN through I/O port or Interrupt PIN.

TCP

W5100

PACKET-INFO

W5300

No Header

PACKET-INFO addition when Sn_MR(ALIGN) = 0 1

Manually

Manually, Automatically

1 Byte Keep-alive data

0 byte Keep-alive data

(Header)

Keep-Alive

<Note> 1. As memory operation of W5100 is processed in Byte unit, the additional information

is not required for Received Data in TCP. However, the memory operation of W5300

is processed in Word(2 Bytes) unit, it is not possible to tell the difference between

odd and even number sized TCP data. When receiving the data, Host should analyze

the Packet-Info and process the data as big as receive size. If RX data size is in even

number, by setting the ALIGN bit of Sn_MR as 1, the PACKET-INFO does not need to

be added.

2. According to the setting value of Wn_KPALVTR, W5300 can transmit Keep Alive

Packet of 0 Byte Data size manually (Sn_KPALVTR=0x00 and SEND_KEEP command) or

automatically (Sn_KPALVTR > 0 and without command)

Copyright 2008 WIZnet Co., Inc. All rights reserved.

Comparison Sheet between W5100 and W5300

MACRAW

W5100

W5300

PACKET-INFO

Header Size information includes

The Size information of PACKET-

(Header)

not only Data size but also Header

INFO just includes Data size.

size, 2Bytes.

Received Data

Header(2Bytes) + Data

+ CRC(4bytes) 1

Format

PAUSE FRAME

PAKCET-INFO(2Bytes) + DATA packet

No support

When receiving PAUSE FRAME from

Switch

or

Router,

all

data

transmission is paused during Pause

Time.

<Note> 1. Whenever receiving MACRAW Data at the W5300, CRC(4bytes) data is added lastly.

Received CRC is the CRC value of Ethernet Frame, but not used practically. After

reading this CRC, the host should ignore it.

2. PAUSE FRAME is the mechanism for data Flow Control among Ethernet network

devices. Ethernet Flow Control occurs when the transmission speed of the sender

is faster than receiver. In this case, the receiver transmits the PAUSE FRAME to the

sender to hold the data transmission for the specified time.

Package

W5100

Package

64 LQFP

Copyright 2008 WIZnet Co., Inc. All rights reserved.

W5300

100 LQFP

You might also like

- Network with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationFrom EverandNetwork with Practical Labs Configuration: Step by Step configuration of Router and Switch configurationNo ratings yet

- AirWatch (v8.0) - MAG Install Guide For WindowsDocument44 pagesAirWatch (v8.0) - MAG Install Guide For WindowsTony YNo ratings yet

- Diagnostic Tools 5.2 For Audio CodeDocument67 pagesDiagnostic Tools 5.2 For Audio CodeBour BonNo ratings yet

- Basic Switch Configuration ProjectDocument3 pagesBasic Switch Configuration Projectapi-443394797No ratings yet

- WAVENCE18 Installation & Comm - RN88294 - C - 1800 - V1.0 - SG - Ed1 - CEDocument172 pagesWAVENCE18 Installation & Comm - RN88294 - C - 1800 - V1.0 - SG - Ed1 - CEDia nur100% (3)

- Firewall and Proxy ServersDocument26 pagesFirewall and Proxy ServersrajeevadeeviNo ratings yet

- Parameter Editor Manual V1.1Document10 pagesParameter Editor Manual V1.1MAQUINAX7No ratings yet

- High-Performance Internet Connectivity Solution - W5300 V1.2.5 EngDocument126 pagesHigh-Performance Internet Connectivity Solution - W5300 V1.2.5 Engsunny007_mNo ratings yet

- 02 210325 - Manual - Ezi-STEPII Plus-E Communication Function - ENGDocument132 pages02 210325 - Manual - Ezi-STEPII Plus-E Communication Function - ENGsanthoshs241sNo ratings yet

- WIZ811MJ Datasheet v1.2Document13 pagesWIZ811MJ Datasheet v1.2ummonkNo ratings yet

- Df550 Ultrasonic Level Sensor - Lorawan - ProtocolDocument11 pagesDf550 Ultrasonic Level Sensor - Lorawan - ProtocolIstar DMNo ratings yet

- AT Commands Examples: Examples For U-Blox GSM/GPRS ModulesDocument25 pagesAT Commands Examples: Examples For U-Blox GSM/GPRS ModulesTapish Parihar bluCursorNo ratings yet

- Wiz125sr User Manual en v1.0Document19 pagesWiz125sr User Manual en v1.0John Jairo Escudero F.No ratings yet

- Wiz108sr User Manual en v1.0Document30 pagesWiz108sr User Manual en v1.0alealmunaNo ratings yet

- High Reliability Series Eeproms I C Bus: BR24L - W SeriesDocument43 pagesHigh Reliability Series Eeproms I C Bus: BR24L - W Serieskeyboard2014No ratings yet

- 20190725-103344553 - VLAN MismatchDocument7 pages20190725-103344553 - VLAN MismatchPRATEEK MANWANINo ratings yet

- AS5403 CRC: Signature CalculationDocument13 pagesAS5403 CRC: Signature CalculationdurgakishoreNo ratings yet

- BLE Application Note SPP Over BLEDocument49 pagesBLE Application Note SPP Over BLEerfgrthjtrytrerfdNo ratings yet

- Meiligao GPRS Communication Protocol GT30i GT60 VT300 VT310 VT400 V2.4Document24 pagesMeiligao GPRS Communication Protocol GT30i GT60 VT300 VT310 VT400 V2.4pondokjitu100% (1)

- Wiz107sr User Manual en v1.0Document29 pagesWiz107sr User Manual en v1.0Pauli Correa ArriagadaNo ratings yet

- Wiz810mj Datasheet V 1.0Document16 pagesWiz810mj Datasheet V 1.0Deyvi Gutiérrez100% (1)

- SP12-18-48 Standard Protocol V3.2Document31 pagesSP12-18-48 Standard Protocol V3.2Ivan Alain Serrudo SeasNo ratings yet

- CMS16P53Document32 pagesCMS16P53kowinthawNo ratings yet

- Sle4418, Sle4428Document17 pagesSle4418, Sle4428Badrulshahputra BashaNo ratings yet

- 901 - Ceragon - QinQ CFG - PDF v1.5Document21 pages901 - Ceragon - QinQ CFG - PDF v1.5mehdi_mehdiNo ratings yet

- FS-8700-36 Weigh-Tronix: Driver ManualDocument8 pagesFS-8700-36 Weigh-Tronix: Driver ManualEric DunnNo ratings yet

- How To Program The Z80 Serial I/O (SIO) and CTC Document Version 2.1Document19 pagesHow To Program The Z80 Serial I/O (SIO) and CTC Document Version 2.1salvaesNo ratings yet

- Simatic S7-1200 Update To The S7-1200 System Manual, Edition 03/2014Document14 pagesSimatic S7-1200 Update To The S7-1200 System Manual, Edition 03/2014ali rifNo ratings yet

- A Simple Wired 802.1X Lab - PacketLife PDFDocument12 pagesA Simple Wired 802.1X Lab - PacketLife PDFLoc NguyenNo ratings yet

- An52478 001-52478Document15 pagesAn52478 001-52478Đặng Văn TàiNo ratings yet

- w5100s Ethernet Shield Ds V100eDocument9 pagesw5100s Ethernet Shield Ds V100eRanjit JahakarNo ratings yet

- S0100846 T7433 - DCDA System, Keppel FELS B289 Keppel Fels B289Document28 pagesS0100846 T7433 - DCDA System, Keppel FELS B289 Keppel Fels B289John LockNo ratings yet

- HDV100A2 1306CommandResponseDocument32 pagesHDV100A2 1306CommandResponserichar centenoNo ratings yet

- Meitrack ProtocolDocument23 pagesMeitrack ProtocolBriann BachNo ratings yet

- Web Home Automation Using Bluetooth Communication With 8051 MicrocontrollerDocument20 pagesWeb Home Automation Using Bluetooth Communication With 8051 Microcontrollerravi1432No ratings yet

- m2x3c I500c en M C Manual GBDocument88 pagesm2x3c I500c en M C Manual GBdinakaran2020No ratings yet

- Nortel Meridian 81C With AudioCodes Mediant 1000 & 2000 Using T1 QSIGDocument44 pagesNortel Meridian 81C With AudioCodes Mediant 1000 & 2000 Using T1 QSIGchand_basha_8No ratings yet

- Siemens S7 300 MPIDocument12 pagesSiemens S7 300 MPIbakri fattalNo ratings yet

- Virtual WireDocument13 pagesVirtual Wiresuperpuma86No ratings yet

- Dvi-300 S User's Guide (Doc0499) r01-001Document14 pagesDvi-300 S User's Guide (Doc0499) r01-001trungdungtb73100% (1)

- Cisco 2621 Gateway-PBX Interoperability: Ericsson MD-110 With T1 PRI SignalingDocument11 pagesCisco 2621 Gateway-PBX Interoperability: Ericsson MD-110 With T1 PRI Signalinginr0000zhaNo ratings yet

- Nuvoton 8051 ISP by COM Port: User ManualDocument18 pagesNuvoton 8051 ISP by COM Port: User ManualParth PatelNo ratings yet

- FS-8700-07 Bacnet Arcnet: Driver ManualDocument13 pagesFS-8700-07 Bacnet Arcnet: Driver ManualEric DunnNo ratings yet

- OpenVox WGW1002G User ManualDocument63 pagesOpenVox WGW1002G User Manualmaple4VOIPNo ratings yet

- Protocol Manual: VPL-FX50 RM-PJM50Document14 pagesProtocol Manual: VPL-FX50 RM-PJM50Hugh BarkerNo ratings yet

- Microcor Datalogger ML-9500A - Man Rev NCDocument13 pagesMicrocor Datalogger ML-9500A - Man Rev NCfelio ossoNo ratings yet

- SQUARELL rs232 Protocol Description 160127Document39 pagesSQUARELL rs232 Protocol Description 160127Gabriel KNo ratings yet

- DF702DF703 LoRaWAN Protocol V2.8Document15 pagesDF702DF703 LoRaWAN Protocol V2.8Istar DMNo ratings yet

- TSL230R Light-to-Frequency Converter (#27924) : General DescriptionDocument4 pagesTSL230R Light-to-Frequency Converter (#27924) : General DescriptionRamiNo ratings yet

- Edmi Mk3 Dnp3 Profile A0 - 2Document14 pagesEdmi Mk3 Dnp3 Profile A0 - 2asela115No ratings yet

- TI 20180317 String Inverters Communication Protocol V11 enDocument25 pagesTI 20180317 String Inverters Communication Protocol V11 encspj250mwNo ratings yet

- ZYXEL Application-Note PMG1005-T20B 1.0Document22 pagesZYXEL Application-Note PMG1005-T20B 1.0JasonNo ratings yet

- Data Exchanged Between Two SIMATIC S7-200 Devices in PPI ModeDocument5 pagesData Exchanged Between Two SIMATIC S7-200 Devices in PPI ModeagreenstoneNo ratings yet

- Vsat NSNDocument9 pagesVsat NSNafzalaamirNo ratings yet

- Ve - Direct Protocol FaqDocument7 pagesVe - Direct Protocol FaqlukaseksmurfNo ratings yet

- Configuration Documents For MFM Integration v2Document12 pagesConfiguration Documents For MFM Integration v2manishNo ratings yet

- AN12246Document27 pagesAN12246tom.tomqwe19801980No ratings yet

- Best Tuning Practices For Power Vault MD3600 Series Storage ArraysDocument8 pagesBest Tuning Practices For Power Vault MD3600 Series Storage ArraysAdam Van HarenNo ratings yet

- SafeXcel-IP-94-PLB SAS Appendix B v1.5Document7 pagesSafeXcel-IP-94-PLB SAS Appendix B v1.5neelamvamsiNo ratings yet

- Wiz-Rf40 Datasheet v1 0 enDocument14 pagesWiz-Rf40 Datasheet v1 0 enarikandiNo ratings yet

- Modbus Protocol Implementation NOJA-508Document15 pagesModbus Protocol Implementation NOJA-508JoseSanchez50% (2)

- Cisco CDR LoggingDocument6 pagesCisco CDR LoggingmasriffaNo ratings yet

- w5500 Ethernet ShieldDocument8 pagesw5500 Ethernet ShieldUlrich AdjeNo ratings yet

- Netgear WGT624v3 Router ManualDocument104 pagesNetgear WGT624v3 Router ManualJohnNo ratings yet

- Lab 5Document8 pagesLab 5Zakaria JubarnNo ratings yet

- Mitel 5212 IP Phone PDFDocument4 pagesMitel 5212 IP Phone PDFRichNo ratings yet

- Sicap - Administering - BIG IP - F5 TRG BIG OP ADMINDocument5 pagesSicap - Administering - BIG IP - F5 TRG BIG OP ADMINAlessandro PazNo ratings yet

- How To Connect One Router To Another To Expand A NetworkDocument20 pagesHow To Connect One Router To Another To Expand A NetworkDorinHurmuzNo ratings yet

- DS-2CD2765G1-IZS Datasheet V5.6.0 20220609Document5 pagesDS-2CD2765G1-IZS Datasheet V5.6.0 20220609Mohanad SulimanNo ratings yet

- Cognex PDFDocument59 pagesCognex PDFrguzmanabundisNo ratings yet

- DocumentDocument7 pagesDocumentAnkur YadavNo ratings yet

- E300g AP ManualDocument64 pagesE300g AP ManualnitaserbanscribdNo ratings yet

- FB BGP Community SignalingDocument14 pagesFB BGP Community SignalingLerner MapurungaNo ratings yet

- APP Iptv: Firewall Parental ControlDocument5 pagesAPP Iptv: Firewall Parental Controlhudan toyibanNo ratings yet

- Topology in Network DesignDocument5 pagesTopology in Network DesignakshayNo ratings yet

- Iot QuestionsDocument2 pagesIot QuestionsShardul DeolankarNo ratings yet

- Datasheet Forcepoint NGFW 300 Series enDocument4 pagesDatasheet Forcepoint NGFW 300 Series enfppcoelhoNo ratings yet

- Socks4 ProxiesDocument317 pagesSocks4 ProxiesanilpawarNo ratings yet

- 520H0011 4 Advanced CryptographyDocument37 pages520H0011 4 Advanced Cryptographybaochu832002No ratings yet

- Quectel EC25-E-FA Firmware Release Notes V0603Document7 pagesQuectel EC25-E-FA Firmware Release Notes V0603Proscend IndiaNo ratings yet

- NGFW Site-To-Site VPN Troubleshooting GuideDocument6 pagesNGFW Site-To-Site VPN Troubleshooting GuideBhavik2002No ratings yet

- Inmarsat Using Scoopy IP Over BGANDocument6 pagesInmarsat Using Scoopy IP Over BGANjose300No ratings yet

- ELEC5509 RevisionDocument5 pagesELEC5509 RevisionKaichi KohNo ratings yet

- Dual DHCP DNS Server: Installation and Configuration ManualDocument38 pagesDual DHCP DNS Server: Installation and Configuration Manualrqi11No ratings yet

- Config VRRP in Netscreen SSGDocument2 pagesConfig VRRP in Netscreen SSGZhuzhu ZhuNo ratings yet

- Qos SettingDocument21 pagesQos Settinglucky chandelNo ratings yet

- CR15i Quick Start GuideDocument12 pagesCR15i Quick Start GuideNavin KumarNo ratings yet

- Design and Implementation of Test IP Network Intelligent Monitoring System Based On SNMPDocument4 pagesDesign and Implementation of Test IP Network Intelligent Monitoring System Based On SNMPAldrey PhadmaNo ratings yet

- 300Mbps In-Wall Wireless Access PointDocument6 pages300Mbps In-Wall Wireless Access PointIrvin Yair Sabillón LópezNo ratings yet

- Subnetting-Supernetting 20051120Document59 pagesSubnetting-Supernetting 20051120JeandelaSagesseNo ratings yet