Professional Documents

Culture Documents

Benchmark Circuits

Benchmark Circuits

Uploaded by

adaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Benchmark Circuits

Benchmark Circuits

Uploaded by

adaCopyright:

Available Formats

124

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 1, JANUARY 2013

Built-In Generation of Functional Broadside Tests

Using a Fixed Hardware Structure

Irith Pomeranz, Fellow, IEEE

AbstractFunctional broadside tests are two-pattern scanbased tests that avoid overtesting by ensuring that a circuit traverses only reachable states during the functional clock cycles of a

test. In addition, the power dissipation during the fast functional

clock cycles of functional broadside tests does not exceed that

possible during functional operation. On-chip test generation

has the added advantage that it reduces test data volume and

facilitates at-speed test application. This paper shows that on-chip

generation of functional broadside tests can be done using a simple

and fixed hardware structure, with a small number of parameters

that need to be tailored to a given circuit, and can achieve high

transition fault coverage for testable circuits. With the proposed

on-chip test generation method, the circuit is used for generating

reachable states during test application. This alleviates the need

to compute reachable states offline.

Index TermsBuilt-in test generation, functional broadside

tests, reachable states, transition faults.

I. INTRODUCTION

VERTESTING due to the application of two-pattern

scan-based tests was described in [1][3]. Overtesting

is related to the detection of delay faults under non-functional

operation conditions. One of the reasons for these non-functional operation conditions is the following. When an arbitrary

state is used as a scan-in state, a two-pattern test can take

the circuit through state-transitions that cannot occur during

functional operation. As a result, slow paths that cannot be

sensitized during functional operation may cause the circuit

to fail [1]. In addition, current demands that are higher than

those possible during functional operation may cause voltage

drops that will slow the circuit and cause it to fail [2], [3]. In

both cases, the circuit will operate correctly during functional

operation.

Functional broadside tests [4] ensure that the scan-in state is

a state that the circuit can enter during functional operation, or

a reachable state. As broadside tests [5], they operate the circuit

in functional mode for two clock cycles after an initial state is

scanned in. This results in the application of a two-pattern test.

Since the scan-in state is a reachable state, the two-pattern test

Manuscript received April 11, 2011; revised November 14, 2011; accepted

December 07, 2011. Date of publication January 02, 2012; date of current version December 19, 2012. This work was supported in part by Semiconductor

Research Corporation under Grant 2011-TJ-2135. This paper was presented in

part at the Proceedings of the Design Automation and Test in Europe Conference, Grenoble, France, March 2011.

The author is with the School of Electrical and Computer Engineering, Purdue

University, West Lafayette, IN 47907 USA (e-mail: pomeranz@ecn.purdue.

edu).

Digital Object Identifier 10.1109/TVLSI.2011.2179682

takes the circuit through state-transitions that are guaranteed to

be possible during functional operation. Delay faults that are

detected by the test can also affect functional operation, and the

current demands do not exceed those possible during functional

operation. This alleviates the type of overtesting described in

[1][3]. In addition, the power dissipation during fast functional

clock cycles of functional broadside tests does not exceed that

possible during functional operation.

Test generation procedures for functional and pseudo-functional scan-based tests were described in [4] and [6][13]. The

procedures generate test sets offline for application from an

external tester. Functional scan-based tests use only reachable

states as scan-in states. Pseudo-functional scan-based tests

use functional constraints to avoid unreachable states that are

captured by the constraints.

This work considers the on-chip (or built-in) generation of

functional broadside tests. On-chip test generation reduces

the test data volume and facilitates at-speed test application.

On-chip test generation methods for delay faults, such as the

ones described in [14] and [15], do not impose any constraints

on the states used as scan-in states. Experimental results indicate that an arbitrary state used as a scan-in state is unlikely to

be a reachable state [4]. The on-chip test generation method

from [16] applies pseudo-functional scan-based tests. Such

tests are not sufficient for avoiding unreachable states as scan-in

states. The on-chip test generation process described in this

work guarantees that only reachable states will be used.

It should be noted that the delay fault coverage achievable

using functional broadside tests is, in general, lower than that

achievable using arbitrary broadside tests as in [14], [15] or

pseudo-functional broadside tests as in [16]. This is due to the

fact that functional broadside tests avoid unreachable scan-in

states, which are allowed by the methods described in [14][16].

However, the tests that are needed for achieving this higher fault

coverage are also ones that can cause overtesting. They can also

dissipate more power than possible during functional operation.

Only functional broadside tests are considered in this work.

Under the proposed on-chip test generation method, the circuit is used for generating reachable states during test application. This alleviates the need to compute reachable states or

functional constraints by an offline process as in [4], [6][13]

and [16]. The underlying observation is related to one of the

methods used in [4] for offline test generation, and is the following.

If a primary input sequence is applied in functional mode

starting from a reachable state, all the states traversed under

are reachable states. Any one of these states can be used as the

initial state for the application of a functional broadside test.

1063-8210/$31.00 2012 IEEE

POMERANZ: BUILT-IN GENERATION OF FUNCTIONAL BROADSIDE TESTS

By generating on-chip and ensuring that it takes the circuit

through a varied set of reachable states, the on-chip test generation process is able to achieve high transition fault coverage

using functional broadside tests based on . It should be noted

that, for the detection of a set of faults , at most

different

reachable states are required. This number is typically only a

small fraction of the number of all the reachable states of the

circuit. Thus, the primary input sequence does not need to

take the circuit through all its reachable states, but only through

a sufficiently large number relative to

, in order to be effective for the detection of target faults.

The hardware used in this paper for generating the primary

input sequence

consists of a linear-feedback shift-register

(LFSR) as a random source [17], and of a small number of gates

(at most six gates are needed for every one of the benchmark circuits considered). The gates are used for modifying the random

sequence in order to avoid cases where the sequence takes the

circuit into the same or similar reachable states repeatedly. This

is referred to as repeated synchronization [18]. In addition, the

on-chip test generation hardware consists of a single gate that is

used for determining which tests based on will be applied to

the circuit. The result is a simple and fixed hardware structure,

which is tailored to a given circuit only through the following

parameters.

1) The number of LFSR bits.

2) The length of the primary input sequence .

3) The specific gates used for modifying the LFSR sequence

into the sequence .

4) The specific gate used for selecting the functional broadside tests that will be applied to the circuit based on .

5) Seeds for the LFSR in order to generate several primary

input sequences and several subsets of tests.

The on-chip test generation hardware is based on the one described in [19]. It differs from it in the following ways.

1) The logic that produces the primary input sequence is

designed in this paper to reduce the dependencies between

the values assigned to the primary inputs, considering the

following sources of dependency. In [19], for a circuit

with primary inputs and a parameter mod, the LFSR

used for producing has

bits. The left-most

bits are used for driving the primary inputs of the circuit,

and the mod right-most bits are used for modifying the

random sequence in order to avoid repeated synchronization. With this structure, all the primary input values are

modified using the same function of the mod right-most

bits of the LFSR. Thus, they are always modified together

and to the same values. In addition, some primary inputs

receive shifted values of the primary inputs immediately

preceding them.

The structure used in this paper reduces these dependencies between primary input values by using a

-bit

LFSR for a circuit with primary inputs, where is a parameter such that

. Every consecutive bits of the

LFSR are used for producing the value of a different primary input. At most mod of the bits dedicated to a primary

input are actually used for producing values for the input,

including the modification of the input values in order to

avoid repeated synchronization. Since the modification is

125

done using different bits for every primary input, the dependencies between primary input values are reduced. In

addition, the unused bits serve to reduce the dependencies between the values of different primary inputs further

by avoiding cases where a primary input receives shifted

values of the primary input immediately preceding it. With

reduced dependencies, the primary input sequence

is

more likely to take the circuit into a varied set of reachable states. As a result, a higher fault coverage is achieved

for several of the circuits considered in [19]. In addition,

other parts of the test generation hardware can be simplified compared with the design in [19], as discussed next.

2) Both [19] and this paper apply multiple primary input sequences in order to achieve the highest possible fault coverage. To select which tests will be applied to the circuit

based on every sequence, the approach of [19] uses a different gate for every sequence. Since the number of sequences in [19] is significant, a large multiplexer and a significant number of gates are needed for this purpose. The

approach in this paper fixes the gate used for test selection in advance, and ensures that all the primary input sequences used for the circuit fit with the preselected gate. In

this way, a single gate is needed for test selection regardless

of the number of sequences used, and there is no need for

a multiplexer to distinguish between different sequences.

3) The lengths of the primary input sequences is varied in [19]

in order to control the number of tests applied to the circuit.

In this paper, all the sequences have the same length. This

makes the test application process uniform across different

sequences.

The result is that the test generation hardware used in this

paper has a simple and fixed structure, and it is independent of

the number of sequences used. The sequences differ only in the

seed used for the LFSR. The seeds can be stored on-chip, or a

seed can be scanned in together with the initial state of the circuit

before the application of every primary input sequence.

The paper focuses on the generation of input test data, which

is unique to functional broadside tests. For the output test data

the paper assumes that an output compactor such as a multipleinput shift-register (MISR) [17] will be used.

When the circuit-under-test is embedded in a larger design,

its primary inputs may be driven by other logic blocks that

are part of the same design. In addition, the primary inputs of

the circuit-under-test include any external inputs of the design

that drive the circuit-under-test. The primary outputs of the circuit-under-test may drive other logic blocks, or they may be primary outputs of the complete design. For simplicity this paper

assumes that primary inputs can be assigned any combination of

values. Functional constraints on primary input sequences can

be accommodated in one of the following ways.

1) The logic used for producing the primary input sequence

can be extended to incorporate some functional constraints.

2) A separate logic block can be used for modifying so as

to satisfy functional constraints.

3) Placing the on-chip test generation hardware for a logic

block on the inputs of the logic blocks driving it can create

some of the functional constraints for the block without

requiring additional logic.

126

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 1, JANUARY 2013

This paper is organized as follows. Section II gives an

overview of the on-chip generation and application of functional

broadside tests. Section III describes the details. Section IV

presents experimental results demonstrating the achievable

fault coverage.

II. OVERVIEW

This section gives an overview of the proposed method for

on-chip generation of functional broadside tests.

The discussion in this paper assumes that the circuit is initialized into a known state before functional operation starts.

Initialization may be achieved by applying a synchronizing sequence as in [4], [6][8] and [10][12], by asserting a reset input

as in [9] and [13], or by a combination of both. The initial state

of the circuit is denoted by . The discussion also assumes that

functional operation consists of the application of primary input

sequences starting from state .

With

as the initial state for functional operation,

is a

reachable state. In addition, the set of reachable states consists

of every state such that there exists a primary input sequence

that takes the circuit from to . Since can be entered during

functional operation starting from

is a reachable state.

It is possible to obtain reachable states on-chip by placing

the circuit in state

and applying a primary input sequence

of length in functional mode. The

circuit can be brought into state by using a scan-in operation,

or by using its initializing sequence. Let

be the state that

the circuit reaches at time unit under , for

. We

have that

. In addition,

is a reachable state for

. Therefore, every state

can be used as the initial

state for a functional broadside test

, where

plays the role of a scan-in state. As in a broadside test,

and

are primary input vectors that are applied in two consecutive

functional clock cycles starting from

using a slow and a

fast clock, respectively.

In addition to producing reachable states, the primary input

sequence can also be used as a source for the primary input

vectors of functional broadside tests. In particular, every subsequence of length two of defines a functional broadside test

. By using

and

from

, it is possible to avoid the need for a different source for these

primary input vectors during on-chip test generation.

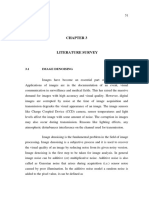

For illustration we consider ISCAS-89 benchmark

with initial state

. The circuit is shown in Fig. 1.

A primary input sequence for the circuit is shown in Table I.

For every time unit , Table I shows the state

and

the primary input vector

. Table I yields the functional broadside tests

.

The proposed on-chip generation method of functional broadside tests is based on placing the circuit in the initial state ,

applying a primary input sequence , and using several of the

functional broadside tests that can be extracted from in order

to detect target faults.

Next, we discuss how the application of

is affected

by the need to observe fault effects created by a test

.

Fig. 1.

TABLE I

PRIMARY INPUT SEQUENCE FOR

At time unit the circuit is in state

. Applying

and

in functional mode will result in the application of

.

A fault can be detected in one of the following two ways.

1) Based on the primary output vector

obtained in

response to

, if this vector is different from the

expected fault free primary output vector.

2) Based on the final state

of the test, if this state is

different from the expected fault free state.

In the context of built-in self-test,

and

need

to be captured by an output response compactor such as a MISR

[17]. In the case of

, the state needs to be shifted into the

output response compactor over a number of clock cycles equal

to the length of the longest scan chain. The circuit then needs to

be brought back to state

in order to continue the test

application process under .

Bringing the circuit back to state

can be done by

using circular shift of

[17]. As

is scanned out,

it can also be scanned in. If

is faulty, the output response

compactor will capture the fault effect, and observation of the

final signature will indicate that a fault is present. If

is fault free, the remaining tests based on will be applied as

required.

It should be noted that the tests starting in two consecutive

time units,

and

, are overlapping in the following

sense. Application of

takes the circuit through states

and

. Application of

takes

the circuit through states

, and

.

The application of both

and

requires special

hardware to bring the circuit back to state

after

is

POMERANZ: BUILT-IN GENERATION OF FUNCTIONAL BROADSIDE TESTS

TABLE II

PARAMETERS

applied. To avoid the need for this hardware, the proposed test

generation hardware applies subsets of non-overlapping tests

of the form

, where

for

.

III. ON-CHIP GENERATION OF FUNCTIONAL BROADSIDE TESTS

This section describes the on-chip generation method for

functional broadside tests based on the concepts discussed in

Section II. Section III-A describes the generation of the sequence . Section III-B describes the selection of tests that will

be applied based on . Section III-C describes the selection

of seeds for the generation of several different primary input

sequences and the application of several different subsets of

tests. Section III-D describes the selection of parameter values

in order to match the on-chip test generation hardware to a

given circuit. The parameters of the on-chip test generation

hardware are summarized in Table II for ease of reference.

A. Primary Input Sequence

The simplest way to generate a primary input sequence

on-chip is to use a random source such as an LFSR. However, a

random sequence may bring the circuit from the initial state

into a limited set of reachable states. This can be explained by

the effect observed in [18] and referred to as repeated synchronization. According to [18], a primary input cube synchronizes

a subset of state variables

if the following conditions are

satisfied. Let be applied to the primary inputs when the circuit

is in the all-unspecified present-state. Suppose that this results

in a next-state . The state variables whose values are specified

in are included in

.

In the example of

shown in Fig. 1, the primary input cube

applied in present-state

results

in the next-state

, synchronizing state variable

. In addition, the primary input cube

applied in present-state

results in the next-state

, synchronizing state variable .

A primary input cube with a small number of specified

values is likely to appear repeatedly in a random primary input

sequence . When this happens, the state variables in

assume the same values repeatedly under . This may prevent

the circuit from entering certain reachable states, and limit the

ability of the functional broadside tests extracted from to detect target faults. Repeated synchronization can also be caused

by a sequence of primary input cubes. However, the longer the

sequence the less likely it is to appear in a random primary input

sequence. Therefore, only single cubes are considered in [18].

127

Considering single cubes, repeated synchronization was

avoided in [18] by using a software procedure. With a high

probability, the procedure avoids primary input cubes that

would cause repeated synchronization. It allows them to appear with a small probability in order not to preclude certain

values from ever appearing on the state variables. Here, we

need a similar process that will be implemented using on-chip

hardware. To design such hardware, a software procedure is

first used for computing primary input cubes that synchronize

one or more state variables. The procedure focuses on primary

input cubes with single specified values since such cubes are

the most likely to appear repeatedly in a random primary input

sequence. For a circuit with primary inputs,

,

the procedure considers every primary input cube

where

primary input assumes the value and the other primary inputs are unspecified. For

, where

and

,

the procedure computes the set of synchronized state variables

. It then combines all the primary input cubes into a

single cube

that is useful for avoiding

repeated synchronization as follows.

1) If

, setting

causes fewer nextstate variables to be specified than setting

. The

procedure sets

.

2) If

, setting

causes fewer nextstate variables to be specified than setting

. The

procedure sets

.

3) If

, the procedure sets

.

In the example of

the procedure yields

, and

in all the other cases.

Therefore, it yields

. When this cube is applied to

the circuit in the all-unspecified state it leaves all the next-state

variables unspecified. Thus, it ensures that the circuit can

traverse all its reachable states.

It is possible to specify additional bits of in order to avoid

cubes with more than one specified value, or based on sequences

of cubes. A single specified bit of is sufficient in both of these

cases. For example, to avoid the sequence 0xxx x0xx xx0x it is

sufficient to set

or

or

.

The on-chip test generation hardware uses for the generation of

as follows. For a circuit

with primary inputs and for parameters and mod such that

, the hardware includes a

-bit LFSR. The LFSR

is clocked for cycles to produce a sequence of length .

At every time unit of the LFSR sequence, every consecutive bits of the LFSR are used for producing the value of one

primary input. Let the LFSR state at time unit be

. Let

the value of bit of the LFSR at time unit be

. The

value

of primary input

at time unit is produced

based on

. The value

of primary input

at time unit is produced based

on

. In general,

the value

of primary input at time unit is produced

based on

using the following rules.

1) If

. In this case, the value

of

is the random value

produced by the

LFSR. Bits

are

128

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 1, JANUARY 2013

TABLE III

LFSR SEQUENCE FOR

Fig. 2. On-chip generation of

unused, and they serve to reduce the dependencies between

the values of and those of

.

2) If

. By using the AND

function of mod LFSR bits,

with probability

. Thus, repeated synchronization of state variables due to

is avoided with this probability.

Bits

are unused, and they serve to reduce the dependencies

between the values of and those of

.

3) If

. By using the OR function of

mod LFSR bits,

with probability

.

Thus, repeated synchronization of state variables due to

is avoided with this probability. Bits

are unused, and they

serve to reduce the dependencies between the values of

and those of

.

With this implementation, the values of each primary input

are modified independently using a different set of mod LFSR

bits. This reduces the dependencies between the values of different primary inputs further.

For illustration, Fig. 2 shows the hardware used for

with

parameters

and

. For this circuit,

and

. The 12-bit LFSR is shown at the top of Fig. 2. Bits

0, 1 and 2 of the LFSR are used for producing the values of .

Since

, an OR gate is used for increasing the probability

that will be assigned the value 1. The OR gate is driven by bits

0 and 1 of the LFSR. Bit 2 of the LFSR reduces the dependencies

between the values of and the values of .

Bits 3, 4, and 5 of the LFSR are used for producing the values

of . For

. Therefore, is driven directly by bit 3

of the LFSR. Bits 4 and 5 reduce the dependencies between the

values of and the values of .

Bits 6, 7, and 8 are used for producing the values of . Since

, an AND gate is used for increasing the probability that

will be assigned the value 0. The AND gate is driven by bits 6

and 7. Bit 8 of the LFSR reduces the dependencies between the

values of and those of .

Finally, bits 9, 10, and 11 are used for producing the values

of . For

. Therefore, is driven directly by bit 9

of the LFSR.

In general, if there are primary inputs with

, the

implementation illustrated by Fig. 2 requires a

-bit LFSR,

and AND or OR gates with mod inputs.

The primary input sequence shown in Table I was produced

by the structure shown in Fig. 2 using the 12-bit primitive LFSR

from [20] with seed 101 011 100 100.

The states of the LFSR are shown in Table III.

B. Test Selection

This subsection describes the selection of the functional

broadside tests that will be applied based on a primary input

sequence . Let

be the set of target faults. In general, the

goal is to select a subset of time units

and apply a test set

, where

, such that the following

conditions are satisfied.

1) To ensure that the tests are non-overlapping,

for

.

2) It should be possible to produce the subset on-chip efficiently.

3) The test set

based on should detect as many of the

faults in as possible.

4)

should be as small as possible.

For simplicity, the proposed on-chip test generation hardware

satisfies the first two conditions as follows. A counter denoted

by

, where

,

counts from 0 to

to indicate the current time unit of .

For a parameter

, a test is applied when the last

bits

of CNT are 0, that is, when

. With

, the condition

implies

that only tests that start at even time units are applied. Thus,

. With

, the condition

implies that only tests that start at time units

divisible by four are applied. Thus,

. In general, the condition

implies that only tests that start at time units divisible by

are

applied. We denote

.

For a given value of , a single NOR gate is needed for producing the function

.

An example using

and

is shown in

Fig. 3. The counter CNT is shown at the top of the figure. When

is applied as a two-pattern test to the circuit.

Application of

includes output response compaction of the

primary output vector

under the second pattern, and

POMERANZ: BUILT-IN GENERATION OF FUNCTIONAL BROADSIDE TESTS

Fig. 3. On-chip test selection.

output response compaction of the final state

of the

test. The counter CNT is stopped during the scan-out operation

of the final state until state

is restored through circular

shift as discussed in Section II.

C. Selecting Seeds

The on-chip test generation hardware described so far has

parameters

and sel. These parameters determine the

primary input sequence , and the tests that will be applied

based on it. Keeping

and sel constant in order to keep

the hardware fixed, there is flexibility only in determining the

seed of the LFSR. Different seeds yield different primary input

sequences and different tests. Therefore, it is possible to increase

the fault coverage by using several different seeds.

To select seeds for a circuit it is possible to use an approach

similar to the one used for test data compression [21]. Using

a symbolic seed, it is possible to compute a primary input sequence and the subset of tests based on it, and then solve equations based on functional broadside tests that are known to detect target faults. The approach used in this paper avoids deterministic test generation to identify effective functional broadside tests by considering random seeds. A set of seeds is selected

using the following process.

Let be the set of target faults. For

, the process

selects a random seed denoted by

. It computes the primary input sequence

obtained with this seed. It also finds the

subset of tests

that will be applied based on . Both

and

are determined by the parameters

and sel.

In particular, is fixed by sel for all the values of . The process

performs fault simulation of under

and removes the detected faults from . If any faults are detected, it stores

in

a set denoted by SEED. It continues to consider additional seeds

until the last seeds do not improve the fault coverage, for a

constant .

Computation of seeds requires fault simulation with fault

dropping of under

tests for every seed. As additional

seeds are selected, the number of faults in is reduced, and the

fault simulation effort decreases.

Let the set of selected seeds be

, with corresponding sequences

and subsets of applied tests

. It is possible that all

the faults detected by

will also be detected by

. In this case,

does not need to be

129

used as part of the on-chip test generation process. The process

of seed selection identifies and removes such sequences as

follows.

During the selection of the seeds, if a fault

is detected

by a test from

, the process sets

. It also sets

for

. After all the seeds are selected, for

, the process checks whether all the faults

detected by

are also detected by subsets

such that

and

. This requires fault simulation of every

fault such that

under subsets

such that

and

. If all the faults with

are detected by

other subsets, the process updates the variable

for every

such fault to reflect another subset based on which is detected.

It also sets

. At the end, the process removes from

SEED every seed

for which

.

D. Selecting Parameters

The parameters of the on-chip test generation hardware,

and sel, are selected as follows.

The value of mod determines the probability of avoiding repeated synchronization by modifying a primary input vector

of based on the cube . Experimental results for benchmark circuits indicate that

or 4 is suitable for all the

circuits considered, and that decreasing or increasing mod beyond these values does not produce a higher fault coverage. We

use

when it is sufficient for matching or exceeding the

fault coverage reported in [19], and

when

is

not sufficient for this purpose. It was necessary to use

only for one circuit.

Increasing and can potentially increase the fault coverage.

Increasing increases the number of available tests, and increasing reduces the dependencies between the values of the

primary inputs. Increasing sel can potentially decrease the fault

coverage since it decreases the number of tests that will be applied to the circuit.

Considering the values suitable for different circuits and the

effects of increasing and decreasing these values, the values

found to be effective are

, or 8192,

or

, and

or 512. The value of determines the number of LFSR bits to

be

. This number is limited to be at most 300. The following

process is applied in order to select the values of these parameters for a given circuit.

Setting

and

, the process considers

and 16. For every value of such that

it selects seeds

as described in the previous subsection using

. It finds

a fault coverage denoted by

. Of all the values of

, it selects the lowest one that yields the highest fault coverage.

This is the value of selected for the circuit.

Next, the process considers

and 8192.

For every value of it considers

. For every

value of and sel it selects seeds as described in the previous

subsection using

. It finds a fault coverage denoted

by

. The process continues to increase sel for each

value of only as long as the fault coverage does not go down,

or until sel reaches its upper bound of 512.

Of the solutions obtained with

, the following ones

are reported.

130

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 1, JANUARY 2013

TABLE IV

ON-CHIP TEST GENERATION

1) If the fault coverage does not exceed that of [19] for any

solution, we report on the following solutions.

a) The solution with the highest fault coverage and the

lowest number of seeds.

b) The solution with the highest fault coverage and the

lowest number of applied tests.

2) If the fault coverage of at least one solution exceeds that of

[19], we report on the following solutions.

a) The solution with the highest fault coverage.

b) The solution with a fault coverage higher than that of

[19] and the lowest number of seeds.

c) The solution with a fault coverage higher than that of

[19] and the lowest number of applied tests.

One of these solutions is expected to be the most appropriate

for the circuit. In addition to these solutions there are others with

intermediate numbers of seeds and applied tests, which are not

reported.

IV. EXPERIMENTAL RESULTS

The circuits considered for the on-chip generation of functional broadside tests are ISCAS-89 and ITC-99 benchmarks

that are testable using functional tests. This excludes from

, and

, for

consideration circuits such as

which the fault coverage achievable by functional tests is very

low. Practical circuits are expected to be testable by functional

tests of the type considered here.

The initial state of the circuit is assumed to be the all-0 state.

Transition faults are used as the target fault model. For the LFSR

in the implementation of the on-chip test generation hardware,

a primitive LFSR from [20] is used.

The highest number of specified values in the cube used

for avoiding repeated synchronization in any circuit was six.

Thus, at most six mod-input gates are required for modifying

the primary input sequence as illustrated by Fig. 2.

The results are shown in Table IV as follows. The first row

for every circuit provides the results from [19] for comparison.

The next rows provide the results of the on-chip test generation

process described in this paper, corresponding to the solutions

with the highest fault coverage, the lowest number of seeds, and

the lowest number of applied tests, as discussed earlier. Each

row is organized as follows.

Columns

and sel show the values of the corresponding parameters.

POMERANZ: BUILT-IN GENERATION OF FUNCTIONAL BROADSIDE TESTS

Column seq shows the number of primary input sequences

(and the number of seeds) selected.

Column tests subcolumn app shows the number of tests applied based on the selected sequences, and subcolumn eff shows

the number of tests that improve the fault coverage when they

are applied. Some applied tests do not increase the fault coverage since the function apply does not exclude all the tests that

do not increase the fault coverage.

Column f.c. shows the transition fault coverage achieved by

the tests applied on-chip. For all of the circuits considered, the

on-chip generation of functional broadside tests achieves a transition fault coverage that is the same as or higher than that reported in [13] using an offline test generation procedure.

Column gates shows the following numbers of gates.

1) For the approach from [19], the modification of the primary input sequence based on requires a two-input gate

for every specified bit of . In addition, each sequence requires a gate for selecting the tests that will be applied to

the circuit. The multiplexer required for selecting the appropriate gate for each sequence has one AND gate for every

sequence, and an OR gate to produce the output of the multiplexer. Overall, the number of gates is estimated as the

number of specified bits in plus the number of sequences.

2) For the approach described in this paper, the hardware

structure is illustrated by Figs. 2 and 3. The modification of

the primary input sequence based on requires a gate for

every specified bit of . In addition, a single gate is used

for selecting the tests that will be applied to the circuit. The

same gate is used for implementing the selection for all the

sequences, and no multiplexers are needed to select among

the different sequences. The number of gates is equal to the

number of specified bits in plus one.

Column LFSR shows the number of LFSR bits. In spite of the

larger size of the LFSR compared with the approach from [19],

the approach described in this paper has the advantage that it

reduces the need for random logic, and it already accommodates

the need to reduce dependencies between primary input values

in order to increase the fault coverage.

From Table IV it can be seen that, the simplified hardware and

the reduced dependencies between the values assigned to the

primary inputs, allows the on-chip test generation approach described in this paper to achieve a higher fault coverage than that

reported in [19] for several circuits. The fault coverage using the

proposed hardware structure is never lower than that reported in

[19].

The proposed hardware also provides the flexibility needed

to produce solutions with low numbers of different seeds or low

numbers of applied tests. The numbers of applied tests are typically higher than in [19] due to the simpler hardware structure.

However, even with higher numbers of applied tests, the numbers remain manageable.

It is also interesting to consider the fault coverage of the primary input sequences that can be applied under the proposed approach when they are used as functional test sequences, without

using scan. We used the on-chip test generation hardware for

generating functional test sequences targeting single stuck-at

faults, using the parameters

or 16, and

. The selection between

and 16 was made based on

131

TABLE V

FUNCTIONAL TEST SEQUENCES

the number of primary inputs. For a circuit with up to 10 primary inputs,

ensures that the LFSR is large enough to

produce effective test sequences. For a circuit with more than

10 primary inputs,

is sufficient.

The on-chip test generation hardware was simulated with several different seeds, until the last

sequences did not

improve the single stuck-at fault coverage.

The results are shown in Table V, as follows. Columns

and show the values of the corresponding parameters.

Column seq shows the number of primary input sequences (and

the number of seeds) selected. Column eff shows the maximum

length required for any applied sequence. If a sequence

of

length does not detect any additional faults after the first

primary input vectors are applied, its effective length is

.

The number under column eff is the maximum value of

considering all the selected primary input sequences. Column

f.c. shows the single stuck-at fault coverage. For comparison,

column determ shows the single stuck-at fault coverage that

is known to be achievable using offline deterministic test sequences. This fault coverage is not available for

since

the circuit is highly untestable using functional test sequences

and it is not considered by test generation procedures for

non-scan circuits.

From Table V it can be seen that, for several of the circuits

considered, the proposed approach produces functional test sequences that match the achievable offline single stuck-at fault

coverage. For other circuits, the fault coverage is significantly

lower than that achievable offline. It should be noted that the

proposed on-chip hardware achieves the highest known transition fault coverage using functional broadside tests, and that it

was not designed to produce functional test sequences. The difference between functional test sequences and functional broadside tests can be explained as follows.

Fault detection by the application of functional test sequences

requires that the circuit be brought into states where faults can

be activated. It also requires the propagation of fault effects to

the primary outputs. The first requirement exists for functional

broadside tests as well, and the primary input sequences produced by the on-chip test generation hardware are effective for

this purpose. However, the sequences may not include propagation sequences since this is not a requirement for functional

broadside tests. If propagation sequences are not included, the

fault coverage of the sequences, when considered as functional

test sequences, may be lower.

132

IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 1, JANUARY 2013

This points to the existence of a substantial difference between generating functional test sequence and generating functional broadside tests. Due to this difference, substantially different on-chip hardware may be required for the two applications.

V. CONCLUDING REMARKS

This paper described an on-chip test generation method for

functional broadside tests. The hardware was based on the application of primary input sequences starting from a known reachable state, thus using the circuit to produce additional reachable

states. Random primary input sequences were modified to avoid

repeated synchronization and thus yield varied sets of reachable

states. Two-pattern tests were obtained by using pairs of consecutive time units of the primary input sequences. The hardware

structure was simple and fixed, and it was tailored to a given

circuit only through the following parameters: 1) the length of

the LFSR used for producing a random primary input sequence;

2) the length of the primary input sequence; 3) the specific gates

used for modifying the random primary input sequence; 4) the

specific gate used for selecting applied tests; and 5) the seeds for

the LFSR. The on-chip generation of functional broadside tests

achieved high transition fault coverage for testable circuits.

REFERENCES

[1] J. Rearick, Too much delay fault coverage is a bad thing, in Proc. Int.

Test Conf., 2001, pp. 624633.

[2] J. Saxena, K. M. Butler, V. B. Jayaram, S. Kundu, N. V. Arvind, P.

Sreeprakash, and M. Hachinger, A case study of IR-drop in structured

at-speed testing, in Proc. Int. Test Conf., 2003, pp. 10981104.

[3] S. Sde-Paz and E. Salomon, Frequency and power correlation between

at-speed scan and functional tests, in Proc. Int. Test Conf., 2008, pp.

19, Paper 13.3.

[4] I. Pomeranz and S. M. Reddy, Generation of functional broadside tests

for transition faults, IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 25, no. 10, pp. 22072218, Oct. 2006.

[5] J. Savir and S. Patil, Broad-side delay test, IEEE Trans. Comput.Aided Design Integr. Circuits Syst., vol. 13, no. 8, pp. 10571064, Aug.

1994.

[6] I. Pomeranz, On the generation of scan-based test sets with reachable

states for testing under functional operation conditions, in Proc. Design Autom. Conf., 2004, pp. 928933.

[7] Y.-C. Lin, F. Lu, K. Yang, and K.-T. Cheng, Constraint extraction

for pseudo-functional scan-based delay testing, in Proc. Asia South

Pacific Design Autom. Conf., 2005, pp. 166171.

[8] Z. Zhang, S. M. Reddy, and I. Pomeranz, On generating pseudo-functional delay fault tests for scan designs, in Proc. Int. Symp. Defect

Fault Toler. VLSI Syst., 2005, pp. 398405.

[9] I. Polian and F. Fujiwara, Functional constraints vs. test compression

in scan-based delay testing, in Proc. Design, Autom. Test Euro. Conf.,

2006, pp. 16.

[10] M. Syal et al., A study of implication based pseudo functional testing,

in Proc. Int. Test Conf., 2006, pp. 110.

[11] A. Jas, Y.-S. Chan, and Y.-S. Chang, An approach to minimizing functional constraints, in Proc. Defect Fault Toler. VLSI Syst., 2006, pp.

215226.

[12] H. Lee, I. Pomeranz, and S. M. Reddy, On complete functional broadside tests for transition faults, IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., pp. 583587, 2008.

[13] I. Pomeranz and S. M. Reddy, On reset based functional broadside

tests, in Proc. Design Autom. Test Euro. Conf., 2010, pp. 14381443.

[14] H. Lee, I. Pomeranz, and S. M. Reddy, Scan BIST targeting transition

faults using a Markov source, in Proc. Int. Symp. Quality Electron.

Design, 2004, pp. 497502.

[15] V. Gherman, H.-J. Wunderlich, J. Schloeffel, and M. Garbers, Deterministic logic BIST for transition fault testing, in Proc. Euro. Test

Symp., 2006, pp. 123130.

[16] Y.-C. Lin, F. Lu, and K.-T. Cheng, Pseudofunctional testing, IEEE

Trans. Comput.-Aided Design Integr. Circuits Syst., pp. 15351546,

2006.

[17] M. Abramovici, M. A. Breuer, and A. D. Friedman, Digital Systems

Testing and Testable Design. Piscataway, NJ: IEEE Press, 1995.

[18] I. Pomeranz and S. M. Reddy, Primary input vectors to avoid in

random test sequences for synchronous sequential circuits, IEEE

Trans. Comput.-Aided Design Integr. Circuits Syst., pp. 193197,

2008.

[19] I. Pomeranz, Built-in generation of functional broadside tests, presented at the Design Autom. Test Euro. Conf., Grenoble, France, 2011.

[20] P. H. Bardell, W. H. McAnney, and J. Savir, Built-In Test for VLSI.

New York: Wiley, 1987.

[21] B. Konemann, LFSR-coded test patterns for scan designs, in Proc.

Euro. Test Conf., 1991, pp. 237242.

Irith Pomeranz (M89SM96F99) received the

B.Sc. degree (summa cum laude) in computer engineering and the D.Sc degree from the Department of

Electrical Engineering, TechnionIsrael Institute of

Technology, Haifa, Israel, in 1985 and 1989, respectively.

From 1989 to 1990, she was a Lecturer with the

Department of Computer Science, Technion. From

1990 to 2000, she was a faculty member with the

Department of Electrical and Computer Engineering,

University of Iowa. In 2000, she joined the School of

Electrical and Computer Engineering, Purdue University. Her research interests

include testing of VLSI circuits, design for testability, synthesis and design verification.

Dr. Pomeranz was a recipient of the NSF Young Investigator Award in 1993,

and of the University of Iowa Faculty Scholar Award in 1997. She is a Golden

Core Member of the IEEE Computer Society.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Digital Image Processing Tutorial Questions AnswersDocument38 pagesDigital Image Processing Tutorial Questions Answersanandbabugopathoti100% (1)

- ITM Integration With Omnibus Multi Tier Architecure v1Document40 pagesITM Integration With Omnibus Multi Tier Architecure v1titi2006No ratings yet

- Papers Publised-1Document7 pagesPapers Publised-1anandbabugopathotiNo ratings yet

- Papers Publised-3Document8 pagesPapers Publised-3anandbabugopathotiNo ratings yet

- Contrast EnhancementDocument39 pagesContrast EnhancementanandbabugopathotiNo ratings yet

- The Effect of Economic Literacy and Parents Socio Economic Status On Entrepreneurial Intention in Economic Education Student Universitas Negeri MakassarDocument3 pagesThe Effect of Economic Literacy and Parents Socio Economic Status On Entrepreneurial Intention in Economic Education Student Universitas Negeri MakassaranandbabugopathotiNo ratings yet

- Discrete Wavelet TransformDocument40 pagesDiscrete Wavelet TransformanandbabugopathotiNo ratings yet

- Sampling With Automatic Gain Control 4Document31 pagesSampling With Automatic Gain Control 4anandbabugopathotiNo ratings yet

- Exp - No: Study of Spectrum Analyzer Aim: Equipment RequiredDocument6 pagesExp - No: Study of Spectrum Analyzer Aim: Equipment RequiredanandbabugopathotiNo ratings yet

- Hall Ticket (Rank) Hall Ticket (Rank) Hall Ticket (Rank) Hall Ticket (Rank) Hall Ticket (Rank)Document3 pagesHall Ticket (Rank) Hall Ticket (Rank) Hall Ticket (Rank) Hall Ticket (Rank) Hall Ticket (Rank)anandbabugopathotiNo ratings yet

- UNIT-4 FinalDocument70 pagesUNIT-4 FinalanandbabugopathotiNo ratings yet

- Digital Signal Processing by ChitodeDocument588 pagesDigital Signal Processing by Chitodeanandbabugopathoti100% (3)

- Exp - No:05 Time Division Multiplexing & Demultiplexing (TDM&D) AimDocument5 pagesExp - No:05 Time Division Multiplexing & Demultiplexing (TDM&D) AimanandbabugopathotiNo ratings yet

- 3 PDFDocument38 pages3 PDFanandbabugopathotiNo ratings yet

- Performance Characteristics of Thread Safe CollectionDocument24 pagesPerformance Characteristics of Thread Safe CollectionAlexandre AlbizzatiNo ratings yet

- Unit 4 - Operating System - WWW - Rgpvnotes.inDocument23 pagesUnit 4 - Operating System - WWW - Rgpvnotes.inGirraj DohareNo ratings yet

- OS in One VideoDocument16 pagesOS in One VideoShayak KaranNo ratings yet

- Qthreads PDFDocument8 pagesQthreads PDFStefano NefastoNo ratings yet

- OOPJ MultiThreading NJB PDFDocument27 pagesOOPJ MultiThreading NJB PDFRaj ShahNo ratings yet

- OS Imp Questions PDFDocument25 pagesOS Imp Questions PDFStudents LpuNo ratings yet

- User ManualDocument37 pagesUser ManualShamen DubonNo ratings yet

- OpenACC 2.5Document118 pagesOpenACC 2.5yeongnjingwakNo ratings yet

- Concurrent ProcessesDocument52 pagesConcurrent ProcessesrvalethNo ratings yet

- CS9252Document2 pagesCS9252R Gandhimathi RajamaniNo ratings yet

- Lab3 SynchronizationDocument17 pagesLab3 SynchronizationHoàng Anh KhoaNo ratings yet

- 04 Quiz 1 - ARG - PlattechDocument2 pages04 Quiz 1 - ARG - PlattechRobert BasanNo ratings yet

- Sun Solaris OS: Glenn Barney Gb2174@columbia - EduDocument35 pagesSun Solaris OS: Glenn Barney Gb2174@columbia - EduhanhndNo ratings yet

- Assignment 1 Ece 633Document17 pagesAssignment 1 Ece 633dedey123No ratings yet

- Operating System Concepts 10Th 10Th Edition Abraham Silberschatz Online Ebook Texxtbook Full Chapter PDFDocument69 pagesOperating System Concepts 10Th 10Th Edition Abraham Silberschatz Online Ebook Texxtbook Full Chapter PDFjoseph.mikula975100% (8)

- SAP Collections ManagementDocument37 pagesSAP Collections ManagementLoreto Matus D.100% (1)

- Define OOP.: Unit I - Introduction To Oop and Fundamentals of JavaDocument27 pagesDefine OOP.: Unit I - Introduction To Oop and Fundamentals of JavaseethaNo ratings yet

- 27 New Features of .NET Framework 4.0Document12 pages27 New Features of .NET Framework 4.0Umisha ShahNo ratings yet

- Article 2.2Document9 pagesArticle 2.2Seitmagambetov AzizbekNo ratings yet

- Unit 3Document104 pagesUnit 3Vamsi KrishnaNo ratings yet

- CS205 Project NachOSDocument46 pagesCS205 Project NachOSHassan Tariq0% (1)

- RTS MID AnswersDocument11 pagesRTS MID AnswershafeezaNo ratings yet

- Fusion Tax Partner Integration Cookbook v2Document71 pagesFusion Tax Partner Integration Cookbook v2Peter DruckerNo ratings yet

- Realtime ROS2Document53 pagesRealtime ROS2schwarmcycNo ratings yet

- Asymmetric Dekker SynchronizationDocument52 pagesAsymmetric Dekker SynchronizationfirefoxextslurperNo ratings yet

- CM6 Combined 2013Document154 pagesCM6 Combined 2013مسعد مرزوقىNo ratings yet

- SRDF Solutions PDFDocument192 pagesSRDF Solutions PDFJimmy UkoboNo ratings yet

- Jimma University: Jimma Institute of Technology Faculty of ComputingDocument7 pagesJimma University: Jimma Institute of Technology Faculty of ComputingadmachewNo ratings yet

- Operating Systems Notes - Part1Document78 pagesOperating Systems Notes - Part1H full jjjfyNo ratings yet