Professional Documents

Culture Documents

CS704 1

CS704 1

Uploaded by

Mian Ejaz0 ratings0% found this document useful (0 votes)

19 views2 pagesjyijo7bol

Original Title

CS704_1

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentjyijo7bol

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

19 views2 pagesCS704 1

CS704 1

Uploaded by

Mian Ejazjyijo7bol

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 2

Virtual University of Pakistan

Spring 16

CS704 Advanced Computer Architecture-II

Due Date: 11th May, 2016

Assignment 1

Instructions to Solve Assignments

The purpose of assignments is to give you hands on practice. It is

expected that students will solve the assignments themselves.

Following rules will apply during the evaluation of assignment.

Cheating from any source will result in zero marks in the

assignment.

Any student found cheating in any two of the assignments

submitted will be awarded "F" grade in the course.

No assignment after due date will be accepted.

Virtual University of Pakistan

Spring 16

Question 1: Total Points (10)

In reg-mem architecture, clock cycle is 10 ns wide. It is proposed that

reg-reg architecture be used instead, that reduces the clock cycle by 2

ns. However, it requires an additional load instruction, in some cases!

Will the new processor be more efficient, if so under what

circumstances? Quantify your answer.

Question 2: Total Points (15)

Three enhancements with the following speedups are proposed for a

new architecture.

Speedup1 = 30

Speedup2 = 20

Speedup3 = 15

Only one enhancement is usable at a time.

a. If enhancement 1 and 2 are each usable for 25% of the time,

what fraction of the time must enhancement 3 be used to

achieve an overall speedup of 10?

b. Assume, for some benchmark, the fraction of use is 15% for each

of enhancement 1 and 2 and 70% for enhancement 3. We want

to maximize performance. If only one enhancement can be

implemented, which one should it be, to achieve the best overall

performance?

c. Assume the enhancement can be used 25%, 35%, and 10% of

the time for enhancement 1, 2, and 3, respectively. For what

fraction of the reduced execution time is no enhancement in

use?

Question 3: Total Points (10+15= 25)

Read the research paper titled TransARM: An Efficient Instruction Set

Architecture Emulator, and answer the following questions.

a. How TransARM works?

b. How TransARM deals with implementation issues like executable

and linking format resolution, architecture mapping and system

call emulation?

You might also like

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Jinny Choe Temp Mem CardDocument1 pageJinny Choe Temp Mem CardginauineNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Option StrategiesDocument13 pagesOption StrategiesArunangshu BhattacharjeeNo ratings yet

- Exercises To Develop Neck StrengthDocument14 pagesExercises To Develop Neck StrengthbluhartNo ratings yet

- AD302 - Tightening of BoltsDocument2 pagesAD302 - Tightening of BoltsdenismcnelisNo ratings yet

- Drug StudyDocument7 pagesDrug Studykakienz100% (7)

- Detailed Lesson Plan in English 5 First Quarter Week 2 - Day 2 I. ObjectivesDocument3 pagesDetailed Lesson Plan in English 5 First Quarter Week 2 - Day 2 I. ObjectivesElvz C. DionesNo ratings yet

- Manjushri Chanting The Names Lotsawahouse A5Document40 pagesManjushri Chanting The Names Lotsawahouse A5Jasni YangNo ratings yet

- Cokaliong Shipping vs. UCPBDocument3 pagesCokaliong Shipping vs. UCPBglorybelle01No ratings yet

- Ba English Poems Download NotesDocument17 pagesBa English Poems Download NotesMian Ejaz75% (12)

- G.R. No. 159926 January 20, 2014 Pinausukan Seafood House, Roxas Bouley Ard, Inc.Document65 pagesG.R. No. 159926 January 20, 2014 Pinausukan Seafood House, Roxas Bouley Ard, Inc.johnkyleNo ratings yet

- cs703 MidDocument11 pagescs703 MidMian EjazNo ratings yet

- HSSC-II Short Notes CH 4Document7 pagesHSSC-II Short Notes CH 4Mian EjazNo ratings yet

- Important Long QuestionsDocument1 pageImportant Long QuestionsMian EjazNo ratings yet

- New Daily BDC Report 02.09.2016Document2 pagesNew Daily BDC Report 02.09.2016Mian EjazNo ratings yet

- Name of Paper Marks Obtained Total Marks Status: CongratulationDocument1 pageName of Paper Marks Obtained Total Marks Status: CongratulationMian EjazNo ratings yet

- PPSC Lecturer of Computer Science Past Paper QuestionsDocument19 pagesPPSC Lecturer of Computer Science Past Paper QuestionsMian Ejaz0% (2)

- Questions: (Ii) Sun, Rain, Curving SkyDocument1 pageQuestions: (Ii) Sun, Rain, Curving SkyMian EjazNo ratings yet

- ASSISTANT Director Land RecordDocument32 pagesASSISTANT Director Land RecordMian EjazNo ratings yet

- Homework 4Document4 pagesHomework 4Mian EjazNo ratings yet

- Web Generated Bill: Lahore Electric Supply Company - Electricity Consumer Bill (Mdi)Document2 pagesWeb Generated Bill: Lahore Electric Supply Company - Electricity Consumer Bill (Mdi)Mian EjazNo ratings yet

- CS704 - Advanced Computer Architecture-II: Due DateDocument2 pagesCS704 - Advanced Computer Architecture-II: Due DateMian EjazNo ratings yet

- English Half BookDocument4 pagesEnglish Half BookMian EjazNo ratings yet

- 16 Support & Movement: NameDocument2 pages16 Support & Movement: NameMian EjazNo ratings yet

- Computer Systems Architecture: Thorsten Altenkirch and Liyang HuDocument20 pagesComputer Systems Architecture: Thorsten Altenkirch and Liyang HuMian EjazNo ratings yet

- Solution Assignment No 2Document8 pagesSolution Assignment No 2Mian EjazNo ratings yet

- Past Paper Chemistry 1st Year BISE Lahore 2013 Group 1Document6 pagesPast Paper Chemistry 1st Year BISE Lahore 2013 Group 1Mian EjazNo ratings yet

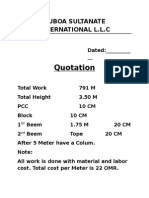

- Ruboa Sultanate International LDocument2 pagesRuboa Sultanate International LMian EjazNo ratings yet

- Inter Part One Physics Old PaperDocument72 pagesInter Part One Physics Old PaperMian EjazNo ratings yet

- Past Paper Chemistry 1st Year BISE Lahore 2012 Group 1Document5 pagesPast Paper Chemistry 1st Year BISE Lahore 2012 Group 1Mian EjazNo ratings yet

- Benefits and DetrimentsDocument16 pagesBenefits and DetrimentsAdolfo LasinNo ratings yet

- Main MenuDocument3 pagesMain MenueatlocalmenusNo ratings yet

- 4 KEE101T 201T Basic Electrical EnggDocument158 pages4 KEE101T 201T Basic Electrical EnggFinnyNo ratings yet

- OASYS GEO v17.8Document4 pagesOASYS GEO v17.8Koresh KhalpariNo ratings yet

- Horizons, Vol. 60, No. 3, Pp. 395-404.: Singh, Poonam, 6585450Document2 pagesHorizons, Vol. 60, No. 3, Pp. 395-404.: Singh, Poonam, 6585450Poonam SinghNo ratings yet

- Black Neon Green Neon Pink Trendy Illustrative Creative PresentationDocument15 pagesBlack Neon Green Neon Pink Trendy Illustrative Creative PresentationVagabond KatanaNo ratings yet

- PS182 - Terminal Report (1st Q)Document88 pagesPS182 - Terminal Report (1st Q)MarieBalangueNo ratings yet

- Facelift by Going Digital NowDocument3 pagesFacelift by Going Digital NowsitaNo ratings yet

- Subsequent Measurement Accounting Property Plant and EquipmentDocument60 pagesSubsequent Measurement Accounting Property Plant and EquipmentNatalie SerranoNo ratings yet

- AdmitCard PDFDocument2 pagesAdmitCard PDFSonu Kumar KumarNo ratings yet

- Recent Aspects On The Implementation of TQM in German EnterprisesDocument12 pagesRecent Aspects On The Implementation of TQM in German EnterprisesPratik KadamNo ratings yet

- Nepal Final PaperDocument18 pagesNepal Final Paperapi-340263670No ratings yet

- Wasde 1222Document40 pagesWasde 1222SamyakNo ratings yet

- Death and The CompassDocument12 pagesDeath and The CompassCrystal BerryNo ratings yet

- Moraga, Cherrie La GueraDocument5 pagesMoraga, Cherrie La GueranizaiaNo ratings yet

- MASON, K. (1986) The Status of Women - Conceptual and Methodological Issues in DemographicDocument18 pagesMASON, K. (1986) The Status of Women - Conceptual and Methodological Issues in DemographicValquiria AlmeidaNo ratings yet

- Rice Is NiceDocument3 pagesRice Is Niceammayi100No ratings yet

- Science Technology and Society MidtermsDocument16 pagesScience Technology and Society MidtermsDARYL JAMES MISANo ratings yet

- Earthquake-Induced Settlement: The Following Notation Is Used in This ChapterDocument27 pagesEarthquake-Induced Settlement: The Following Notation Is Used in This ChapternktanakaNo ratings yet

- Sociolinguistic Survey of Northern Pakistan Volume 4Document194 pagesSociolinguistic Survey of Northern Pakistan Volume 4bashoooo1No ratings yet

- Ca Celin Carretela Arrived Bringing Inside My Brother and Her WifeDocument2 pagesCa Celin Carretela Arrived Bringing Inside My Brother and Her WifeYjasmin AnneNo ratings yet