86% found this document useful (22 votes)

77K views27 pagesBooth's Algorithm - Multiplication & Division

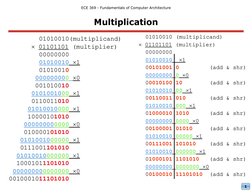

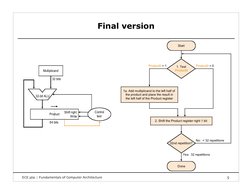

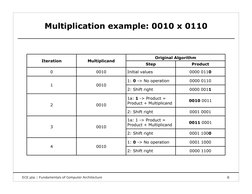

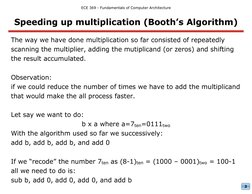

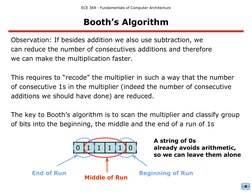

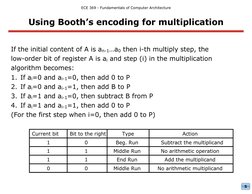

Multiplication is more complicated than addition and requires more steps and space. It is performed using a shifting and addition algorithm where the multiplicand is added to a running product and shifted at each step of the multiplication. There are more efficient techniques like Booth's encoding that can be used instead of the grade school algorithm. Negative numbers must first be converted before multiplying.

Uploaded by

naveenCopyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

86% found this document useful (22 votes)

77K views27 pagesBooth's Algorithm - Multiplication & Division

Multiplication is more complicated than addition and requires more steps and space. It is performed using a shifting and addition algorithm where the multiplicand is added to a running product and shifted at each step of the multiplication. There are more efficient techniques like Booth's encoding that can be used instead of the grade school algorithm. Negative numbers must first be converted before multiplying.

Uploaded by

naveenCopyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

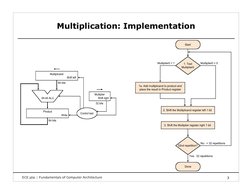

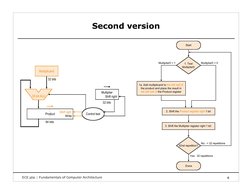

- Multiplication Methods

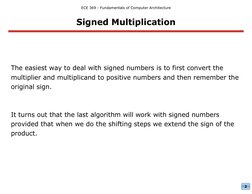

- Signed Multiplication

- Booth’s Algorithm

- Division Techniques

- Floating Point Arithmetic

- Summary of Chapter 3