67% found this document useful (3 votes)

13K views10 pagesComputer Architecture Question Bank

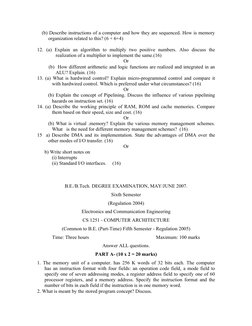

The document contains past university exam papers for Computer Architecture, including questions from exams in May/June 2009, November/December 2008, and April/May 2008. The papers follow a similar structure, with Part A consisting of 10 short answer questions worth 2 marks each, and Part B consisting of 5 longer answer questions worth 16 marks each. The questions cover topics such as system buses, memory types, binary arithmetic, pipelining, interrupts, I/O devices, and computer organization including functional units, addressing modes, control units, hazards, caches, and virtual memory.

Uploaded by

Malk MalikCopyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOC, PDF, TXT or read online on Scribd

67% found this document useful (3 votes)

13K views10 pagesComputer Architecture Question Bank

The document contains past university exam papers for Computer Architecture, including questions from exams in May/June 2009, November/December 2008, and April/May 2008. The papers follow a similar structure, with Part A consisting of 10 short answer questions worth 2 marks each, and Part B consisting of 5 longer answer questions worth 16 marks each. The questions cover topics such as system buses, memory types, binary arithmetic, pipelining, interrupts, I/O devices, and computer organization including functional units, addressing modes, control units, hazards, caches, and virtual memory.

Uploaded by

Malk MalikCopyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOC, PDF, TXT or read online on Scribd