Professional Documents

Culture Documents

TSE Tutorial

Uploaded by

hoanglongroyalCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TSE Tutorial

Uploaded by

hoanglongroyalCopyright:

Available Formats

Tutorial

Triple Speed Ethernet on Stratix III dev kit

I. System on SOPC builder

Hệ thống bao gồm các thành phần:

CPU (NIOS II Processor )

o Nios II/S

o Reset vector: ext_flash_1 offset: 0x1500000

o Exception vector: onchip_ram offset: 0x20

o Instruction Cache: 64Kbytes

onchip_ram (On-chip memory)

o 128 kbytes

flash_tristate_bridge (Avalon-MM Tristate Bridge):

o registered

o shared signals: select all.

ext_flash và ext_flash_1 (Flash memory interface CFI)

o 32 Mbytes: address width 24 data width 16

o Timing: settup 30 -wait 90 –hold 30 unit ns

sys_clk_timer (Interval timer)

o period 1ms

jtag_uart (JTAG UART)

led_pio (Parallel I/O)

o Width 8

o Output ports only

button_pio (Parallel I/O)

o Width 4

o Input ports only

o Synchronously capture: falling edge

o General IRQ: edge

quad_seven_seg_pio (Parallel I/O)

o Width 13

o Output ports only

sysid (System ID Peripheral)

altmemddr_bridge và altmemddr_1_bridge (Avalon-MM Clock Crossing

Bridge)

o Master-to-Slave FIFO depth 32

o Slave-to-Master FIFO depth 256

o Data width 32 –Slave/Master domain synchronizer length 3

Copyright© 2011 by Hieu Tran

altmemddr và altmemddr_1 (DDR2 SDRAM High Performance Controller)

o Speed grade 4

o PLL reference clock frequency 50/125 MHz

o Memory clock frequency 200MHz

o Memory preset: Micron MT47H64M8CB-3

sgdma_tx (Scatter-Gather DMA Controller)

o Transfer mode: Memory to Stream

o Data width 32 –Source error width1

sgdma_rx (Scatter-Gather DMA Controller)

o Transfer mode: Stream to Memory

o Data width 32 –Sink error width 6

tse_mac (Triple-Speed Ethernet)]

o Core variation: 10/100/1000Mb Ethernet MAC with 1000BASE-X/SGMII

PCS

o Use internal FIFO

o Use transceiver block : LVDS I/O

o MAC options: select all except for “Enable 64-bit statistics byte counters”

o Host clock divisor: 40

o PCS/SGMII options: Enable SGMII bridge

descriptor_memory (On-chip Memory)

o 8 kbytes

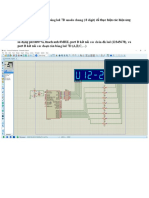

Hệ thống được kết nối như hình 1.

Recommend: tạo và connect trước khi tùy chỉnh thông số cho các component.

Chú ý địa chỉ BASE của các thành phần trong hệ thống phải nhỏ hơn 0x10000000

nếu không sẽ xuất hiện “warning: cpu: the address range of the slaves connected to the

NIOS II instruction master exceeds 28bits.”

Copyright© 2011 by Hieu Tran

Hình 1 System on SOPC builder

Copyright© 2011 by Hieu Tran

II. Modules in Quartus

1. Necessary modules Mega-plugin:

ddr_o.v (ALTDDIO_OUT)

Hình 2 ddr_o General

Copyright© 2011 by Hieu Tran

enet_tx_clk_pll (ALTPLL)

Hình 3.1 enet_tx_clk_pll General

Copyright© 2011 by Hieu Tran

Hình 3 2 enet_tx_clk_pll inputs/Lock

Hình 3 3 enet_tx_clk_pll output Clocks CLK C0

Copyright© 2011 by Hieu Tran

Hình 3 4 enet_tx_clk_pll output Clocks CLK C1

2. Module toplevel:

module stratixIII_3sl150_dev_niosII_standard(

// global signals

clkin_50,

clkin_125,

user_resetn,

// the_flash_tristate_bridge_avalon_slave

fsm_a,

fsm_d,

flash_oen,

flash_cen,

flash_wen,

flash_advn,

flash_resetn,

//altmemddr signals

ddr2_deva_dq,

ddr2_deva_dqs_p,

ddr2_deva_a,

ddr2_deva_ba,

Copyright© 2011 by Hieu Tran

ddr2_deva_casn,

ddr2_deva_cke,

ddr2_deva_ck_n,

ddr2_deva_ck_p,

ddr2_deva_csn,

ddr2_deva_dm,

ddr2_deva_rasn,

ddr2_deva_wen,

ddr2_deva_odt,

//altmemddr_1 signals

ddr2_devb_dq,

ddr2_devb_dqs_p,

ddr2_devb_a,

ddr2_devb_ba,

ddr2_devb_casn,

ddr2_devb_cke,

ddr2_devb_ck_n,

ddr2_devb_ck_p,

ddr2_devb_csn,

ddr2_devb_dm,

ddr2_devb_rasn,

ddr2_devb_wen,

ddr2_devb_odt,

// the quad seven segment display

seven_seg_sel,

seven_seg_a,

seven_seg_b,

seven_seg_c,

seven_seg_d,

seven_seg_e,

seven_seg_f,

seven_seg_g,

seven_seg_dp,

seven_seg_minus,

// the_button_pio

user_pb,

// the_led_pio

Copyright© 2011 by Hieu Tran

user_led,

// Ethernet

enet_led_link1000,

enet_resetn,

enet_tx_p,

enet_rx_p,

enet_mdio,

enet_mdc,

);

// Ethernet

input enet_led_link1000;

output enet_mdc;

inout enet_mdio;

output enet_resetn;

input enet_rx_p;

output enet_tx_p;

// Seven segment display

output [4: 1] seven_seg_sel;

output seven_seg_a;

output seven_seg_b;

output seven_seg_c;

output seven_seg_d;

output seven_seg_e;

output seven_seg_f;

output seven_seg_g;

output seven_seg_dp;

output seven_seg_minus;

//DDR2 SDRAM

output [ 12: 0] ddr2_deva_a;

output [ 1: 0] ddr2_deva_ba;

output ddr2_deva_casn;

output ddr2_deva_cke;

output ddr2_deva_odt;

inout ddr2_deva_ck_n;

inout ddr2_deva_ck_p;

output ddr2_deva_csn;

output ddr2_deva_dm;

Copyright© 2011 by Hieu Tran

inout [ 7: 0] ddr2_deva_dq;

inout ddr2_deva_dqs_p;

output ddr2_deva_rasn;

output ddr2_deva_wen;

output [ 12: 0] ddr2_devb_a;

output [ 1: 0] ddr2_devb_ba;

output ddr2_devb_casn;

output ddr2_devb_cke;

output ddr2_devb_odt;

inout ddr2_devb_ck_n;

inout ddr2_devb_ck_p;

output ddr2_devb_csn;

output ddr2_devb_dm;

inout [ 7: 0] ddr2_devb_dq;

inout ddr2_devb_dqs_p;

output ddr2_devb_rasn;

output ddr2_devb_wen;

//FLASH

output [ 24: 0] fsm_a;

inout [ 31: 0] fsm_d;

output flash_oen;

output flash_cen;

output flash_wen;

output flash_resetn;

output flash_advn;

input clkin_50;

input clkin_125;

input [ 3: 0] user_pb;

input user_resetn;

output [ 7: 0] user_led;

wire [ 25: 0] fsm_a_alignment;

wire flash_select_n;

wire flash_1_select_n;

wire [ 12: 0] seven_seg_data;

wire mdio_in;

wire mdio_out;

Copyright© 2011 by Hieu Tran

wire mdio_oen;

wire enet_gtx_clk;

wire enet_tx_clk_mac;

wire enet_tx_clk_phy;

assign seven_seg_a = seven_seg_data[0];

assign seven_seg_b = seven_seg_data[1];

assign seven_seg_c = seven_seg_data[2];

assign seven_seg_d = seven_seg_data[3];

assign seven_seg_e = seven_seg_data[4];

assign seven_seg_f = seven_seg_data[5];

assign seven_seg_g = seven_seg_data[6];

assign seven_seg_dp = seven_seg_data[7];

assign seven_seg_minus = seven_seg_data[8];

assign seven_seg_sel[1] = seven_seg_data[9];

assign seven_seg_sel[2] = seven_seg_data[10];

assign seven_seg_sel[3] = seven_seg_data[11];

assign seven_seg_sel[4] = seven_seg_data[12];

assign fsm_a[24:0] = fsm_a_alignment[25:1];

assign flash_resetn = user_resetn;

assign flash_advn = 1'b0;

assign flash_cen = flash_select_n & flash_1_select_n;

assign mdio_in = enet_mdio;

assign enet_mdio = (mdio_oen == 1'b0)? mdio_out : 1'bz;

ddr_o phy_ckgen

(

.datain_h(1'b1),

.datain_l(1'b0),

.outclock(enet_tx_clk_phy),

.dataout(enet_gtx_clk)

);

// Ethernet TX PLL (changed to 125 by dav0)

enet_tx_clk_pll enet_tx_clk_pll

(

.inclk0(clkin_125),

.c0(enet_tx_clk_mac),

.c1(enet_tx_clk_phy)

);

Copyright© 2011 by Hieu Tran

// Delayed reset for the Ethernet PHY ..

reg [19:0] counter;

always @(posedge clkin_50)

begin

if (user_resetn == 1'b0)

counter <= 20'b0;

else

if (counter[19] == 1'b0)

counter <= counter + 1;

else

counter <= counter;

end

assign enet_resetn = !counter[18];

stratixIII_3sl150_dev_niosII_standard_sopc

this_stratixIII_3sl150_dev_niosII_standard_sopc

// COPY *_INST.V

(

.mem_addr_from_the_altmemddr(ddr2_deva_a),

.mem_ba_from_the_altmemddr(ddr2_deva_ba),

.mem_cas_n_from_the_altmemddr(ddr2_deva_casn),

.mem_cke_from_the_altmemddr(ddr2_deva_cke),

.mem_clk_n_to_and_from_the_altmemddr(ddr2_deva_ck_n),

.mem_clk_to_and_from_the_altmemddr(ddr2_deva_ck_p),

.mem_cs_n_from_the_altmemddr(ddr2_deva_csn),

.mem_dm_from_the_altmemddr(ddr2_deva_dm),

.mem_dq_to_and_from_the_altmemddr(ddr2_deva_dq),

.mem_dqs_to_and_from_the_altmemddr(ddr2_deva_dqs_p),

.mem_ras_n_from_the_altmemddr(ddr2_deva_rasn),

.mem_we_n_from_the_altmemddr(ddr2_deva_wen),

.mem_odt_from_the_altmemddr(ddr2_deva_odt),

.global_reset_n_to_the_altmemddr(user_resetn),

.mem_addr_from_the_altmemddr_1(ddr2_devb_a),

.mem_ba_from_the_altmemddr_1(ddr2_devb_ba),

.mem_cas_n_from_the_altmemddr_1(ddr2_devb_casn),

.mem_cke_from_the_altmemddr_1(ddr2_devb_cke),

.mem_clk_n_to_and_from_the_altmemddr_1(ddr2_devb_ck_n),

.mem_clk_to_and_from_the_altmemddr_1(ddr2_devb_ck_p),

Copyright© 2011 by Hieu Tran

.mem_cs_n_from_the_altmemddr_1(ddr2_devb_csn),

.mem_dm_from_the_altmemddr_1(ddr2_devb_dm),

.mem_dq_to_and_from_the_altmemddr_1(ddr2_devb_dq),

.mem_dqs_to_and_from_the_altmemddr_1(ddr2_devb_dqs_p),

.mem_ras_n_from_the_altmemddr_1(ddr2_devb_rasn),

.mem_we_n_from_the_altmemddr_1(ddr2_devb_wen),

.mem_odt_from_the_altmemddr_1(ddr2_devb_odt),

.global_reset_n_to_the_altmemddr_1(user_resetn),

.out_port_from_the_led_pio(user_led),

.flash_tristate_bridge_readn(flash_oen),

.flash_tristate_bridge_address(fsm_a_alignment),

.flash_tristate_bridge_data(fsm_d),

.select_n_to_the_ext_flash(flash_select_n),

.select_n_to_the_ext_flash_1(flash_1_select_n),

.flash_tristate_bridge_writen(flash_wen),

.osc_clk(clkin_50),

.osc_clk_1(clkin_125),

.in_port_to_the_button_pio(user_pb),

.out_port_from_the_quad_seven_seg_pio(seven_seg_data),

.reset_n(user_resetn),

// the_tse_mac

.txp_from_the_tse_mac(enet_tx_p),

.rxp_to_the_tse_mac(enet_rx_p),

.ref_clk_to_the_tse_mac(enet_tx_clk_mac),

.mdc_from_the_tse_mac(enet_mdc),

.mdio_in_to_the_tse_mac(mdio_in),

.mdio_oen_from_the_tse_mac(mdio_oen),

.mdio_out_from_the_tse_mac(mdio_out),

);

ENDMODULE

3. Project Attached:

Sử dụng project xây dựng mẫu ./stratixIII_3sl150_dev_niosII_standard.qar

Copyright© 2011 by Hieu Tran

III. Software with NIOS II – Eclipse:

1. Create Project:

Sử dụng Eclipse tạo project

File/New/Nios II Application and BSP from template

Chọn project template : simple socket server.

Finish

2. Using InicheStack:

Tùy chỉnh BSP: click phải vào project/NIOS II/ BSP Editor…

Software Packages : đảm bảo check altera_iniche

Sử dụng DHCP hay không bằng cách check enable_dhcp_client

Nếu không dung DHCP, thiết lập IP tỉnh trong file:

simple_socket_server.h.

Copyright© 2011 by Hieu Tran

You might also like

- Chương trình thực hiện giao tiếp I2C giữa PIC 16F877A và IC DS1307 để cài đặt thời gianDocument9 pagesChương trình thực hiện giao tiếp I2C giữa PIC 16F877A và IC DS1307 để cài đặt thời gianhuuminhtsqttNo ratings yet

- BTL NhungDocument31 pagesBTL NhungLuong NguyenNo ratings yet

- Bai Tap LCDDocument19 pagesBai Tap LCDMinh TânnNo ratings yet

- Lab 5Document7 pagesLab 5Phát ThànhNo ratings yet

- 01 DK Led 7 ThanhDocument3 pages01 DK Led 7 ThanhQuốc BảoNo ratings yet

- THVDK B1Document10 pagesTHVDK B1Vinh HuaNo ratings yet

- Tài liệu thí nghiệm Vi xử lý 2017Document38 pagesTài liệu thí nghiệm Vi xử lý 2017Thành CôngNo ratings yet

- Hướng dẫn - hiển thị LCD dùng ccs cho người mới bắt đầu - Page 2 - Cộng đồng cơ điện tử Việt Nam - Mechatronics PDFDocument5 pagesHướng dẫn - hiển thị LCD dùng ccs cho người mới bắt đầu - Page 2 - Cộng đồng cơ điện tử Việt Nam - Mechatronics PDFDanh_IS4No ratings yet

- Mach Do Nhiet Do Ds18B20, Hien Thi LCD, Giao Tiep PCDocument37 pagesMach Do Nhiet Do Ds18B20, Hien Thi LCD, Giao Tiep PCNguyen DuongNo ratings yet

- Đề TàiDocument27 pagesĐề Tàihuycuong20033No ratings yet

- Giao tiếp 8051 với RFDocument10 pagesGiao tiếp 8051 với RFHuy TuongNo ratings yet

- ATHT Lab2 2021 2022Document24 pagesATHT Lab2 2021 2022Be BeNo ratings yet

- AbcDocument9 pagesAbcvoan nguyenNo ratings yet

- BTVN - LAB 3 - 24led - DonDocument8 pagesBTVN - LAB 3 - 24led - DonPhát ThànhNo ratings yet

- Luu Do Thuat ToanDocument8 pagesLuu Do Thuat ToanTrần Dương QuangNo ratings yet

- 20Nh14 ATTT Lab19 102200227Document37 pages20Nh14 ATTT Lab19 102200227Quân MaiNo ratings yet

- Chapter09 Driver NetworkCardDocument46 pagesChapter09 Driver NetworkCardÁnh NguyễnNo ratings yet

- Báo Cáo BTLDocument10 pagesBáo Cáo BTLNguyễn Thành Nam - B19DCVT269No ratings yet

- Tiểu nhóm số 20-20DTVT1-Báo cáo TH NMKT Arduino - 2Document5 pagesTiểu nhóm số 20-20DTVT1-Báo cáo TH NMKT Arduino - 2Vu Lam CaoNo ratings yet

- Tuần6 nút nhấnDocument14 pagesTuần6 nút nhấnnhoc kunNo ratings yet

- Hướng dẫn ôn tập môn VĐKDocument8 pagesHướng dẫn ôn tập môn VĐKHuynh Ngoc ThaoNo ratings yet

- Nguyen Thi Hang B20DCVT139Document11 pagesNguyen Thi Hang B20DCVT139Nguyễn Thị HằngNo ratings yet

- B1809564-ATHT Lab2 2021 2022Document6 pagesB1809564-ATHT Lab2 2021 2022khq2211No ratings yet

- Báo Cáo D Án IOTDocument15 pagesBáo Cáo D Án IOTanlthe181137No ratings yet

- AntidebugDocument26 pagesAntidebugLucia RinNo ratings yet

- Chức năng Sửa IP Mô tả Chức năng này cho phép sửa địa chỉ ip của thiết bịDocument25 pagesChức năng Sửa IP Mô tả Chức năng này cho phép sửa địa chỉ ip của thiết bịnguyenthiha08082002tbNo ratings yet

- Huong Dan Giao Tiep Matlab-ProteusDocument17 pagesHuong Dan Giao Tiep Matlab-Proteus0471 Nguyễn Quốc BảoNo ratings yet

- TIỂU LUẬN VI XỬ LÝDocument11 pagesTIỂU LUẬN VI XỬ LÝkimxoNo ratings yet

- Hack ProgramDocument5 pagesHack ProgramĐặng Quang HuyNo ratings yet

- Bài thực hành 03 - v2. Triển khai hệ thống phát hiện xâm nhập Snort (Gửi sinh viên)Document12 pagesBài thực hành 03 - v2. Triển khai hệ thống phát hiện xâm nhập Snort (Gửi sinh viên)Hòa ĐỗNo ratings yet

- Báo Cáo Đồ Án Vi Xử Lý: Tên đề tài: Thiết kế và điều khiển mô hình khóa số điện tửDocument31 pagesBáo Cáo Đồ Án Vi Xử Lý: Tên đề tài: Thiết kế và điều khiển mô hình khóa số điện tửĐăng HoàngNo ratings yet

- BAI8Document14 pagesBAI8Hoàng Vũ ĐứcNo ratings yet

- LCD, LMD35, Hien Thi Nhiet DoDocument8 pagesLCD, LMD35, Hien Thi Nhiet DoLEDUYLOC991No ratings yet

- Bài Giảng Bài 4 - LCD I2C Với STM32F407 Discovery - 1325325Document28 pagesBài Giảng Bài 4 - LCD I2C Với STM32F407 Discovery - 1325325Tinh LươngNo ratings yet

- ATHT Lab2 2023 2024 TuxaDocument6 pagesATHT Lab2 2023 2024 Tuxanguyennhutluan369No ratings yet

- TUT - Bộ Truyền (Transmitter) Theo Chuẩn UART - Diễn Đàn Thiết Kế Vi Mạch Và Vi Điện TửDocument15 pagesTUT - Bộ Truyền (Transmitter) Theo Chuẩn UART - Diễn Đàn Thiết Kế Vi Mạch Và Vi Điện TửTrọngHữuNguyễnNo ratings yet

- Baocao TTVDKDocument14 pagesBaocao TTVDKhongthuynguyenvloNo ratings yet

- TKSoC Buoi8 N8 ST5Document9 pagesTKSoC Buoi8 N8 ST5Thehoang PhanNo ratings yet

- Nút nhấn điều khiển dùng 12f629Document3 pagesNút nhấn điều khiển dùng 12f629teo tranNo ratings yet

- Nh19.99 NguyenVanThuong LabATTT12Document21 pagesNh19.99 NguyenVanThuong LabATTT12Thương NguyễnNo ratings yet

- Tranning Inf TF v1.0 VNDocument53 pagesTranning Inf TF v1.0 VNPhong BaNo ratings yet

- Bao Cao Ethernet ChandufoDocument17 pagesBao Cao Ethernet ChandufoPoint To PointNo ratings yet

- Kill Oracle Procedure LockedDocument7 pagesKill Oracle Procedure LockedDung Can DanceNo ratings yet

- Hướng Dẫn Lập Trình DMA Với STM32Document8 pagesHướng Dẫn Lập Trình DMA Với STM32Bui ThuyNo ratings yet

- Ứng dụng cơ bản 2Document42 pagesỨng dụng cơ bản 2Đoàn Văn MinhNo ratings yet

- EME-MC8 LabDocument59 pagesEME-MC8 LabBùi Công Huy CườngNo ratings yet

- BTL Vi Xu LyDocument25 pagesBTL Vi Xu Lycuongkhong2002No ratings yet

- Cài Đặt Snort ChuẩnDocument27 pagesCài Đặt Snort ChuẩnHưng NguyễnNo ratings yet

- lê minh hiếu- truyền thông uartDocument12 pageslê minh hiếu- truyền thông uartLê Minh HiếuNo ratings yet

- Thiet Ke Vi Mach Voi HDL Pham Quoc Cuong Reporthdl (Cuuduongthancong - Com)Document14 pagesThiet Ke Vi Mach Voi HDL Pham Quoc Cuong Reporthdl (Cuuduongthancong - Com)Hưng Nguyễn ThànhNo ratings yet

- Shell Coding 5Document35 pagesShell Coding 5lephuongdgNo ratings yet

- Hoc Tap Nghiep Vu Xử Lý Server FW7500, FW4570, Các Lệnh Của Server Sun, Win2003Document52 pagesHoc Tap Nghiep Vu Xử Lý Server FW7500, FW4570, Các Lệnh Của Server Sun, Win2003ăn uốngNo ratings yet

- Bai Tap DTTTDocument18 pagesBai Tap DTTTManucian TúNo ratings yet

- Thủ Thuật Router MikrotikDocument33 pagesThủ Thuật Router MikrotikMinh Nghia PhamNo ratings yet