Professional Documents

Culture Documents

8051 Ref

Uploaded by

Nam NguyenCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8051 Ref

Uploaded by

Nam NguyenCopyright:

Available Formats

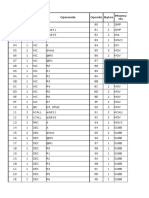

8051 Compact Assembly Reference

const16 const8 direct addr16 Opcode 11+a 24 26+i 25 28+n 34 36+i 35 38+n 01+a 54 56+i 55 58+n B0 82 53 52 B6+i B4 B5 B8+n E4 C2 C3 F4 B2 B3 D4 16+i 14 15 18+n 84 D5 D8+n 06+i 04 05 A3 08+n 20 10 40 73 30 50 70 60 12 02 76+i F6+i A6+i 74 E6+i E5 E8+n = = = = 16bit Code const 8bit Code const 8bit IData addr 16bit Code addr Operands Bytes CY CY CY CY CY CY CY CY addr11 rel bit i=0-1 Flags AC AC AC AC AC AC AC AC OV OV OV OV OV OV OV OV = 11bit Code absaddr = 8bit Code reladdr signed = 8bit IData bit addr n=0-7 a=32*(absaddr shr 8) Cycles P P P P P P P P P P P P CY CY 2 1 1 1 1 1 1 1 1 2 1 1 1 1 2 2 2 1 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 4 2 2 1 1 1 2 1 2 2 2 2 2 2 2 2 2 2 1 1 2 1 1 1 1 92 A2 75 86+i F5 85 88+n 90 78+n F8+n A8+n 93 83 F0 F2+i E0 E2+i A4 00 44 46+i 45 48+n A0 72 43 42 D0 C0 22 32 23 33 03 13 D2 D3 80 94 96+i 95 98+n C4 C6+i C5 C8+n D6+i 64 66+i 65 68+n 63 62 MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOV MOVC MOVC MOVX MOVX MOVX MOVX MUL NOP ORL ORL ORL ORL ORL ORL ORL ORL POP PUSH RET RETI RL RLC RR RRC SETB SETB SJMP SUBB SUBB SUBB SUBB SWAP XCH XCH XCH XCHD XRL XRL XRL XRL XRL XRL 3 2 1 0 PSW 7 6 5 4 CY AC F0 RS1 RS0 OV F1 P RS0 RS1: register bank selection; mem: 00 :00-07 01 :08-0f 10 :10-17 11 :18-1f bit, C C, bit direct, #const8 direct, @Ri direct, A direct, direct direct, Rn DPTR, #const16 Rn, #const8 Rn, A Rn, direct A, @A+DPTR A, @A+PC @DPTR, A @Ri, A A, @DPTR A, @Ri AB 2 2 3 2 2 3 2 3 2 1 2 1 1 1 1 1 1 1 1 A, #const8 2 A, @Ri 1 A, direct 2 A, Rn 1 C, /bit 2 C, bit 2 direct, #const8 3 direct, A 2 direct 2 direct 2 1 1 A 1 A 1 A 1 A 1 bit 2 C 1 rel 2 A, #const8 2 A, @Ri 1 A, direct 2 A, Rn 1 A 1 A, @Ri 1 A, direct 2 A, Rn 1 A, @Ri 1 A, #const8 2 A, @Ri 1 A, direct 2 A, Rn 1 direct, #const8 3 direct, A 2 2 1 2 2 1 2 2 2 1 1 2 2 2 2 2 2 2 4 1 1 1 1 1 2 2 2 1 2 2 2 2 1 1 1 1 1 1 2 1 1 1 1 1 1 1 1 1 1 1 1 1 2 1

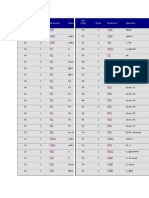

Mnemonic ACALL ADD ADD ADD ADD ADDC ADDC ADDC ADDC AJMP ANL ANL ANL ANL ANL ANL ANL ANL CJNE CJNE CJNE CJNE CLR CLR CLR CPL CPL CPL DA DEC DEC DEC DEC DIV DJNZ DJNZ INC INC INC INC INC JB JBC JC JMP JNB JNC JNZ JZ LCALL LJMP MOV MOV MOV MOV MOV MOV MOV

addr11 2 A, #const8 2 A, @Ri 1 A, direct 2 A, Rn 1 A, #const8 2 A, @Ri 1 A, direct 2 A, Rn 1 addr11 2 A, #const8 2 A, @Ri 1 A, direct 2 A, Rn 1 C, /bit 2 C, bit 2 direct, #const8 3 direct, A 2 @Ri, #const8, re3 A, #const8, rel 3 A, direct, rel 3 Rn, #const8, rel3 A 1 bit 2 C 1 A 1 bit 2 C 1 A 1 @Ri 1 A 1 direct 2 Rn 1 AB 1 direct, rel 3 Rn, rel 2 @Ri 1 A 1 direct 2 DPTR 1 Rn 1 bit, rel 3 bit, rel 3 rel 2 @A+DPTR 1 bit, rel 3 rel 2 rel 2 rel 2 addr16 3 addr16 3 @Ri, #const8 2 @Ri, A 1 @Ri, direct 2 A, #const8 2 A, @Ri 1 A, direct 2 A, Rn 1

CY

P P

CY

P P OV P P P P P

CY CY CY CY P CY P CY CY

CY CY

P P

CY CY CY CY CY CY CY AC AC AC AC OV OV OV OV

P P

CY

OV P

P P P P P P P P P P P P

P P P P

Memory organization

SFRs

You might also like

- Car Gear Indicator AbstractDocument5 pagesCar Gear Indicator Abstractapi-3818780No ratings yet

- M @-51 Instruction Set: Programmer'SDocument7 pagesM @-51 Instruction Set: Programmer'Swen_galsNo ratings yet

- Opcodes: Products Download Events Support VideosDocument3 pagesOpcodes: Products Download Events Support VideosSefu ThakurNo ratings yet

- Opcode of Microcontroller - 8051Document6 pagesOpcode of Microcontroller - 8051anandhkrNo ratings yet

- Opcodes PrabhaDocument2 pagesOpcodes PrabhaDhivya Ad A DNo ratings yet

- Hex Code Bytes and Mnemonics ChartDocument12 pagesHex Code Bytes and Mnemonics ChartAnbalagan GuruNo ratings yet

- Opcodes: The Following Table Lists The 8051 Instructions by HEX CodeDocument3 pagesOpcodes: The Following Table Lists The 8051 Instructions by HEX CodeVijay VermaNo ratings yet

- 8051 Microcontroller Instruction Set TableDocument4 pages8051 Microcontroller Instruction Set TableBalaji KannanNo ratings yet

- 8051 OpcodeDocument4 pages8051 OpcodeGokulakrishnan100% (1)

- TDA2030ADocument2 pagesTDA2030AChalitha KanchanaNo ratings yet

- 8051 Instruction SetDocument50 pages8051 Instruction Setkapil singhNo ratings yet

- Clevo 5X00SDocument29 pagesClevo 5X00SAndrew AyalaNo ratings yet

- CJ Instrucoes 8051Document6 pagesCJ Instrucoes 8051Luz Do Mundo PijamasNo ratings yet

- 8051 Instruction SetDocument2 pages8051 Instruction SetMaheswari VijayakumarNo ratings yet

- 8051 Instruction SetDocument6 pages8051 Instruction Setanamika_2k8No ratings yet

- Hex Bytes Mnemonic Code Chart for 8051 Microcontroller OperationsDocument8 pagesHex Bytes Mnemonic Code Chart for 8051 Microcontroller Operationsansari2erNo ratings yet

- Asembbly Operation & Sintax Program Arithmetic Operations Mnemonic Description Bytes CyclesDocument6 pagesAsembbly Operation & Sintax Program Arithmetic Operations Mnemonic Description Bytes CyclesArief HamidNo ratings yet

- RNC Role in NetworkDocument22 pagesRNC Role in NetworkAmit RanjanNo ratings yet

- Chuong Trinh Dung AT Mega 8535 Do Nhiet DoDocument6 pagesChuong Trinh Dung AT Mega 8535 Do Nhiet Doapi-26399985No ratings yet

- rqqhfwlrqvehwzhhq5) Dqg%%0Rgxohv: &&67Hfkqlfdo'Rfxphqwdwlrq 6Fkhpdwlfv/D/Rxwv') Ybd 1$0Document9 pagesrqqhfwlrqvehwzhhq5) Dqg%%0Rgxohv: &&67Hfkqlfdo'Rfxphqwdwlrq 6Fkhpdwlfv/D/Rxwv') Ybd 1$0anjirponselNo ratings yet

- Sony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICDocument36 pagesSony-Vaio-Mbx-126-Je5-Schematic-Mb-Mp SCHEMATICvideoson0% (1)

- MCD2601 Assessment 3Document7 pagesMCD2601 Assessment 3mpumeshongwe80No ratings yet

- DatasheetDocument13 pagesDatasheetbitanjungNo ratings yet

- Hex Code 8051Document6 pagesHex Code 8051blzz2netNo ratings yet

- 1Document1 page1Ulul AzmiNo ratings yet

- The Following Table Lists The 8051 Instructions by HEX CodeDocument5 pagesThe Following Table Lists The 8051 Instructions by HEX CodeBruce_Jass_3739No ratings yet

- Betaflight Config for XRACERF4Document20 pagesBetaflight Config for XRACERF4WernerNo ratings yet

- Sony Vaio Mbx-126 - Quanta Je5.1Document36 pagesSony Vaio Mbx-126 - Quanta Je5.1nunoq171No ratings yet

- ATmega8-L Microcontroller Circuit DiagramDocument3 pagesATmega8-L Microcontroller Circuit DiagramNguyễn Văn HinhNo ratings yet

- Density Based Traffic Light ControllingDocument39 pagesDensity Based Traffic Light Controllingsantosh426No ratings yet

- Addablock Diagram DPS24: Input 2-4 S Ame As Inp Ut 1Document1 pageAddablock Diagram DPS24: Input 2-4 S Ame As Inp Ut 1RWMaichNo ratings yet

- 8051 Instruction Set ReferenceDocument29 pages8051 Instruction Set ReferenceSmith Ccahuay HuamaniNo ratings yet

- Intel 8051 Instruction SetDocument55 pagesIntel 8051 Instruction SetRakesh GangwarNo ratings yet

- Conector Tipo B: Rxleda# TCK TDI TDO TMS NTRST RTCK RST DBGRQ Dbgack Acbus1Document2 pagesConector Tipo B: Rxleda# TCK TDI TDO TMS NTRST RTCK RST DBGRQ Dbgack Acbus1juenkkinNo ratings yet

- ATtiny24/44/84 Instruction Set SummaryDocument2 pagesATtiny24/44/84 Instruction Set SummaryRajsekhar NagNo ratings yet

- Beta95x 4.2.9Document20 pagesBeta95x 4.2.9Star interceptor FPVNo ratings yet

- Schematic Diagrams Appendix BDocument0 pagesSchematic Diagrams Appendix BfclodoaldoNo ratings yet

- combinepdfDocument14 pagescombinepdfDuoDrenchNo ratings yet

- Opcode Bytes Operands Opcode Bytes Mnemo Nic Mnemo NicDocument10 pagesOpcode Bytes Operands Opcode Bytes Mnemo Nic Mnemo NicJeba ChristoNo ratings yet

- CPU Board Logic Diagram System 6 PinballDocument0 pagesCPU Board Logic Diagram System 6 PinballMauricio RaúlNo ratings yet

- Schematic 13Document1 pageSchematic 13api-203437529No ratings yet

- KA2284Document2 pagesKA2284Adir FigueiredoNo ratings yet

- Ve Mach inDocument7 pagesVe Mach inBonten HitakeiNo ratings yet

- PLD Vars April2010Document27 pagesPLD Vars April2010scribd_pineda71No ratings yet

- Arduino EtArduino Ethernet Shield 06 Schematichernet Shield 06 SchematicDocument1 pageArduino EtArduino Ethernet Shield 06 Schematichernet Shield 06 SchematicJohn BurgerNo ratings yet

- Compact title for circuit diagram documentDocument3 pagesCompact title for circuit diagram documentAdrian PeterNo ratings yet

- Driver Bipolar 2 Amp PDFDocument5 pagesDriver Bipolar 2 Amp PDFEmiliano CuscuetaNo ratings yet

- ATmega16 ATmega32Document9 pagesATmega16 ATmega32binitdubeyNo ratings yet

- GBCrib Sheet 000129Document4 pagesGBCrib Sheet 000129mistershrubberNo ratings yet

- Top-Level Diagram: SHEET 13-18Document21 pagesTop-Level Diagram: SHEET 13-18Aref MGHNo ratings yet

- 8dev-0700 0002 SB SCHDocument3 pages8dev-0700 0002 SB SCHVitor AquinoNo ratings yet

- 6800 Instruction Set Address Modes and EffectsDocument5 pages6800 Instruction Set Address Modes and EffectsHayati AkdağNo ratings yet

- Electronic Circuit Design Ideas: Edn Series for Design EngineersFrom EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersRating: 5 out of 5 stars5/5 (2)

- 110 Semiconductor Projects for the Home ConstructorFrom Everand110 Semiconductor Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)