Professional Documents

Culture Documents

Am 2930

Uploaded by

SD_Ducksoup0 ratings0% found this document useful (0 votes)

40 views11 pagesDatasheet for Am2930 Program Control Unit for bitslice designs (AMD).

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentDatasheet for Am2930 Program Control Unit for bitslice designs (AMD).

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

40 views11 pagesAm 2930

Uploaded by

SD_DucksoupDatasheet for Am2930 Program Control Unit for bitslice designs (AMD).

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 11

Am2930

Program Control Unit

DISTINCTIVE CHARACTERISTICS

‘¢ Pownrul, it sie address entries for memorat

‘set with both main memory and mictoprogtam memory

Expandable ro goerate any adres length,

executes 32 instructions

‘Autometic generation of address and updete of program

counter for fetch eyes, branch cyets, and subroutine call

fd return

© Consins extendable fui acer

‘Twelve diferant relative odaeess instructions ae provided,

Including jump osubroutine relative and return om sub.

1 Bulcin condition code inp

Sixtan instructions ae dependent on external condition

control

‘+ Seventeentevel pushipop stack

(Onechio storage of subroutine return adcreses ested Up to

Tr ievele doe

‘© Separate inremente for program counter

‘A telatveadcess may be computed and PC may be ince

ranted by one ona hg eyle

GENERAL DESCRIPTION

“The Arm2930's 0 four-it wide Program Control Unit intended

ta perform machina level adersting fneions, athough the

eve can also be used at 2 microprogam sequencer. Four

‘Am2890's may be interconnected to generate Tit sade.

(EK wore) The Am2920 contains a progrtm counts su

outing sack, an auaiary register, and afl adr for com

puting relative addresses

‘The Am2830 performs fve type of instructions. Thess ae

1) Unconditional Feton; 2) Conditional Jump: 3) Conetna!

Jump Subroutine: 4) Conditions! Return from Subroutine

‘a's miscetaneaus structions

“There are four toures of data forthe addr which generates

‘the Adgrets outputs (¥Q-Y3). Thase ar: 1) the Program

‘Counter (PC); 2) te Stack {8}; 3) the auxiliary Rogistr(Rl:

‘and 4) the Direct inputs (D). Under contra ofthe Instruction

inputs {Iga the multiplexers atthe acer inputs allow vac

tous combinations of these ters 1 be gonerated atte tree

Updating of the prowram counter and the auxiliary regster.

‘condition cade input is provided for conitionalInsuctons.

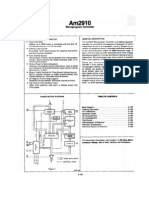

Locie symeoL

BLOCK DIAGRAM

aade

‘Fr epycatin formation, see Chapter V ot Bit ice Miso

‘rocaesor Design, Mick Bick, McGraw Hi Publications,

ri0980

BLOCK DIAGRAM

caterer

im

stack

uctibctxe

%

recisien

‘st

curo)

PROGRAM

Registes

icmementeRt > Cag

YP Veg GND

| snerenwan

6267

, as

5

owe

Tear aM ex =:

i oot sete" | —o

bhi, eS :

‘Am2930

ARCHITECTURE OF THE Am2930

‘The A200 is bipolar Program Control Unit intended for use

in highaneed microprocessor aplieations. The device is or

Cadable,fourbit alee such that three devices allow aestng

‘fupte 4K words of memory and tour devs alow ecdresing

of up to BAK words of memory.

[As shown in the Block Diagram, the device consists of the

faltowing: .

1) A ful adaer with input rutipeeers

21 A Progam Counter Regter with an leramenter and an

Inout multitexer

S)ATT 34 Lattin, FistOut (LIFO) stack consisting of an

ingut multplexet, 17 x4 RAM, and a Stack Pointer

4) An ausiiay regstor with an input mulploxor

5) An intivetion decodar

6) Four 3stato output butters on the address outputs

“The following przeraphs describe cach ofthese block in deta

The Full Adder isa binary device with fll ookahesd carry

loge tor high-speed addition and provision i made for further

lookanead by eluding both camry propagate (P) and eatry

sgorerate (G) cutputs in slowor systems, the carry output

{Cyrai can be connect to the next higher Cn to provide

Fipple block arhmeti. The cary Input tothe adder (Cp is

Inceraly inhibited curing those Instructions whieh do net ee

ule a0 adelton tobe pertotmed, For thes irtctont, a

ote is pesed directly through the adder, Independent of the

ite of Cp

“The multploars atthe A and 8 inputs of the acer ara com

‘rolledby the Instruction decoder hich selects the appropiate

‘ier inputs forthe sinctd Insaco,

Progrom Counter

‘The program counter consits of «raster procteded by on

Incremente. The Program Counter Register (PC) i fourbit,

cege-vigered, D-type rite whichis loaded from the inre-

‘mater outbut on the LOWo-HIGH transition of the clock

Inout (CP athe ond of every intrction,

The incrementer utilizes fll lookahead loge for ish seed

For cascacing comes, tne carry output oF the Incramenter

{Gisq)'s connected tothe incrementer cary input (C) of the

next higher davies. The output ofthe inremantsr, whieh it

Toaded into the P, i aul tothe inerementr input put Cy

‘Tharelor, itis posible to contot the entre caaded ine:

enter from the Ginpuc ofthe feat significant devices2 LOW

fn the Cy input of the fast significant devien wil Sly pass

gH wil cause the outputs of the multiplexer tobe ine

‘mented before they are lauded Into PC. During tree InsruS-

‘ons (uneoncitional Hold and conditions! Hold and Surpond

when the inputs LOW), the 6; input internally inibted

{haretore, data i passed fom she multplensr output the PC

without incrementing, The multiplexer selects the input tothe

incrementer tom either PC ofthe output of the Full Adder,

Sepenaing upon the ietvucton boing searvted. Duting te

Jump, Jump-to Subroutine, and Return instructions, the mult

Blexat ehooces tha ul Adder outputs asthe input tothe fn

romenter if the CC input it LOW. The Full Adder output i

‘so selected for the Reset instruction. For all other Instrue-

tions, the PCs selected asthe input to the ineromenter,

1724 LiF Stack

‘The 17x4 LIFO stack conta ofa multiplex, 8 174 50

anda Stack Pointer (SP) which addres the wards in ts FAM

“The OP atweys pois to the lant word lta ious "48

(Too ofthe Stack. The Top of the Stack (S) savas = he

‘output ofthe RAM,

‘ata is pushed onto the Top of the Stack from sth © «PC

‘eisuriten inte memory location SPT. The Sit incr=oon

fon the LOW. HIGH clock tration at the end of bce

5 that It sil poins tthe let data weiten into the #22

Fora Pop operation the contents of the RAM are not cr,

‘bu the SP is docremented et the end of the cyte 40 tet it

then points tothe raw Top of the Sack

‘Tho SP isan upldonn counter which changes state on the

LOWA0-HIGH tronaition of the Clock Input. Itt intemaly

prevented from incrementing when the stack I full nd trom

‘ecreronting wien the Stack is empty. When the Stack i fil,

‘me RAM write crurry soko wore.

‘The active LOW Empty output (EMPTY) is LOW whan the

stack is empty (ahr the Reset instruction and after te last

‘word has been Popped Trom the tack); the ative LOW Full

‘output (FULL) is LOW either when the sack i full or when

‘he current iotruction bing executed wil fil the stack during

sd after the 172 Pu)

‘Aviary Register (8)

‘Tho Ausilary Register (R} canbe loaded fom ether the Direct

Inputs (0) oF the output ofthe Full Adder ts loaded onthe

LOW:20+HIGH wanstion of the lock Input (CP) the Rese

‘ter Enable input (RE) ie LOW or ifthe Instruction inputs eal

{or it tobe loaded. When RE is LOW, fi loaded trom the D

Inputs unles the Inetrvetion detatee that R be loded from

‘he outputof the Full Adder.

Inseuetion Decoder

‘The lnstruction Decoder generates the signals necessary to

‘establish the date pats and to erable the fading of the PC.

SP, and RAM.

For unconditional instructions, the OE input isnot vied:

‘in may be ether HIGH or LOW. For ennditiona instructions,

{it CE ls LOM, the condition is mat and the conditional oper

{tion i performed; If CC is HIGH, @ Fetah PC i performed.

Output Butters

‘The Adres outputs (¥oY3) are three-state drivers whch

may be diabled elthe under Inetuction contol or by 8 HIGH

fn the Gutput Enable input (OE), Disabling the Y outputs doa

not atfoct the execution of instructions Inside the AmZ930.

Inatrution Ensbie

When HIGH, the Instruction Enable out (TER) forces PC and

SP ito the hold mode and sabes the write cculery tothe

RAM, The aucliry register (R) ix under contol ofthe RE in

‘put when TEW is HIGH, independent of the stata of the Instuc-

fion inputs. The IEN input doesnot affect the combinatorial

data paths or ¥ outputs Io the Am2000. The dat pats ae

‘elected by the Instruction and CC inputs and ae no tfocted

by TEN.

6208

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- AM33C93A SCSI-Bus Interface Controller Timing 5Document3 pagesAM33C93A SCSI-Bus Interface Controller Timing 5SD_DucksoupNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- AM33C93A SCSI-Bus Interface Controller Timing 1Document3 pagesAM33C93A SCSI-Bus Interface Controller Timing 1SD_DucksoupNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- AM33C93A SCSI-Bus Interface Controller Timing 3Document2 pagesAM33C93A SCSI-Bus Interface Controller Timing 3SD_DucksoupNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Am 2910Document14 pagesAm 2910SD_DucksoupNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Am 2909Document15 pagesAm 2909SD_Ducksoup100% (1)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Am 2901Document33 pagesAm 2901SD_DucksoupNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- 68030Document46 pages68030SD_Ducksoup100% (1)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- DAC01Document4 pagesDAC01SD_DucksoupNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- 68882Document45 pages68882SD_Ducksoup100% (2)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)