Professional Documents

Culture Documents

Introduction To Cmos Vlsi Design: Sequential Circuits

Uploaded by

Gaurang ChaudhariOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Introduction To Cmos Vlsi Design: Sequential Circuits

Uploaded by

Gaurang ChaudhariCopyright:

Available Formats

Introduction to

CMOS VLSI

Design

Sequential Circuits

CMOS VLSI Design Sequential Logic Slide 2

Outline

Sequencing

Sequencing Element Design

Max and Min-Delay

Clock Skew

Time Borrowing

Two-Phase Clocking

CMOS VLSI Design Sequential Logic Slide 3

Sequencing

Combinational logic

output depends on current inputs

Sequential logic

output depends on current and previous inputs

Requires separating previous, current, future

Called state or tokens

Ex: FSM, pipeline

CL

clk

in out

clk clk clk

CL CL

Pipeline Finite State Machine

CMOS VLSI Design Sequential Logic Slide 4

Sequencing Cont.

If tokens moved through pipeline at constant speed,

no sequencing elements would be necessary

Ex: fiber-optic cable

Light pulses (tokens) are sent down cable

Next pulse sent before first reaches end of cable

No need for hardware to separate pulses

But dispersion sets min time between pulses

This is called wave pipelining in circuits

In most circuits, dispersion is high

Delay fast tokens so they dont catch slow ones.

CMOS VLSI Design Sequential Logic Slide 5

Sequencing Overhead

Use flip-flops to delay fast tokens so they move

through exactly one stage each cycle.

Inevitably adds some delay to the slow tokens

Makes circuit slower than just the logic delay

Called sequencing overhead

Some people call this clocking overhead

But it applies to asynchronous circuits too

Inevitable side effect of maintaining sequence

CMOS VLSI Design Sequential Logic Slide 6

Sequencing Elements

Latch: Level sensitive

a.k.a. transparent latch, D latch

Flip-flop: edge triggered

A.k.a. master-slave flip-flop, D flip-flop, D register

Timing Diagrams

Transparent

Opaque

Edge-trigger

D

F

l

o

p

L

a

t

c

h

Q

clk clk

D Q

clk

D

Q (latch)

Q (flop)

CMOS VLSI Design Sequential Logic Slide 7

Sequencing Elements

Latch: Level sensitive

a.k.a. transparent latch, D latch

Flip-flop: edge triggered

A.k.a. master-slave flip-flop, D flip-flop, D register

Timing Diagrams

Transparent

Opaque

Edge-trigger

D

F

l

o

p

L

a

t

c

h

Q

clk clk

D Q

clk

D

Q (latch)

Q (flop)

CMOS VLSI Design Sequential Logic Slide 8

Latch Design

Pass Transistor Latch

Pros

+

+

Cons

D Q

|

CMOS VLSI Design Sequential Logic Slide 9

Latch Design

Pass Transistor Latch

Pros

+ Tiny

+ Low clock load

Cons

V

t

drop

nonrestoring

backdriving

output noise sensitivity

dynamic

diffusion input

D Q

|

Used in 1970s

CMOS VLSI Design Sequential Logic Slide 10

Latch Design

Transmission gate

+

- D Q

|

|

CMOS VLSI Design Sequential Logic Slide 11

Latch Design

Transmission gate

+ No V

t

drop

- Requires inverted clock D Q

|

|

CMOS VLSI Design Sequential Logic Slide 12

Latch Design

Inverting buffer

+

+

+ Fixes either

D

|

|

X

Q

D Q

|

|

CMOS VLSI Design Sequential Logic Slide 13

Latch Design

Inverting buffer

+ Restoring

+ No backdriving

+ Fixes either

Output noise sensitivity

Or diffusion input

Inverted output

D

|

|

X

Q

D Q

|

|

CMOS VLSI Design Sequential Logic Slide 14

Latch Design

Tristate feedback

+

|

|

|

|

Q D

X

CMOS VLSI Design Sequential Logic Slide 15

Latch Design

Tristate feedback

+ Static

Backdriving risk

Static latches are now essential

|

|

|

|

Q D

X

CMOS VLSI Design Sequential Logic Slide 16

Latch Design

Buffered input

+

+

|

|

Q D

X

|

|

CMOS VLSI Design Sequential Logic Slide 17

Latch Design

Buffered input

+ Fixes diffusion input

+ Noninverting

|

|

Q D

X

|

|

CMOS VLSI Design Sequential Logic Slide 18

Latch Design

Buffered output

+

|

|

Q

D

X

|

|

CMOS VLSI Design Sequential Logic Slide 19

Latch Design

Buffered output

+ No backdriving

Widely used in standard cells

+ Very robust (most important)

- Rather large

- Rather slow (1.5 2 FO4 delays)

- High clock loading

|

|

Q

D

X

|

|

CMOS VLSI Design Sequential Logic Slide 20

Latch Design

Datapath latch

+

-

|

|

|

|

Q

D

X

CMOS VLSI Design Sequential Logic Slide 21

Latch Design

Datapath latch

+ Smaller, faster

- unbuffered input

|

|

|

|

Q

D

X

CMOS VLSI Design Sequential Logic Slide 22

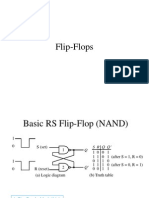

Flip-Flop Design

Flip-flop is built as pair of back-to-back latches

D Q

|

|

|

|

X

D

|

|

|

|

X

Q

Q

|

|

|

|

CMOS VLSI Design Sequential Logic Slide 23

Enable

Enable: ignore clock when en = 0

Mux: increase latch D-Q delay

Clock Gating: increase en setup time, skew

D Q

L

a

t

c

h

D Q

en

en

|

|

L

a

t

c

h

D

Q

|

0

1

en

L

a

t

c

h

D Q

| en

D

Q

|

0

1

en

D Q

| en

F

l

o

p

F

l

o

p

F

l

o

p

Symbol Multiplexer Design Clock Gating Design

CMOS VLSI Design Sequential Logic Slide 24

Reset

Force output low when reset asserted

Synchronous vs. asynchronous

D

|

|

|

|

Q

Q

|

|

|

|

reset

D

|

|

|

|

|

|

Q

|

|

D

reset

|

|

Q

|

|

D

reset

reset

|

|

reset

S

y

n

c

h

r

o

n

o

u

s

R

e

s

e

t

A

s

y

n

c

h

r

o

n

o

u

s

R

e

s

e

t

S

y

m

b

o

l F

l

o

p

D Q

L

a

t

c

h

D Q

reset reset

| |

|

|

Q

reset

CMOS VLSI Design Sequential Logic Slide 25

Set / Reset

Set forces output high when enabled

Flip-flop with asynchronous set and reset

D

|

|

|

|

|

|

Q

|

|

reset

set

reset

set

CMOS VLSI Design Sequential Logic Slide 26

Sequencing Methods

Flip-flops

2-Phase Latches

Pulsed Latches

F

l

i

p

-

F

l

o

p

s

F

l

o

p

L

a

t

c

h

F

l

o

p

clk

|

1

|

2

|

p

clk clk

L

a

t

c

h

L

a

t

c

h

|

p

|

p

|

1

|

1

|

2

2

-

P

h

a

s

e

T

r

a

n

s

p

a

r

e

n

t

L

a

t

c

h

e

s

P

u

l

s

e

d

L

a

t

c

h

e

s

Combinational Logic

Combinational

Logic

Combinational

Logic

Combinational Logic

L

a

t

c

h

L

a

t

c

h

T

c

T

c

/2

t

nonoverlap

t

nonoverlap

t

pw

Half-Cycle 1 Half-Cycle 1

CMOS VLSI Design Sequential Logic Slide 27

Timing Diagrams

F

l

o

p

A

Y

t

pd

Combinational

Logic

A Y

D Q

clk

clk

D

Q

L

a

t

c

h

D Q

clk

clk

D

Q

t

cd

t

setup

t

hold

t

ccq

t

pcq

t

ccq

t

setup

t

hold

t

pcq

t

pdq

t

cdq

t

pd

Logic Prop. Delay

t

cd

Logic Cont. Delay

t

pcq

Latch/Flop Clk-Q Prop Delay

t

ccq

Latch/Flop Clk-Q Cont. Delay

t

pdq

Latch D-Q Prop Delay

t

pcq

Latch D-Q Cont. Delay

t

setup

Latch/Flop Setup Time

t

hold

Latch/Flop Hold Time

Contamination and

Propagation Delays

CMOS VLSI Design Sequential Logic Slide 28

Max-Delay: Flip-Flops

F

1

F

2

clk

clk clk

Combinational Logic

T

c

Q1 D2

Q1

D2

t

pd

t

setup

t

pcq

( )

sequencing overhead

pd c

t T s

CMOS VLSI Design Sequential Logic Slide 29

Max-Delay: Flip-Flops

F

1

F

2

clk

clk clk

Combinational Logic

T

c

Q1 D2

Q1

D2

t

pd

t

setup

t

pcq

( )

setup

sequencing overhead

pd c pcq

t T t t s +

CMOS VLSI Design Sequential Logic Slide 30

Max Delay: 2-Phase Latches

T

c

Q1

L

1

|

1

|

2

L

2

L

3

|

1

|

1

|

2

Combinational

Logic 1

Combinational

Logic 2

Q2 Q3 D1 D2 D3

Q1

D2

Q2

D3

D1

t

pd1

t

pdq1

t

pd2

t

pdq2

( )

1 2

sequencing overhead

pd pd pd c

t t t T = + s

CMOS VLSI Design Sequential Logic Slide 31

Max Delay: 2-Phase Latches

T

c

Q1

L

1

|

1

|

2

L

2

L

3

|

1

|

1

|

2

Combinational

Logic 1

Combinational

Logic 2

Q2 Q3 D1 D2 D3

Q1

D2

Q2

D3

D1

t

pd1

t

pdq1

t

pd2

t

pdq2

( )

1 2

sequencing overhead

2

pd pd pd c pdq

t t t T t = + s

CMOS VLSI Design Sequential Logic Slide 32

Max Delay: Pulsed Latches

T

c

Q1 Q2 D1 D2

Q1

D2

D1

|

p

|

p

|

p

Combinational Logic

L

1

L

2

t

pw

(a) t

pw

> t

setup

Q1

D2

(b) t

pw

< t

setup

T

c

t

pd

t

pdq

t

pcq

t

pd

t

setup

( )

sequencing overhead

max

pd c

t T s

CMOS VLSI Design Sequential Logic Slide 33

Max Delay: Pulsed Latches

T

c

Q1 Q2 D1 D2

Q1

D2

D1

|

p

|

p

|

p

Combinational Logic

L

1

L

2

t

pw

(a) t

pw

> t

setup

Q1

D2

(b) t

pw

< t

setup

T

c

t

pd

t

pdq

t

pcq

t

pd

t

setup

( )

setup

sequencing overhead

max ,

pd c pdq pcq pw

t T t t t t s +

CMOS VLSI Design Sequential Logic Slide 34

Min-Delay: Flip-Flops

cd

t >

CL

clk

Q1

D2

F

1

clk

Q1

F

2

clk

D2

t

cd

t

hold

t

ccq

CMOS VLSI Design Sequential Logic Slide 35

Min-Delay: Flip-Flops

hold cd ccq

t t t >

CL

clk

Q1

D2

F

1

clk

Q1

F

2

clk

D2

t

cd

t

hold

t

ccq

CMOS VLSI Design Sequential Logic Slide 36

Min-Delay: 2-Phase Latches

1, 2

cd cd

t t >

CL

Q1

D2

D2

Q1

|

1

L

1

|

2

L

2

|

1

|

2

t

nonoverlap

t

cd

t

hold

t

ccq

Hold time reduced by

nonoverlap

CMOS VLSI Design Sequential Logic Slide 37

Min-Delay: 2-Phase Latches

1, 2 hold nonoverlap cd cd ccq

t t t t t >

CL

Q1

D2

D2

Q1

|

1

L

1

|

2

L

2

|

1

|

2

t

nonoverlap

t

cd

t

hold

t

ccq

Hold time reduced by

nonoverlap

CMOS VLSI Design Sequential Logic Slide 38

Min-Delay: Pulsed Latches

cd

t >

CL

Q1

D2

Q1

D2

|

p

t

pw

|

p

L

1

|

p

L

2

t

cd

t

hold

t

ccq

Hold time increased

by pulse width

CMOS VLSI Design Sequential Logic Slide 39

Min-Delay: Pulsed Latches

hold cd ccq pw

t t t t > +

CL

Q1

D2

Q1

D2

|

p

t

pw

|

p

L

1

|

p

L

2

t

cd

t

hold

t

ccq

Hold time increased

by pulse width

CMOS VLSI Design Sequential Logic Slide 40

Time Borrowing

In a flop-based system:

Data launches on one rising edge

Must setup before next rising edge

If it arrives late, system fails

If it arrives early, time is wasted

Flops have hard edges

In a latch-based system

Data can pass through latch while transparent

Long cycle of logic can borrow time into next

As long as each loop completes in one cycle

CMOS VLSI Design Sequential Logic Slide 41

Time Borrowing Example

L

a

t

c

h

L

a

t

c

h

L

a

t

c

h

Combinational Logic

Combinational

Logic

Borrowing time across

half-cycle boundary

Borrowing time across

pipeline stage boundary

(a)

(b)

L

a

t

c

h

L

a

t

c

h

Combinational Logic

Combinational

Logic

Loops may borrow time internally but must complete within the cycle

|

1

|

2

|

1

|

1

|

1

|

2

|

2

CMOS VLSI Design Sequential Logic Slide 42

How Much Borrowing?

Q1

L

1

|

1

|

2

L

2

|

1

|

2

Combinational Logic 1

Q2 D1 D2

D2

T

c

T

c

/2

Nominal Half-Cycle 1 Delay

t

borrow

t

nonoverlap

t

setup

( )

borrow setup nonoverlap

2

c

T

t t t s +

2-Phase Latches

borrow setup pw

t t t s

Pulsed Latches

CMOS VLSI Design Sequential Logic Slide 43

Clock Skew

We have assumed zero clock skew

Clocks really have uncertainty in arrival time

Decreases maximum propagation delay

Increases minimum contamination delay

Decreases time borrowing

CMOS VLSI Design Sequential Logic Slide 44

Skew: Flip-Flops

F

1

F

2

clk

clk clk

Combinational Logic

T

c

Q1 D2

Q1

D2

t

skew

CL

Q1

D2

F

1

clk

Q1

F

2

clk

D2

clk

t

skew

t

setup

t

pcq

t

pdq

t

cd

t

hold

t

ccq

( )

setup skew

sequencing overhead

hold skew

pd c pcq

cd ccq

t T t t t

t t t t

s + +

> +

CMOS VLSI Design Sequential Logic Slide 45

Skew: Latches

Q1

L

1

|

1

|

2

L

2

L

3

|

1

|

1

|

2

Combinational

Logic 1

Combinational

Logic 2

Q2 Q3 D1 D2 D3

( )

( )

sequencing overhead

1 2 hold nonoverlap skew

borrow setup nonoverlap skew

2

,

2

pd c pdq

cd cd ccq

c

t T t

t t t t t t

T

t t t t

s

> +

s + +

2-Phase Latches

( )

( )

setup skew

sequencing overhead

hold skew

borrow setup skew

max ,

pd c pdq pcq pw

cd pw ccq

pw

t T t t t t t

t t t t t

t t t t

s + +

> + +

s +

Pulsed Latches

CMOS VLSI Design Sequential Logic Slide 46

Two-Phase Clocking

If setup times are violated, reduce clock speed

If hold times are violated, chip fails at any speed

Working chips are most important

Analyzing clock skew difficult

An easy way to guarantee hold times is to use 2-

phase latches with big nonoverlap times

Call these clocks |

1

, |

2

(ph1, ph2)

CMOS VLSI Design Sequential Logic Slide 47

Safe Flip-Flop

Flip-flop with nonoverlapping clocks

Very slow nonoverlap adds to setup time

But no hold times

In industry, use a better timing analyzer

Add buffers to slow signals if hold time is at risk

D

|

2

X

Q

Q

|

1

|

2

|

1

|

1

|

1

|

2

|

2

CMOS VLSI Design Sequential Logic Slide 48

Summary

Flip-Flops:

Very easy to use, supported by all tools

2-Phase Transparent Latches:

Lots of skew tolerance and time borrowing

Pulsed Latches:

Fast, some skew tol & borrow, hold time risk

You might also like

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- Lect11 SeqDocument35 pagesLect11 Seqkaushik_gupta_4No ratings yet

- Lect11 SeqDocument35 pagesLect11 Seqs.b.v.seshagiri1407No ratings yet

- VLSI Chapter01b Circui&layout PDFDocument48 pagesVLSI Chapter01b Circui&layout PDFJay SharmaNo ratings yet

- Skew DesignDocument29 pagesSkew DesignAshok KoyyalamudiNo ratings yet

- Introduction to CMOS VLSI Design Lecture 1Document56 pagesIntroduction to CMOS VLSI Design Lecture 1darshan_077No ratings yet

- Introduction To Cmos Vlsi Design: Circuits & LayoutDocument47 pagesIntroduction To Cmos Vlsi Design: Circuits & Layoutnehanice123_68509352No ratings yet

- Lecture on flip flops and sequencing elementsDocument0 pagesLecture on flip flops and sequencing elementshim92No ratings yet

- 3-Vld Cmos GateDocument8 pages3-Vld Cmos GateApri KurniawanNo ratings yet

- CPE/EE 427, CPE 527 VLSI Design I Sequential Circuits: - Combinational Logic - Sequential LogicDocument25 pagesCPE/EE 427, CPE 527 VLSI Design I Sequential Circuits: - Combinational Logic - Sequential LogicKamal Kumar Kalra0% (1)

- Introduction To Cmos Vlsi Design: Logical EffortDocument47 pagesIntroduction To Cmos Vlsi Design: Logical EffortDaniel NguyễnNo ratings yet

- Introduction To Cmos Vlsi Design: Circuits & LayoutDocument47 pagesIntroduction To Cmos Vlsi Design: Circuits & LayoutmlwececehodNo ratings yet

- Introduction To Cmos Vlsi DesignDocument40 pagesIntroduction To Cmos Vlsi Designmniyas_1No ratings yet

- CMOS Sequential Circuit Design Lec.-1Document22 pagesCMOS Sequential Circuit Design Lec.-1Parag ParandkarNo ratings yet

- 5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoDocument15 pages5.2 CMOS Logic Gate Design: Serial or Parallel in Rs Transisto of NoRaj AryanNo ratings yet

- Lecture 17Document31 pagesLecture 17KoteswaraRaoBNo ratings yet

- Ca2 FastAddersDocument29 pagesCa2 FastAddersBala BeliveNo ratings yet

- Introduction To Cmos Vlsi DesignDocument40 pagesIntroduction To Cmos Vlsi DesignAdiseshuMiddeNo ratings yet

- Avoiding Metastability in FPGA Devices: David Landoll Applications Architect Mentor Graphics CorpDocument32 pagesAvoiding Metastability in FPGA Devices: David Landoll Applications Architect Mentor Graphics CorpPooja KhareNo ratings yet

- Introduction To Cmos Vlsi Design: Datapath Functional UnitsDocument54 pagesIntroduction To Cmos Vlsi Design: Datapath Functional Unitsjubincb2No ratings yet

- VLSI: Design FlowDocument37 pagesVLSI: Design FlowCGNo ratings yet

- Zipper Cmos Logic CircuitDocument15 pagesZipper Cmos Logic CircuitShreerama Samartha G BhattaNo ratings yet

- References: (Used For Creation of The Presentation Material)Document35 pagesReferences: (Used For Creation of The Presentation Material)Kumar BsnspNo ratings yet

- Introduction to FPGA timing constraints and design flowDocument187 pagesIntroduction to FPGA timing constraints and design flowKhubaib AhmedNo ratings yet

- Logical Effort CMOS VLSI Design LectureDocument33 pagesLogical Effort CMOS VLSI Design LectureAbdullah GubbiNo ratings yet

- Introduction To Cmos Vlsi Design: AddersDocument44 pagesIntroduction To Cmos Vlsi Design: AdderssupradeepthicNo ratings yet

- ECE 4514 Digital Design II Spring 2008 Timing Analysis and Timed SimulationDocument49 pagesECE 4514 Digital Design II Spring 2008 Timing Analysis and Timed SimulationHarold WilsonNo ratings yet

- Debugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichDocument22 pagesDebugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichSandeep PatilNo ratings yet

- Appendix PowerDocument29 pagesAppendix PowerPham VietNo ratings yet

- Finite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Document31 pagesFinite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Sai PrashanthNo ratings yet

- Introduction To Cmos Vlsi Design: Circuits & LayoutDocument54 pagesIntroduction To Cmos Vlsi Design: Circuits & LayoutKalai OmprakashNo ratings yet

- Sub-System Design 5Document177 pagesSub-System Design 5Abdullah Gubbi100% (1)

- Fundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Document29 pagesFundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Huzur AhmedNo ratings yet

- 07 RTL Optimization TechniquesDocument20 pages07 RTL Optimization TechniquesvpsampathNo ratings yet

- Debugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichDocument22 pagesDebugging Clock Trees Will Now Be Easier: Cadence Cdnlive! 2007 Emea Conference in MunichSumanth VarmaNo ratings yet

- CS211 Pipeline Performance ExampleDocument82 pagesCS211 Pipeline Performance ExampleElizabeth AliazNo ratings yet

- Lec 18 Low PowerDocument24 pagesLec 18 Low PowerRahul PanwarNo ratings yet

- sc554 2014 Lecture09Document34 pagessc554 2014 Lecture09tharindu12No ratings yet

- Digital Design: An Embedded Systems Approach Using Verilog: Sequential BasicsDocument73 pagesDigital Design: An Embedded Systems Approach Using Verilog: Sequential Basicsavinash_yuvarajNo ratings yet

- Chapter #10: Finite State Machine ImplementationDocument32 pagesChapter #10: Finite State Machine Implementationphani_abkNo ratings yet

- Chap8 1Document36 pagesChap8 1viratNo ratings yet

- Digital Design and System Implementation Overview of Physical ImplementationsDocument4 pagesDigital Design and System Implementation Overview of Physical ImplementationsGuganesan PerumalNo ratings yet

- Digital Design Gta Esg: - Sequential CircuitDocument34 pagesDigital Design Gta Esg: - Sequential CircuitCeyhan İleriNo ratings yet

- ECE 545-Digital System Design With VHDL: Sequential Logic Review and Algorithmic State Machines 9/9/08Document29 pagesECE 545-Digital System Design With VHDL: Sequential Logic Review and Algorithmic State Machines 9/9/08Rahul TulsianiNo ratings yet

- Introduction To Cmos Vlsi Design: MIPS Processor ExampleDocument43 pagesIntroduction To Cmos Vlsi Design: MIPS Processor ExampleSurbhi PrasadNo ratings yet

- CMOS Digital Design and Implementation TechniquesDocument32 pagesCMOS Digital Design and Implementation Techniquesmeet_kaur865959No ratings yet

- Timing Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignDocument33 pagesTiming Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignVarun KondagunturiNo ratings yet

- Plls and DllsDocument21 pagesPlls and DllsmihaiM500No ratings yet

- VLSI Architecture Design: IEP On Technology CAD (12-17 May 2008)Document52 pagesVLSI Architecture Design: IEP On Technology CAD (12-17 May 2008)Mohammed ElNeanaeiNo ratings yet

- Static Timing Analysis Static Timing AnalysisDocument49 pagesStatic Timing Analysis Static Timing AnalysisRajesh DurisalaNo ratings yet

- Sequential LogicDocument68 pagesSequential LogicbabahussainNo ratings yet

- ContadorDocument1 pageContadorsisissmashxdNo ratings yet

- Design For TestabilityDocument26 pagesDesign For TestabilityDenise NelsonNo ratings yet

- Ch6 I MOS Inverters Switching Characteristics I 2 13Document13 pagesCh6 I MOS Inverters Switching Characteristics I 2 13asad_raza4uNo ratings yet

- Vlsi TechnologyDocument60 pagesVlsi TechnologyPrasad NagavaraNo ratings yet

- Basic flip-flops and memory devicesDocument25 pagesBasic flip-flops and memory devicesNagul MeeraNo ratings yet

- Introduction To Cmos Vlsi Design: Circuit FamiliesDocument34 pagesIntroduction To Cmos Vlsi Design: Circuit FamiliesManjula G RayNo ratings yet

- Lect17 SeqDocument18 pagesLect17 SeqorengeneralNo ratings yet