Professional Documents

Culture Documents

Tek 7633

Uploaded by

Brian FishOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tek 7633

Uploaded by

Brian FishCopyright:

Available Formats

TEKTRONI~

7'633/R7633

STORAGE OSC.llLOSCOPE

WITH OPTIONS

SERVICE

INSTRUCTION

Tektronix,

Inc.

MANUAL

P.o. Box. 500

Beaverton, Oregon 97005 Serial Number

For,t Printing

MAR 1974

010·1761-00

WARR.ANTY AU TEKTRONIX Instruments are warranted against defective materials and workmanship for one year. Any questions wUhrespecl 10 Ihe warranty should betaken up with your TEKTRONIX F lei Engineer or representative. All requests for repairs and repkjifemen&. parts should be directed to the TEKTROlltiK Field Office or re.pr.esentilUveIn your area" This IU .llure you the tast •• , possible s'ervlce. Please Include the Ins,trument Type Number or Part Number and Serial Number wllfi an requests for parts or service. SpecUications and price change privileges reserved. Copyright © 1974 by Tektronlx,lnc., Beave.rton, Oregon. Printed In the United States of America. All rights reserved..Conlents of this publication maynot be reproduced In any form without permission of Tektronix, Inc. U.S.A. and 10reignTEKTRONIX products covered by U.S. and fo.reign patents and/or patents pending. TE.KTRONIXis a registered trademark of Tektronix, Inc.

7633/R7633

Service

TABLE OF CONTENTS

PAGE LIST OF ILLUSTRATIONS LIST OF TABLES SECTION 1 OPERATING INFORMATION 1-1 1-1 1-1 1-1 1-3 1-3 vi ix

PRELIMINARY

OPERATION

AC POWER SOURCES AC POWER CORD OPERATING OPERATING VOLTAGE TEMPERATURE

RACKMOUNTING PLUG-IN UNITS PLUG-IN CONTROLS INSTALLATION AND REMOVAL

1-4 1-4 1-5

AND CONNECTORS AND CONNECTORS 1-6

AND CONNECTORS FRONT PANEL CONTROLS REAR PANEL CONTROLS

1-8 1-10 1-10 1-11 1-11 1-12 1-12 1-12 1-13 1-13

1-14

GENERAL

OPERATING INTENSITY DISPLAY

INFORMATION CONTROL

FOCUS

GRATICULE LIGHT FILTER

BEAMFINDER REDUCED SCAN MODE READOUT DISPLAY STORAGE CARE OF STORAGE VERTICAL TRIGGER MODE SOURCE SCREEN MODES PHOTOGRAPHY

1-15 1-16 1-17 1-18

1-18

X-Y OPERATION INTENSITY MODULATION

RASTER DISPLAY CALIBRATOR SIGNALS OUT

1-19 1-19 1-20 1-21 2-1 2-9

APPLICATIONS SECTION 2 SPECIFICATIONS INTRODUCTION STANDARD ACCESSORIES

7633/R7633 Service

TABLE OF CONTENTS (cont.)

PAGE SECTION 3 THEORY OF OPERATION LOGIC FUNDAMENTALS SYMBOLS LOGIC POLARITY INPUT/OUTPUT NON DIGITAL BLOCK DIAGRAM THEORY OF OPERATION MAIN INTERFACE LOGIC CIRCUIT TABLES DEVICES 3-1 3-2 3-5 3-5 3-5 3-5

<3> <3>

3-9 3-9 3-9 3-9 3-11 3-12 3-15 3-17 3-18 3-20 3-21 3-21 3-21 3-23 3-24 3-25 3-25 3-25 3-26 3-26 3-27 3-27 3-27 3-28 3-28 3-28 3-29 3-29 3-30 3-30

Z-AXIS LOGIC CLOCK GENERATOR VERTICAL CHOPPED BLANKING

CHOP COUNTER VERTICAL VERTICAL MODE CONTROL BINARY

PLUG-IN BINARY OUTPUT BUFFERS TRIGGER SELECTOR ~

TRIGGER MODE AND ADD SIGNALS TRIGGER CHANNEL SWITCH TRIGGER OUTPUT AMPLIFIER VERTICAL VERTICAL SIGNAL BUFFER

INTERFACE VERTICAL AUXILIARY DELAY-LINE DELAY LINE

CHANNEL SWITCH Y-AXIS INPUT AMPLIFIER BUFFER

VERTICAL

AMPLIFIER

<9

NETWORK

CENTERING AND READOUT AMPLIFIER INPUT AMPLIFIER BEAMFINDER

OUTPUT AMPLI FI ER HORIZONTAL AMPLIFIER

HORIZONTAL

CHANNEL SWITCH

RIGHT OUTPUT AMPLIFIER LEFT OUTPUT AMPLIFIER

II

7633/R7633

Service

TABLE OF CONTENTS (cont.)

SIGNALS OUT BOARD

0

OUT

PAGE 3-31 3-31 3-31 3-31 3-31

VERT SIG OUT + GATE OUT + SAWTOOTH CRT CIRCUIT

HIGH VOLTAGE

REGULATION

3-31 3-33 3-34 3-34 3-34 3-35 3-35 3-35 3-38 3-40 3-40 3-40 3-40 3-40

AUTO FOCUS DC RESTORER AUTO FOCUS CONTROL GRID DC RESTORER

Z-AXIS AMPLIFIER CRT CONTROL LOW-VOLTAGE CIRCUITS ~

POWER SUPPLY

POWER INPUT -50-VOL -15-VOL T SUPPLY T SUPPLY

+5-VOL T SUPPL Y +15-VOL T SUPPLY +50-VOL T SUPPLY +130-VOL T SUPPLY GRATICULE CALIBRATOR LIGHT SUPPLY

AND FRONT PANEL

<§>

3-41 3-41 3-42 3-43 3-43

CALIBRATOR READOUT SYSTEM ~

INTRODUCTION THREE-COMPARTMENT DISPLAY FORMAT THE DISPLAY MAINFRAMES

3-43 3-44 3-44 3-51

DEVELOPING TIMER TIME-SLOT

COUNTER

3-53 3-54 3-54 3-54 3-55 3-56 3-59 3-60 3-60

WORD TRIGGER CHANNEL READOUT COUNTER CONTROL LOCKOUT

SINGLE-SHOT ENCODING COLUMN

THE DATA

AND ROW DATA SWITCHES GENERATOR

DISPLAY-SKIP COLUMN

AND ROW DECODERS

iii

7633/R7633

Service

TABLE OF CONTENTS (cont.)

PAGE ZEROS LOGIC AND MEMORY CHARACTER DECIMAL FORMAT Y-OUTPUT X-OUTPUT DISPLAY STORAGE SYSTEM LOGIC OPERATIONAL SECTION 4 MAINTENANCE PRELIMINARY INFORMATION AMPLIFIERS GENERATORS POSITION COUNTER 3-61 3-64 3-64 3-65 3-67 3-67 3-67 3-68 3-68 3-73

POINT LOGIC AND CHARACTER GENERATOR AMPLI FI ER AMPLIFIER SEQUENCE ~

4-1

4-1 4-2 4-3 4-3 4-4 4-5 4-5 4-5 4-5 AIDS EQUIPMENT TECHNIQUES 4-5 4-8 4-8 4-13 PARTS 4-13 4-13 4-13 4-18 4-20

PANEL REMOVAL POWER UNIT REMOVAL PREVENTIVE MAINTENANCE

CLEANING LUBRICATION VISUAL INSPECTION CHECKS

SEMICONDUCTOR RECALIBRATION TROUBLESHOOTING TROUBLESHOOTING TROUBLESHOOTING TROUBLESHOOTING CORRECTIVE MAINTENANCE

OBTAINING SOLDERING COMPONENT

REPLACEMENT TECHNIQUES REPLACEMENT

SEMICONDUCTOR CATHODE-RAY

REPLACEMENT

TUBE REPLACEMENT

SWITCH REPLACEMENT GRATICULE-BULB REPLACEMENT REPLACEMENT

4-21

4-22

POWER TRANSFORMER HIGH VOLTAGE

4-22

4-22 4-23

COMPARTMENT

FUSE REPLACEMENT RECALIBRATION INSTRUMENT AFTER REPAIR

4-23

4-23

REPACKAGING

iv

7633/R7633

Service

TABLE OF CONTENTS

SECTION 5 PERFORMANCE CHECK/CALIBRATION PRELIMINARY INFORMATION INTERVAL FIELD SERVICE

(cont.)

PAGE

5-1 5-1 5-1 5-1 5-1

FIXTURES

CALIBRATION TEKTRONIX

USING THIS PROCEDURE TEST EQUIPMENT REQUIRED SPECIAL CALIBRATION CALIBRATION

EQUIPMENT ALTERNATIVES

SIGNAL CONNECTIONS WARM-UP AND TEMPERATURE PART I-PERFORMANCE CHECK REQUIREMENTS

5-2 5-2 5-2 5-2

5-6 5-6

INTRODUCTION OUTLINE PART II-CALIBRATION INTRODUCTION OUTLINE SECTION 6 SECTION 7 SECTION 8 SECTION 9 OPTIONS ELECTRICAL DIAGRAMS MECHANICAL PARTS LIST PARTS LIST FOR PART II-CALIBRATION FOR PART I-PERFORMANCE CHECK

5-6 5-28 5-28 5-28

CHANGE INFORMATION

7633/R7633

Service

LIST OF ILLUSTRATIONS

PAGE Frontispiece Figure 1-1. Location of voltage-selector jumper. Figure 1-2. Front panel controls and connectors. Figure 1-3. Rear panel controls and connectors. Figure 1-4. Definition of measurement lines on the graticule. Figure 1-5. Location of Readout Mode switch. Figure 1-6. Location of Calibrator jumper on Storage circuit board. Figure 3-1. Block diagram 7633. Figure 3-2. Logic circuit block diagram. Figure 3-3. Z-Axis logic block diagram. Figure 3-4. (A) Clock Generator stage of U55A. (B) Idealized waveforms from Clock Generator stage. Figure 3-5. (A) Input and output pins for Vertical Chopped Blanking stage. IB) Idealized waveforms for Vertical Chopped Blanking stage. Figure 3-6. (A) Logic diagram for Vertical Chopped Blanking stage. (B) Table of input/output combinations for Vertical Chopped Blanking stage. Figure 3-7. Detailed logic diagram of Chop Counter stage. Figure 3-8. Idealized input and output waveforms for Chop Counter stage Figure 3-9. Logic diagram of Vertical Mode Control and Vertical Mode Buffer Amplifier stages. Figure 3-10. Logic diagram of Vertical Binary stage. Figure 3-11. Idealized waveforms showing relationship between input and output waveforms for Vertical Binary and Plug-In Binary stages when operating in ALT mode. Figure 3-12. Logic diagram of Plug-In Binary and Plug-In Alternate Buffer stage. Figure 3-13. Detailed block diagram of Trigger Selector circuit along with simplified diagram of trigger source selection circuitry. Figure 3-14. Input levels at pin 4 of U324. Figure 3-15. Input/output Figure 3-17. Input/output table for Trigger Channel Switch stage. table for Vertical Channel Switch. Figure 3-16. Vertical Interface detailed block diagram. Figure 3-18. Vertical Amplifier detailed block diagram. Figure 3-19. Horizontal Amplifier detailed block diagram. Figure 3-20. CRT circuit detailed block diagram. Figure 3-21. Low-Voltage Power Supply detailed block diagram. Figure 3-22. Schematic illustrating voltage drop between power supply output and load due to resistance of interconnecting wire. Figure 3-23. Calibrator detailed block diagram. Figure 3-24. Location of readout words on the crt identifying the originating plug-in unit and channel (one complete frame shown). 1-2 1-5 1-10 1-11 1-13 1-20 3-6 3-8 3-10 3-11 3-13 3-16 3-17 3-17 3-19 3-19 3-20 3-21 3-22 3-23 3-24 3-25 3-26 3-27 3-29 3-32 3-36 3-39 3-41 3-44

vi

7633/R7633 Service

LIST OF ILLUSTRATIONS (cont.)

PAGE Figure 3-25. Character Selection Matrix for 7633 Readout System. Figure 3-26. Typical readout display where only channel 2 of the Right Vertical and Horizontal units is displayed. Figure 3-27. Detailed block diagram of the Readout System. Figure 3-28. Output waveforms of Timer stage. Figure 3-29. Detail of output at pins 12, 13, 14, and 16 of U2126. Figure 3-30. Timer stage operation when Display-Skip condition occurs. Figure 3-31. Time relationship of the time-slot (TS) pulses produced by U2159. Figure 3-32. Typical encoding scheme for voltage-sensing amplifier plug-in unit. Coding shown for deflection factor of 100 microvolts. Figure 3-33. Idealized current waveforms of: (A) Row analog data, (B) Column analog data. 3-46 3-47 3-48 3-50 3-51 3-52 3-53 3-57 3-58 3-61 3-62 3-65 3-66 3-68 3-69 3-70 3-71 3-72 3-74 4-2 4-6 4-7 4-10 4-17 4-18 5-15 5-17 5-32 5-34 5-46 5-47 5-50 5-57

Fi~re 3-34. Block representation of memory sequence in U2232. Figure 3-35. Typical output waveforms for Zeros Logic and Memory stage operation (at pin 7 of U22321. Figure 3-36. Readout word relating 10 possible character locations to the decimal point instructions that can be encoded, and the resultant crt display. Figure 3-37. Flow chart for character generation by the Readout System. Figure 3-38. Storage circuit simplified block diagram. Figure 3-39. Time relationship of Storage logic pulses. Figure 3-40. BISTABLE mode Storage waveforms. Figure 3-41. VAR PERSIST mode Storage waveforms. Figure 3-42. FAST BISTABLE mode Storage waveforms. Figure 3-43. FAST VAR PERSIST mode Storage waveforms. Figure 4-1. Power Unit removal. Figure 4-2. Location of circuit boards in the 7633. Figure 4-3. Location of circuit boards in the R7633. Figure 4-4. Circuit isolation troubleshooting chart. Figure 4-5. Location of screws holding Low Voltage sub-chassis. Figure 4-6. Location of screws holding Signals Out rear panel. Figure 5-1. Typical crt display when checking X-V phase shift. Figure 5-2. Location of Calibrator AC/DC jumper. Figure 5-3. Location of High-Voltage Test Point. Figure 5-4. Location of adjustments in High-Voltage cover. Figure 5-5. Typical display showing front corner of waveform for Horizontal system high-frequency compensation adjustment. Figure 5-6. Typical crt display when checking X- V phase shift. Figure 5-7. Location of Calibrator AC/DC jumper. Figure 5-8. Idealized Erase waveform.

VII

7633/R7633

Service

LIST OF ILLUSTRATIONS

Figure 5-9_ Idealized Erase and Transfer waveform. Figure 5-10. VAR PERSIST Front Mesh ramp. Figure 5-11. PERSISTENCE pulses.

(ennt.)

PAGE 5-58 5-61 5-63

Section 8 figures are located near their associated diagrams on the foldout pages. Figure 8-1. Semiconductor lead configurations.

Figure 8-2. A1-Main Interface Board. Figure 8-3. A2-Logic Board. Figure 8-4. A3-Trigger Selector Board. Figure 8-5. A4-Verticallnterface Board. Figure 8-6. A5-Vertical Amplifier Board (front). Figure 8-7. AS-Vertical Amplifier Board (rear). Figure 8-8. A6-Horizontal Amplifier Board. Figure 8-9. A7-0utput Signals Board. Figure 8-10. A8-Z-Axis Board. Figu re 8-11. A9-Anode Board. Figure 8-12. A10-High-Voltage Board. Figure 8-13. AII-Low-Voltage Rectifier Board. Figure 8~14. A12-Low-Voltage Regulator Board. Figure 8-15. A13-Readout Board. Figure 8-16. A14-Storage Board. Figure 8-17. Adjustment locations-Z-Axis Board. Figure 8-18. Adjustment locations-High-Voltage Board. Figure 8-19. Adjustment locations-Vertical Amplifier Board. Figure 8-20. Adjustment locations-Horizontal Figure 8-21. Adjustment locations-Readout Amplifier Board. Board. Regulator Board.

Figure 8-22. Adjustment locations-Signals Out Board. Figure 8-23. Adjustment locations-Low-Voltage Figure 8-24. Adjustment locations-Storage Board.

viii

7633/R7633

Service

LIST OF TABLES

PAGE TABLE TABLE TABLE TABLE TABLE TABLE TABLE TABLE 1-1. Power Cord Color-Coding 1-2. Regulating Range and Fuse Data 2-1. ELECTRICAL 2-2. EN VI RONMENTAL 2·3. PHYSICAL 2-4. 7633 SYSTEM SPECIFICATIONS 3-1. Basic Logic Reference 3-2. Standard Readout Format 1-1 1-3 2-1 2-8 2-8 2-10 3-2 3-45 3-55 4-9 4-23 5-3 5-32 Adjustments 5-41

TABLE 3-3. Channel Address Code TABLE 4-1. Power Supply Tolerances TABLE 4-2. Fuse Rating TABLE TABLE TABLE 5-1. Test Equipment 5-2. Power Supply Tolerances 5-3. High-Frequency Compensation

ix

The Tektronix 7633/R7633 Storage Oscilloscope is a solid-state instrument especially designed for fast writing rate storage applications. The 7633 operates in three display modes-NON STORE, STORE, and SAVE, and four storage modesBISTABLE, VAR PERSIST, FAST BISTABLE, and FAST VAR PERSIST. The display and storage functions can be operated in either a full scan or a Reduced Scan mode. In FAST VAR PERSIST, the Reduced Scan feature effectively increases the writing speed approx.imately seven times. The instrument accepts any Tektronix 7-Series plug-in units to form a highly flexible measurement system.

7633/R7633

Service

Section

1-7633/R7633 Service

OPERATING

PRELIMINARY

To effectively ment must be known. trols and connectors, use the 7633/R7633 This section and provides

INFORMATION

OPERATION

the operation information, and capabilities describes of the instruof con-

Storage Oscilloscope, preliminary

provides

operating

operation

general operating

information.

AC POWER SOURCES

This instrument one current-carrying is intended conductor to be operated (the Neutral from a single-phase, earth-referenced power source having from power sources on a three-wire within the Conductor) near earth potential. Operation

where both current-carrying system) is not recommended

conductors

are live with respect to earth (such as phase-to-phase has over-current (fuse) protection

since only the Line Conductor

instrument.

AC POWER CORD

This instrument has a three-wire power cord with a three-terminal terminal polarized plug for connection connected to the power source and safety-earth. strument contact frame. For electric-shock connect The safety-earth protection, of the plug is directly to the in-

insert this plug only in a mating

outlet

with a safety-earth

or otherwise

the frame to a safety earth system. standards as shown in Table 1-1. NOTE

The color-coding

of the cord conductors

is in accordance

with recognized

The power cord on Tektronix instruments may conform to either of the fol/owing two electrical codes: TABLE 1-1

Power Cord Color Coding Conductor Line Neutral Safety-Earth USA (NEC) & Canada Black White Green with Yellow stripe IEC Brown Light Blue * Green with Yellow stripe

*Tinned copper conductor.

OPERATING

In addition, ing procedure

VOLTAGE

can be operated from either a 110-volt within or a 220-volt nominal line-voltage source. ranges can be selected instrument each nominal line voltage source. Use the follow-

The 7633/R7633

three operating to obtain

correct

operation

from the Iine voltage available:

1. Disconnect

the instrument

from the power source. the power unit (nine screws in the R7633; see Figure 1-11.

2. Remove the six screws securing

3. Slide the power unit out of the rear of the chassis.

REV. B,JULY, 1975

1-1

Opera ting I nformation-7.633/

R7633 Service

POWER

UNIT

SECURING SCREVVS

Figure 1,1_

t.ocat ion of voltage-selector

jumper.

4.

To convert from 11 O,volts to 220-volts nominal line voltage, or vice, versa, remove the voltagewith the spare jumper stored on the pi'ns adjacent to the voltage selector

selector jumper and replaceit

area (see Figure 1-1). The jumpers are color coded to indicate the nominal voltage for which they are intended; brown for 11 Q-volt nominal operation and red for 220-vol t nominal operation. provide protection Recti fi er boa rd (see F igur e 1·' for f use local ion and T a bJe 1-2 for fuse ty pal. pl.ug to match the power-source receptacle or use a suitabie adapter. Change the fuse to for the selected nominal line voltage .. Use the fuse located rn the All Fuse holder on the AI so, ch ange the Iin e-cord

'·2

Operating

Information-7633/R7633

Service

5. To convert jumper and re-install

the instrument

from one regulating

range to another, to the desired

remove the voltage selector range. The proper reg(see

it on the set of pins corresponding about

regulating

ulating range will center Table '-2).

the average line voltage to which the instrument

is to be connected

TABLE Regulating

'-2

Range and Fuse Data Regulating Range 220-volts (nominal)

Pins Selected 110-volts LOW MED HI Line Fuse (nominal) 90 to 110 volts 99 to 121 volts 108 to 132 volts 3.2 A slow-blow

180 to 220 volts 198 to 242 volts 218 to 262 volts 1.6 A slow-blow

OPERATING

strument beyond

TEMPERATURE

where the ambient temperatures air temperature -550C is between and +75 C.

0

The 7633 can be operated can be stored the operating in ambient

OOC and +500C.

This in-

between

After storage at temperatures limits before power

limits, allow the chassis temperature

to come within

the operating

is applied.

The 7633 is cooled the rear panel. clearance restrict

by air drawn

in through

the top, side, and bottom externally

panels and exhausted on a heat radiator.

through Adequate

Components

that require

most cooling are mounted

must be provided the air flow through

on all sides to allow heat to be dissipated the holes in the cabinet

from the instrument. Maintain

Do not block or provided

or the heat radiator.

the clearance

by the feet on the bottom

and allow about two inches clearance

on the top, sides, and rear (more if possible).

The R7633

is cooled by air drawn in through Adequate

the air filter on the rear panel and exhausted clearance must be provided at these locations.

through Allow

ports on the right side of the instrument. at least one and one-half inches clearance

behind the air filter and at least one inch on the right side.

A thermal ating level. confined

cutout

interrupts

power to the instrument restored

if the internal returns

temperature

exceeds

a safe operin

Power is automatically

when the temperature

to a safe level.

Operation

areas or close to a heat source may cause the thermal

cutout

to open.

RACKMOUNTING

Instructions Operators manual. and dimensional drawings for rackmounting the R7633 are located in Section 3 of the

1-3

Operating

Information-7633/R7633

Service

PLUG-IN UNITS

The 7633 will accept display combinations measurement measurement up to three 7-series plug-in units. of bandwidth, This plug-in feature sensitivity, permits a variety of and also allows selection In addition, display mode, etc. to meet many system to meet future

requirements. requirements.

it allows expansion

of the oscilloscope

The overall capabilities

of the resultant

system are in large part determined on plug·ins available for use with

by the characteristics this instrument,

of the pluq-in selected. Tektronix,

For complete Inc., catalog.

information

see the current

PLUG-IN INSTALLATION

of the pluq-in with the associated the pluq-in compartment unit to disengage stalled without

AND REMOVAL

align the slots in the top and bottom Push the pluq-in unit firmly into guide rails in the pluq-in compartment.

To install a pluq-in unit into one of the plug-in compartments,

until it locks into place.

To remove a plug-in, pull the release latch on the pluq-in Pluq-in units can be removed or in-

it and pull the unit out of the pluq-in compartment. turning off the instrument power.

It is not necessary

that all of the plug-in compartments for the measurement

be filled to operate to be made.

the instrument;

the only ex-

pluq-in units needed are those required tremes, ments. excess radiation may be radiated

However,

at environmental

into or out of this instrument from Tektronix,

through

the open pluq-in compartorder

Blank pluq-in panels are available

Inc., to cover the unused compartment;

Part No. 016·0155·00.

When the 7633 is calibrated the vertical and horizontal one pluq-in compartment pluq-in units should

in accordance

with the calibration

procedure

given in the Service manual, from

gains are standardized. to another without

This allows calibrated However,

pluq-in units to be changed

recalibration.

the basic calibration

of the individual accuracy.

be checked

when they are installed manual for verification

in this system to venfy their measurement procedure.

See the plug-in unit instruction

Special purpose

plug-in units may have specific restrictions This information

regarding

the plug-in compartments manual

in

which they can be installed.

will be given in the instruction

for these plug-in units.

1-4

Operating Information-7633/R7633

Service

CONTROLS AND CONNECTORS

The major controls for operation of the 7633 are located on the front panel of the instrument. are illustrated in Figure These

'-2.

Figure ,·3 shows the location of rear panel controls and connectors.

The follow·

ing is a brief description

of the controls and connectors shown in Figures 1-2 and 1-3. More detailed operat-

i ng in fo rmat ion is given u nd er Gener aI 0 per ari ng Informatio n.

!i

7853 ...

1766-4

Figur8 1-2.

Front panel controls and connectors,

REV. 8, DEC. 1974

1·5

Operating

Information-7633/R7633

Service

FRONT

PANEL

CONTROLS

descriptions

AND CONNECTORS

are referenced to Figure 1·2.

The following

CD

VERT MODE: LEFT: ALT:

Selects vertical mode operation. Selects signals from the left vertical arnplifieSelects signals from both vertical compartments sweeps (dual trace). compartment for display.

for display on alternate

ADD:

Algebraically plays the sum.

adds the signals from both vertical compartments

and dis-

CHOP:

Selects signals from both vertical compartments The display switches between

for display

(dual trace).

both vertical compartment rate. compartment

signals, during

the sweep, at a one megahertz RIGHT:

Selects signals from the right vertical amplifier

for display.

CD

TRIG SOURCE:

Selects the source of the internal zontal compartment.

trigger for the pluq-in unit in the hori-

LEFT: VERT MODE: RIGHT:

Selects the left vertical compartment Internal trigger signals are determined

as the internal

trigger source.

by the VERT MODE switch. as the internal trigger source.

Selects the right vertical compartment

CD CD CD CD

REDUCED

SCAN-Indicator

light illuminates

when in the Reduced

Scan mode.

INTENSITY-Controls

the brightness

of the display.

REDUCED

SCAN-Pull

switch selects Reduces

Scan operation;

push for normal operation.

R EADOUT -Turns (Option

on the Readout

system

and controls

the brightness

of the Readout

display.

1 deletes this function.l

CD CD

BEAMFINDER-When

pressed,

this switch limits the display to within the graticule

area.

GRATICULE

ILLUM-Controls

the illumination

of the graticule.

1~

Operating

Information-7633/R7633

Service

FRONT

CD

PANEL

CONTROLS

AND CONNECTORS

(cont.)

ERASE-Initiates MANual:

erase cycles; either MANual or PERIODIC. When pressed, initiates an erase cycle to erase the stored display and to the plug-in time-base mode. If the erase period unit.

provide a single-shot Operation PERIODIC: Controls

reset command

is locked out in SA VE display the time between automatic

erase cycles.

ends during a sweep, the erasure This control has a counterclockwise

is delayed

till the end of that sweep. position. Operation

0 FF detent mode.

is locked out in the SAVE display

®

@

PERSISTENCE-Controls stored displays. Operation

the view time of the VAR PERSIST

and FAST VAR PERSIST

is locked out in the SAVE display mode.

FAST -Used

in conjunction

with the VAR PERSIST

and BISTABLE

storage

selections

to choose

the fast transfer

storage modes of either

FAST VAR PERSIST

or FAST BISTABLE.

VAR PERSIST-Selects intensity dependent etc.

the Variable

Persistence

storage mode.

The stored display

is of variable

upon the setting of the STORAGE The stored

LEVEL, density

of charge deposited rate determined by

when storing,

display can be erased at a controllable, control.

continuous

by the setting of the PERSISTENCE the natural

When not being erased, the view time is limited

bright fading of the storage target.

®

@ @ @

BISTABLE-Selects fixed intensity

the BISTABLE (bright)

storage mode. and unwritten

The stored display (background).

is substantially

of two the

levels; written state.

An erase cycle returns

display to the unwritten

POWER-Switch nates to indicate

and indicator. the power is on.

Switch

applies power to the instrument

and the indicator

illumi-

CALIB RATOR-Positive

going square wave or dc voltage selected

by an internal

jumper.

Output

voltage at pin jacks (4 V, 0.4 V, and 4C mV).

STORAGE

LEVEL-Controls

the voltage level on the storage targets. and FAST VAR PERSIST.

Adjusts

writing speed in

FAST BISTABLE,

VAR PERSIST,

®

@

SAVE INTEN-Used reduced tended. intensity,

in conjunction

with SAVE to control

the storage viewing intensity. is proportionately

At ex-

the view time of the stored

VAR PE RSIST display

SAVE-Selects INTENSITY

the SAVE display

mode.

The stored

display

is retained

at a controllable

SAVE

and the erase functions

are locked out.

The time-base

unit is inhibited

except

when the SAVE mode is entered play will wait in the STORE

from STORE

before a sweep occurs.

If this is done. the dis-

mode and enter SAVE automatically

at the end of the next

'-7

Operating Information-7633/R7633

Service

FRONT

PAI\IEL CONTROLS

occuring sweep.

AND CONNECTORS

(cont.)

mode.

This is referred

to as the 'babysitting'

®

@

FAST LEVEL CENTER-Adjusts target and, therefore, the tracking

the voltage level of the FAST target relative to the viewing of the STORAGE LEVEL for the two targets.

STORE-Selects

the STORE

display

mode.

® ® ® ®

NON STORE-Selects

conventional

display mode.

Storage

system is inoperative.

TRACE

ROTATE-Adjusts

alignment

of the trace with the horizontal

graticule

line.

FOCUS-Provides

adjustment

for display

definition.

CAMERA remote

POWER-Three·pin

connector

on crt bezel provides

power output

and receives

sinqle-sweep

reset signal from compatible

camera systems.

REAR PANEL

CONTROLS

AND CONNECTORS

are referenced to Figure '·3.

The following

descriptions

FUSE-Line

voltage fuse.

® ® ®

@

REMOTE

ERASE

IN-Provides

external

connection

for remote

erase.

EXT SS RESET IN-Remote

single sweep reset.

EXT Z AXIS IN-Input

for intensity

modulation

of the crt display.

VERT SIG OUT-Vertical ADD).

signal selected

by TRIG SOURCE

switch

(LEFT,

RIGHT,

ALT, and

® ®

+ GATE OUT -Gate

signal selected

by gate selector

switch (Main, Auxiliary,

and Delay).

+ SAWTOOTH

OUT -Positive·going

sawtooth

from time-base

unit.

'-8

Operating' nformation-7633!

R7633 Service

... '.~

'

••••••••••••••••••••••••••••••••••••••••

,

............... .. ...............•..• •:r:.w~= SSI£.;k~_l~ 3~==J:~~= ,,,.,

,

-.

•• -=

......

'IIII!!w.tII.- ••••••••••••••••••

•••••••••••••••••

fUSE

.....

'

.. .-n:l"MSrllllfll,l'Ir.}

jrMn

f,lJ1fUIWJl_ -

R"ar pa nel controls and conneetors.

GENERAL OPERATING INFORMATION INT~NSITY CONTROL

control may affect the correct when the intensity focus of the display. Slight re-adjustment the crt phosphor. The light filters may be necessary, control level is changed. To protect display.

The setting of the INTENSITY of the FOCUS adjustment do not turn the INTENSITY reduce the observed control

higher than necessary

to provide a satisfactorv

light output

from the crt. When using these fi Iters, avoid advancing When the highest intensity r (per rnanen t tv installed the ambient

the INTENSITY remove the

to a setti ng that may burn the phosphor. protscto

display is desired,

fil ters and use on Iy the cle ar faceplate teositv can also be improved

beh; nd bezel).

Apparen t t ra ce ;nAlso,

in such cases by reducing control

light level or using a viewing hood. the time-base

be careful

that the INTENSITY

is not set too high when changing to the X· Y mode of operation. the display intensity

unit sweep rate from incorporates

a fast to a slow sweep rate, or when changing protection circuitry which automatically

The instrument

reduces

to a lower level when the time-base the crt phosphor at these lower sweep

unit is set to it slow sweep rate.

This reduces

the danger of damaging

rates.

1·9

Operating Information-7633/R7633

Service

DISPLAY

FOCUS

of the crt display. The Readout intensity of this control may be necessary as

The FOCUS adjustment allows control for best definition

should be turned on when adjusting the focus. Slight re-adjustment display conditions change. If a properly adjustment

focused display cannot be obtained with the FOCUS adjustment, section of the Service manual.

the internal Astigmatism

must be re-set; see the Calibration

GRATICULE

The graticule of the 7633 is marked on the inside of the faceplate of the crt, providing accurate, non-parallax measurements. The graticule is divided into eight vertical and ten horizontal square divided into five minor divisions. divisions. Each

full scan division is 0.9 centimeter

1\ Reduced Scan graticule is

etched in the center of the full scan graticule. of a full scan division.

Each Reduced Scan division is exactly half (0.45 centimeter) timing of the plug-in units are calibrated to the of the graticule lines can

The vertical gain and horizontal

graticule so accurate measurements can be made from the crt. The illumination be varied with the GRATICULE ILLUM control.

Fig. '-4 shows the graticuleof

the 7633 and defines the various measurement lines. The terminoNotice the 0%, '0%, rise-

logy defined here will be used in all discussions involving graticule measurements. 90%, and' 00% markings on the left side of the graticule. time measurements.

These markings are provided to facilitate

SECOND VERTICAL LINE

CENTER VERTICAL LINE

TENTH VEFITICAL LINE

100 . . ..

I

....

....

....

. ...

90----~----~,_-+--~4-_.--~.--+--r-~~--~---~----~

rr~~++++++~++~~~~~~+H~~~~~~++~-++++~HORIZONTAL

CENTER LINE

10----+----1--~~~--+--L-4~4--+--L_4--L--~---+--~

\ ....

I

Figure 1-4.

Definition

of measurement

lines on the gratieule.

'-10

Operating Information-7633/R7633

Service

LIGHT

FILTER

The tinted filter provided with the 7633 minimizes light reflections from the face of the crt to improve contrast when viewing the display under high ambient light conditions. This filter should be

removed for waveform photographs or when viewing high writing rate displays. To remove the filter, pull outward on the bottom of the plastic crt mask and remove it from the crt bezel. Remove the tinted filter; leave the clear plastic faceplate protector installed and replace the bezel. The faceplate protector should be left in place at all times to protect the crt faceplate from scratches.

An optional mesh filter is available for use with the 7633. This filter provides shielding against radiated EMI (electro-magnetic interference) from the face of the crt. make the trace more visible under high ambient light conditions. plastic crt mask and the tinted filter. It also serves as a light filter to

The mesh filter fits in place of the Part No. 378-0603-00.

The filter can be ordered by Tektronix

BEAIVIFINDER

The BEAMFINDER switch provides a means of locating a display which overscans the viewing When the BEAMFINDER switch is pressed and held, the display switch to return to a normal disprocedure:

area either vertically or horizontally.

is compressed within the graticule area. Release the BEAMFINDER

play. To locate and reposition an overscanned display, use the following

1. Pressand hold the BEAMFINDER

switch.

2. Increase the vertical and horizontal deflection factors until the vertical deflection is reduced to

about two divisions and the horizontal deflection is reduced to about four divisions (the horizontal deflection needs to be reduced only when in the X-Y mode of operation).

3. Adjust the vertical and horizontal position controls to center the display about the vertical and horizontal center lines of the graticule.

4. Release the BEAMFINDER

switch; the display should remain within the viewing area.

REDUCED

SCAN MODE

to about

The Reduced Scan mode increases the stored writing speed (in centimeters/microsecond)

four times that of the full scan mode. This is achieved by increasing the crt cathode voltage from 1.5 kilovolts in the full scan mode to 3 kilovolts in the Reduced Scan mode, which results in higher beam energy and a smaller spot size.

The calibrated division size changes from 0.9 centimeters in the full scan mode to 0.45 centimeters in Reduced Scan. Calibrated measurements are confined to the inner 8 x 10 Reduced Scan divisions of the graticule area.

1-11

Operating Information-1633/R7633

Service

READOUT MODES (Option 1 deletes)

The cha racters of the readout waveforms. The Readout System d Is-play are wri tten by the cr t beam on a 1ime-share basi s wi th signal operates in a free-running Th e Readout mode to randomly interrupt the wavefOrm

d isol ay to pr esen t the readout

cbaracters.

System can I'llso operate ina GATE T RIG 'D

mode; no readout Signal is produced until after the. sweep has occurred. to have a readout display. Switch 2110,. located on the Readout

In th is mode the sweep must run

See.

board, changes the ReadOlJt modes.

Figu~e 1·5 for location

of 52110.

DISPLAY

PHOTOGRAPHY

record of the crt display can be obtained with an osciltoscoeecerner include complete instruetlons a system.

A permanent

instruction

The

rnanuats

tor

the Tektronix The following

Oscilloscope information

Cameras

for obtaining

waveform photographs.

applies only to the 7633 Oscilloscope.

The crt bezel of the 7633 provides

integral mOll.nting for Tektronix

Osclllcsccps

Cameras,

Three

Pins, located <In ths crt bezel, connect

th e camera man ual for further

power to compatible

camera systems.

These pins also sense con&i ngle·sh ot ph at ogra phy (see

tro I sign 81 fro m Tek tron iX a uta marie cameras to permi t earners -co ntrolled s

in format

ion).

Photographs of waveforms stored in the VAR PERSIST

mode are obtained in the same manner as

those taken j n normal operation.

display,

However, to obtain satisfacrorv photographs of a stored B IS:r AS LE

intensity.

it ls often necessary to switch into the SAVE mode and use reduced

Figure 1-5. Location of Readout Mocfe ,...."itch.

1'1

~)J

Ii I

II

1-12

Operating

Information-7633/R7633

Service

STORAGE

The 7633 Transfer increasing writing speed): Storage Oscilloscope has four selectable storage modes (listed in order of and FAST VAR PER-

BISTABLE,

VAR PERSIST,

FAST BISTABLE,

SIST_ The storage control.

writing speed in all storage LEVEL control

modes is affected

by the setting of the INTENSITY modes except Mesh in VAR

The STORAGE

also adjusts writing speed in all storage adjusts the bias voltage on the Front

BISTABLE. PERSIST

The STORAGE

LEVEL control

mode and on the Fast Mesh in the FAST modes.

Fastest writing speed is obtained ing the trace and the STORAGE

with the INTENSITY

control

set to maximum

without

bloom-

LEVEL set in the two o'clock

position.

The erase cycle removes any previous for receipt of a waveform. of the MAX detent controlled position

display from the Front

{view} Mesh and prepares

this mesh it out

Erase cycles are initiated for PERIODIC range. erasure.

by pressing the MANual knob or by rotating Frequency of PERIODIC

ERASE cycles can be

in the 2 - 10 second

If a sweep is in progress when the PER IODIC ERASE cycle ocThus, the PERIODIC'ERASE sweeps. control can be

curs, the erase cycle is delayed

until the end of sweep. operation

used to set up an erase-after-sweep sent to the time-base single-sweep

for slower periodic

A Single Sweep Reset is if the time-base unit is in the

unit at the end of each erase cycle.

Consequently,

mode, it is automatically

armed to run once following

each erase cycle.

REMOTE

ERASE is commanded

by a ground

closure applied

to the rear panel input.

BISTABLE

MODE storage mode, the INTENSITY control adjusts for optimum stored display.

In the BISTABLE Slower signals require TENCE controls

less intensity

to store than faster signals. mode.

The STORAGE

LEVEL and PERSIS-

do not operate

in the BISTABLE

VARIABLE

PERSISTENCE

MODE mode, the INTENSITY control and STORAGE LEVEL controls adjust the writing it

In the VAR PERSIST speed and the PERSISTENCE fades into the background.

adjusts the length of time the stored signal is visible before

FAST MODES Time-base individual between viewing. unit operation is modified by the Storage intervals. system in the FAST storage modes to permit This permits the Fast Mesh to be prepared from the Fast Mesh to the Front Mesh for

sweeps to recur at about one second sweeps.

After each sweep, the signal is transferred

Then, the Fast Mesh is prepared

again for the next sweep and the cycle repeats.

If an erase cycle occurs, not necessary

Fast Mesh preparation

takes place during the erase cycle. functions to cycle. For instance,

However,

it is

to ERASE for the sweep and transfer

if the time-base

1-13

Operating

Information-7633/R7633 multiple

Service sweeps can be stored by pressing the reset button functions on the time-base automatically

unit is set for single-sweep, unit. operate If the time-base

unit is set for auto triggering,

the sweep and transfer

in a cyclical fashion.

After each sweep, the display transfers for the next sweep. in this manner.

to the F'ont

Mesh for viewing multiple sweeps position

and the Fast Mesh is prepared can be stored automatically is varied between sweeps.

Since no erase cycle is generated,

This can be more easily observed

if the vertical

FAST BISTABLE

MODE the same as BISTABLE except the display is written Therefore, on the Fast Mesh and LEVEL control

This mode operates transferred setting to the Front

Mesh for viewing as described speed.

above.

the STORAGE

affects the stored writing

FAST VARIABLE

PERSISTENCE

MODE of both VAR PERSIST LEVEL adjusts and FAST BISTABLE. The PERSISTENCE

This mode combines control

the operation

adjusts the view time, the STORAGE when the time-base

writing speed, and the display will automatically

sweep and transfer

unit is set for auto triggering.

SAVE MODE The SAVE mode can be entered The intensity of the stored display from either storage mode to retain a stored display indefinitely. When displav.

in the SA VE mode is adjusted

by the SAVE INTEN control. erasure of the stored

the SAVE mode is selected, Also, the time-base occurs.

the ERASE function except

is locked out to prevent

unit is inhibited

when the SAVE mode is entered

from STO R E before a sweep When a sweep oc-

If this is done, the display will wait in the STORE

mode until a sweeo occurs.

curs the display will automatically

enter SAVE_ This is referred

to as the 'Banvsittinq' mode.

CARE OF STORAGE

The following

SCREEN

will prolong the useful storage life of the crt screen used in this instrument.

precautions

1.

Use minimum

beam intensity

to produce

a clear, well-defined

display.

2.

Use minimum

SA VE INT EN when storing

images for extended

periods of time.

3.

Avoid repeated

use of the same area of the screen. occasionally

If a particular

display

is being stored

repeat-

edly, change the vertical

position

to use other portions

of the display area.

1-14

Operating Information-7633/R7633

Service

VERTICAL

MODE

LEFT AND RIGHT MODE When the LEFT or RIGHT button plug-in unit in the selected compartment of the VERT MODE switch is pressed, only the signal from the is displayed.

ALTERNATE

MODE of the VERT MODE switch produces and right vertical compartments a display which alternates between the plug-in

The ALT position units in the left vertical

with each sweep of the crt. a more satisfactory

Although

the AL T mode

can be used at all sweep rates, the CHOP mode provides about 20 milliseconds/division.

display at sweep rates below switching becomes visually

At these slower sweep rates, alternate-mode

perceptible.

NOTE

This instrument will not operate in the A L T mode if the h6rizontal plug-in unit is not operated in the time-base mode.

The TRIG SOURCE

switch allows selection

of the triggering

for an alternate

display.

When this switch This the

is set to the VERT MODE position, provides a stable display signals. showing

each sweep is triggered

by the signal being displayed

on the crt. between

of two unrelated

signals, but does not indicate of the TRIG SOURCE

the time relationship switch,

In either the LEFT or RIGHT positions true time relationship. However,

the two signals are displayed from the plug-in

if the signals are not time-related, on the crt.

the display

unit which is not providing

a trigger signal will appear unstable

CHOPPED

MODE of the VERT MODE switch produces rate. In general, a display which is electronically the best display phenomena switched at sweep are to be with the

The CHOP positior, between channels

at a one-megahertz

the CHOP mode provides dual-trace single-shot

rates lower than about displayed. display.

20 milliseconds/division,

or whenever switching

At faster sweep rates, the chopped

becomes

apparent

and may interfere

Correct

internal switch.

triggering

for the CHOP mode can be obtained

in any of the three positions

of the

TRIG SOURCE from the vertical signal.

When the TRIG SOURCE

switch is set to VERT MODE, the internal unit is triggered

trigger signals

plug-in units are algebraically

added and the time-base positions

from the resultant trig-

Use of the LEFT or RIGHT trigger-source vertical unit only.

triggers the time-base

unit on the internal

ger signal from the selected true time relationship. not providing shot, transient,

This allows two time-related

signals to be displayed for the channel

showing

However,

if the signals are not time-related, unstable.

the display

which is two sinqleunit

the trigger signal will appear or random

The CHOP mode can be used to compare

signals which occur within the time interval determined To provide in time. correct triggering,

by the time-base

(ten times selected must precede

sweep rate).

the display which provides

the trigger signal

the second display

Since the signals show true time-relationship,

time-difference

1·15

Operating I nformation-7633/R7633

Service

measurements can be made from the display.

ALGEBRAIC

ADDITION

The ADD position of the VERT MODE switch can be used to display the sum or difference of two signals, for common-mode rejection to remove an undesired signal, or for dc offset (applying a dc voltage to one channel to offset the dc component of a signal on the other channel). The common-mode rejection ratio between the vertical plug-in compartments of the 7633 is greater than 20: 1 at 50 megahertz. The rejection ratio increases to 100: 1 at dc.

The overall deflection factor on the crt in the ADD mode is the resultant of the algebraic addition of the signals from the two vertical plug-in units. It is difficult to determine the voltage amplitude of the

resultant display unless the amplitude of the signal applied to one of the pluc-in units is known. This is particularly true when the vertical units are set to different deflection factors, since it is not obvious which portion of the display is a result of the signal applied to either pluq-in unit. Also, the polarity and repetition rate of the applied signals enters into the calculation.

The following general precautions should be observed to provide the best display when using the ADD mode:

1. Do not exceed the input voltage rating of the plug-in units.

2. Do not apply large signals to the plug-in inputs. A good rule to follow is not to apply a signal which exceeds an equivalent of about eight times the vertical deflection factors. vertical deflection factor of 0.5 volt/division, For example, with a

the voltage applied to that pluq-in unit should not exceed

4 volts. Larger voltages may result in a distorted display.

3. To ensure the greatest dynamic range in the ADD mode, set the position controls of the pluq-in units to a setting which would result in a mid-screen display if viewed in the LEFT or RIGHT positions of the VERT MODE switch.

4. For similar response from each channel, set the plug-in units for the same input coupling.

TRIGGER

SOURCE

The TRIG SOURCE switch allows selection of the internal trigger signal for the time-base unit. For most applications, this switch can be set to the VERT MODE position. nient, since the internal trigger signal is automatically This position is the most conve-

switched as the VERT 'VlODE switch is changed, or

as the display is electronically switched between the left vertical and right vertical plug-in units in the ALT position of the VERT MODE switch. It also provides a usable trigger signal ill the ADD or CHOP positions

of the VERT MODE switch, since the internal trigger signal in these modes is the algebraic sum of the signals applied to the vertical plug-in units. Therefore, the VERT MODE position ensures that the time-base unit receives a trigger signal regardless of the VERT MODE switch setting, without the need to change the trigger source selection. 1·16

Operating Information-7633/R7633

Service

If correct triggering for the desired display is not obtained in the VERT MODE position, the LEFT or RIGHT positions can be used to obtain the trigger signal from either the left vertical or right vertical plug-in unit. The internal trigger signal is obtained from the selected vertical compartment, whether the plug-in unit in that compartment is selected for display on the crt or not. If the internal trigger signal is

obtai ned from one of the vertical units, but the other vertical unit is selected for display, the internal trigger signal must be time-related to the displayed signal in order to obtain a triggered (stable) display.

X-Y OPERATION

For some applications, it is desirable to display one signal versus another (X-Y) rather than against time (internal sweep). The flexibility of the pluq-in units available for use with the 7633 provides a means Some of the

for applying an external signal to the horizontal deflection system for this type of display.

7B-series time-base units can be operated as amplifiers in addition to their normal use as time-base generators. This feature allows an external signal to provide the horizontal deflection on the crt. For most of the time-base units with the amplifier function, the X (horizontal) signal can be connected either to an

external input connector on the time-base unit or it can be routed to the time-base unit through the internal triggering system (see time-base instruction manual for details). If the latter method is used, the

TRIG SOURCE switch must be set so that the X (horizontal) signal is obtained from one of the vertical units and the Y (vertical) signal is obtained from the other vertical unit. The advantages of using the internal trigger system to provide the X signal are that the attenuator switch of the amplifier unit providing the horizontal signal determines the horizontal deflection factor to allow full-range operation. in units do not have to be removed between compartments when X- Y operation is desired. The plug-

Another method of obtaining an X-V display is to install an amplifier plug-in unit in the horizontal plug-in compartment (check amplifier unit gain as given in the plug-in instruction manual to obtain calibrated if two identical ampli-

horizontal deflection factors).

This method provides the best X-V display, particularly

fier units are used, since both the X and Y input systems will have the same delay time, gain characteristics, input coupling, etc. For further information on obtaining X-V displays, see the plug-in unit manuals. Also, on X-V measurements and interpreting

the reference books listed under Applications provide information the resultant lissajous displays.

INTENSITY MODULATION

Intensity (Z-axis) modulation can be used to relate a third item of electrical phenomena to the vertical (Y-axis) and the horizontal (X-axis) coordinates without affecting the waveshape of the displayed signal. The Z-axis modulating signal applied to the crt circuit changes the intensity of the displayed waveform to provide this type of display. 'Gray scale' intensity modulation can be obtained by applying signals Large amplitude signals of the correct polarity will completely

which do not completely blank the display.

blank the display; the sharpest display is provided by signals with a fast risetime and fall. The voltage amplitude required for visible trace modulation depends upon the setting of the INTENSITY control. A two-

volt peak-to-peak signal will completely blank the display even at high intensity levels. Lower amplitude signals can be used to only change the trace brightness rather than completely blank the display. Negative-

going modulating signals increase the display intensity and positive-going modulating signals decrease the

1·17

Operating display

Information-7633/R7633 intensity.

Service range is dc to 10 megahertz be limited (input voltage derating necessary

Useful input frequency The maximum

above two megahertz).

input voltage should

to 10 volts (de plus peak ac).

Time markers display.

applied

to the EXT Z AXIS input connector horizontal sweep or external from the display. display should horizontal

provide a direct time reference mode operation, if the markers

on the

With uncalibrated

the time markers are not time-related

provide a means of reading time directly to the displayed stable display. waveform, a single-sweep

However,

be used (for internal

sweep only) to provide a

RASTER

DISPLAY

display can be used to effectively both vertically increase the apparent sweep length. signals. For this type

A raster-type of display,

the trace is deflected

and horizontally

by sawtooth

This is accomplished Normally, unit

in the 7633 by installing the time-base

a 7B-series time-base

unit in one of the vertical should

plug-in compartments.

unit in the vertical compartment compartment; Information the number

be set to a slower sweep rate than the time-base traces in the raster depends

in the horizontal

of horizontal

upon the ratio between methods. In the ADD

the two sweep rates. position

can be displayed

on the raster using several different

of the VERT MODE switch, With this method,

the signal from an amplifier

unit can be algebraically on the crt should

added to the verthe distance

tical deflection. between

the vertical signal amplitude Another method

not exceed

the horizontal

lines of the raster.

of displaying of the display.

information

on the raster is to could is

use the EXT Z AXIS input to provide intensity be used to provide a television-type given under Intensity Modulation. display.

modulation

This type of raster display

Complete

information

on operation

using the Z-axis feature

To provide is not provided be used. partment. connections operation

a stable raster display, for the time-base

both time-base

units must be correctly

triggered. external

Internal

triggering must com-

units when they are in the vertical compartments; from the time-base

triggering

Also, blanking

is not provided

units when they ace installed

in a vertical

To blank out the retrace

portion

from the time-base

unit in the vertical compartment, network of the 7633.

special

must be made from this time-base is desirable, blanking contact

unit to the blanking

If this mode of information

your local Tektronix time-base

Field Office or representative

for specific

on obtaining

with the specific

unit being used in the vertical compartment.

CALIBRATOR

GENERAL The internal calibrator of the 7633 provides a convenient signal source 10r checking manual. equipment. basic vertical In addition, the

gain and for adjusting calibrator

probe compensation

as described

in the probe instruction to external

can be used as a convenient

signal source for application

VOLTAGE The calibrator front-panel pin-jack provides connectors accurate output voltages of 40 millivolts, loads. Output

0.4 volt, and 4 volts at the three

is approximately

into high-impedance

resistance

50 ohms

at the 40 mV and 0.4 V pin jacks and approximately

450 ohms at the 4 V pin jack.

(A)

1-18

Operating Info,mation-1633/R7633.

Service

CURRENT

A 40'milliampere, {Tektronix used tocheck one-kilohertz output current is provided when the optional current-loop This output accessory can be

Part No. 012·02·59·00)

is connected

be-tween the 4 V pin jack and ground. probe systems.

and calibrste

current-rneasurlnq

WAVESHAPE The square-wave or adiusting calibrator output si.gnal of the eailbrator

can be used as' a reference

waveform

wavesnsoe

when checking

the compensation

of passive, high·resistance in the displayed

probes'. Since the square-wave output

from the Dc

has a ilat top, any distortion

is due to the probe compensation.

voltage output

is also available by changing a junlPer on the cal ibrator board; see Figure 1·6.

SIGNALS OUT

VERTICAL SIGNAL provides

The VERT SIG OUT connector output signal iH\etermined switch.

sample of the-vertical switCh.

deflec1;ion signa!.

The source of the

by the TRIG SOURCE

The source will follow the setting of the TBIG will follow the VERTICAL

SOURCE

When the TR IG SOURCE is in the VERT MODE the output In. the CHOP mode the signals put signal into 50

0 h ms

MODE switch, RIG HT. The

are

a::lded. The output signals are LEFT, Al T, ADD, and ~5 mill iva Its/d iv ision of the verti ca I signal di spl aved on the svsterns crt.

0n

0 ut

is about

about 0.5 volts/division

of the vertical

signal displaved

n I'

~I

FiliUrB·1~. Location of Cal ibrator [u rnper POSlorapBcircu i t board.

,., 9

Operating Information-7633/R7633

Service

+ GATE

The + GATE connector provides a sweep gate signal that is generated by the time-base plug-in unit. The gate selector switch provides one of three possible gates (MAIN, AUXILIARY, and DELAY). The

duration of the gate pulse is determined by the respective sweep. Auxil iary and Delay gates can only be produced by dual sweep time-base plug-in units. The amplitude of the gate signal is about 50 millivolts into 50 ohms or 10 volts into 1 megohm.

+ SAWTOOTH The SAWTOOTH connector provides a positive going sample of the sawtooth from the time-base unit in the horizontal compartment. time into 50 ohms or 1 volt/unit The rate of rise of the sawtooth signal is about 50 millivolts/unit of

of time into 1 megohm. Unit of time is determined by the time/division

switch of the horizontal plug-in unit.

APPLICATIONS

The 7633 Oscilloscope and its associated plug-in units provide a very flexible measurement system. The capabilities of the overall system depend mainly upon the plug-in units that are chosen for use with this instrument. Specific applications for the individual plug-in units are described in the plug-in manuals.

The overall system can also be used for many applications which are not described in detail either in this manual or in the manuals for the individual plug-in units. Contact your local Tektronix representative for assistance in making specific measurements with this instrument. Field Office or

The following with this instrument.

books describe oscilloscope measurement techniques which can be adapted for use

John D. Lenk, 'Handbook of Oscilloscopes, Theory, and Application', CIiffs, New Jersey, 1968.

Prentice-Hall Inc., Englewood

J. Czech, 'Oscilloscope Measuring Techniques', Springer-Verlag,New

York, 1965.

J. F. Golding, 'Measuring Oscilloscopes', Transatlantic Arts, Inc., 1971.

Charles H. Roth Jr., 'Use of the Oscilloscope', A Programmed Text, Prentice-Hall Inc., Englewood Cliffs, New Jersey, 1970.

1-20

Section 2-7633/R7633

Service

SPECIFICATIONS

I NTRODUCTI

The Tektronix for fast writing form a complete units available 7633 Storage Oscilloscope

ON

high-performance instrument designed

is a solid-state,

rate storage applications. measurement system.

This instrument The flexibility

accepts Tektronix

7-series plug-in units to and the variety of plug-in

of this plug-in feature

allow the system to be used for many measurement

applications.

This instrument column

will meet the electrical complete

characteristics

listed in the Performance

Requirement The following

of Table 2-1 following

calibration

as given in the Service manual. range of OOC to +500C, except

characteristics cated. Warmup

apply over an ambient

temperature

as otherwise

indi-

time for given accuracy

is 30 minutes.

NOTE Many of the measurement capabilities of this instrument mined by the choice of plug-in units. The following are deter-

characteristics

apply to the 7633 Storage Oscilloscope only. See the System Specifications later in this section for characteristics of the complete system.

TABLE

2-1

elECTRICAL

Characteristic

Performance Requirement

VERTICAL DEFLECTION SYSTEM

Supplemental Information

Deflection

Factor

Compatible plug-in units.

with all 7000-series

Between

Compartments Linearity

Within

1%.

Low Frequency

0.1 division or less compression or expansion of a 2·division (at center-screen] signal when positioned vertically within the graticule area. See System 7600-series Specifications instruments. for

Bandwidth

Step Response

Risetime

See System Specifications 7600-series instruments.

for

Isolation Between Compartments

Vertical

At least 100: 1 from DC to 100 MHz.

2-1

Specifications-7633/R7633

Service

TABLE 2-1 (cont.l ELECTRICAL Characteristic Delay Line Performance Requirement Supplemental Information

Permits viewing leading edge of

trqqer signal.

Chopped Mode Rate

Repetition

1 MHz within 20%.

0.4 to 0.6

}lS.

Time Segment From Each Compartment Difference in Delay Between Vertical Compartments Vertical Display Modes

0.5 ns or less.

LEFT:

Left vertical unit only.

Selected

by VERT MODE switch.

ALT: Dual trace, alternate between vertical units. ADD: Added algebraically.

CHOP: Dual trace, chopped between vertical units. RIGHT: only. Right vertical unit

TRIGGERING Trigger Source LEFT VERT: cal only. From left vertiSelected switch. by TRIGGER SOURCE

VERT MODE: Determined vertical mode switch. RIGHT VERT: vertical only. HORIZONTAL Fastest Calibrated Factor Sweep Rate From right

by

DEFLECTION

SYSTEM

5 ns/division.

Compatible with all 7000-series plug-in units.

Deflection

2-2

Specifications-7633/R7633

Service

TABLE

2-1 (cont.l

ELECTRICAL Characteristic Low Frequency Linearity Performance Requirement 0.1 division or less compression or expansion of a 2-division (at center-screen) signal when positioned horizontally within the graticule area. Less than 2° from dc to 35 kHz. Supplemental Information

Phase Shift Between The Vertical and Horizontal Amplifiers Frequency Response Bandwidth IS-Division Reference)

At least 2 MHz.

CALIBRATOR Wave shape Positive-going square wave or de (de voltage selected by internal jumper). 40 mV, 0.4 V, and 4 V. Into 1 MD. load.

Voltage Outputs Voltage Output Accuracy +150C to +350C

Within

1%.

OOC to +500C

Current Output Current Output Accuracy +150C to +350C

Within 2%. 40 mAo

Within 2%. Within 3%.

OOC to +500C

Repetition Output Rate

Within optional current loop accessory (012·0259·00) connected between 4 V pin jack and ground pin jack. Approximately 1 kHz.

Resistance Approximately Approximately 50D.. 450D.,

50 mV and 0.4 V 4V

2·3

Specifications-7633/R7633

Service

TABLE

2-1 (cont.l

ELECTRICAL

Characteristic

Performance

Requirement

Supplemental

Information

OUTPUTS Camera Power (P1041 bezel) Pin 1 - +15 V Pin 3 - single sweep reset Pin 5 - ground at crt

EXTERNAL Sensitivity Rangel (Full Intensity

Z AXIS INPUT

2 V peak to peak.

Useful Input Voltage Frequency

Versus

2 V peak to peak, dc to 2 MHz; reducing to 0.4 V peak to peak at 10 MHz. Positive-going sitv. signal decreases inten-

Polarity

of Operation

Maximum Input

Input Voltage

10 V (de to peak ac). Approximately 500 .Q.

Resistance

CHARACTER

GENERATOR

Character

Size

Adjustable Free-run Triggered

(Vertically independent after sweep.

Only). of sweep. Selected by internal mode switch. Readout

Modes of Operation

POWER SOURCE

Li ne Voltage

Ranges 100 V ± 10%. 110V± 10%.

110 V nominal

120 V ± 10%.

2-4

Specifications-7633/R7633

Service

TABLE 2-1 (cont.l ELECTRICAL Characteristic Line Voltage Ranges 220 V nominal 200 V ± 10%. 220 V ± 10%. 240 V ± 10%. Li ne Frequency Maximum Power Consumption (115 Vac ; 60 Hz) 50 to 60 Hz. 7633: R7633: 170 W, 1.9 A. 180W,2A. Performance Requirement Supplemental Information

Fuse Data 110 V line (Fl000) 220 V line (Fl000) +130 V Supply (F855) +15 V unregulated 3.2 A slow blow. 1.6 A slow blow. 0.15 A fast blow. 2.0 A fast blow.

DISPLA Y (CRT) Cathode·Ray Tube Type Graticule Type Area Reduced Scan Division Internal and illuminated. 8 T7411.

10 divisions

8 x 10 divisions in center of faceplate 0.9 centimeter Full Scan 0.45 centimeter Reduced Scan

Phosphor Accelerating Potential

P31 Approximately 8.5 kV (approximately 10 kV in Reduced Scan). Limits display to within graticule area when BEAMFINDER switch is actuated.

BEAMFINDER

(A)

2-5

Specifications-7633/R7633

Service TABLE

2-1 (cont.l

ELECTRICAL Characteristic Stored Writing Speed Full Scan (center 6 x 8 divisions) FAST VAR PERSIST FAST BISTABLE VAR PERSIST BISTABLE 150div/jJ.s 50 div/as 0.5 div/jJ.s 0.03 div/jJ.s Performance Requirement Supplemental Information

Reduced Scan FAST VAR PERSIST FAST BISTABLE VAR PERSIST BISTABLE 2222 div/jJ.s 400 div/jJ.s 3 div/jJ.s 0.2 div/jJ.s

SIGNALS

OUT

VERT SIG OUT

See Systems Specifications 7600-series instruments.

for

Vertical Signals

LEFT, RIGHT, ALT and ADD

Selected by TRIG SOURCE switch.

Gain Into 50 D. 25 m V /division ±20% system crt to VE RT SIG OUT. Into 1 MD. 0.5 V/division ±20% system crt to VERT SIG OUT. Risetime (Into 50 D.) Centeri ng 5 ns or less. ±3 division system crt to VERT SIG OUT. (1.5 V into 1 MD. or 75 mV into 50 D..) 950 D. within 2%.

Output

Resistance

2-6

Specifications-7633/R7633

TABLE 2-1 (cont.) ELECTRICAL

Service

Characteristic +GATE OUT Gate Signals

Performance Requirement

Supplemental Information

MAIN, AUXI LlARY, and DELAY.

Selected by Gate Selector switch.

Output Into 50 n Into 1 Mn Risetime (Into 50 n) Output Resistance 0.5 V within 10%. 10 V within 10%. 20 ns or less. 950 n within 2%.

+SAWTOOTH OUT Output Into 50 n 50 mV/unit 15%. tlme ' within

Into 1 Mn Output Resistance

1 V/unit tirne ' within 10%. 950 n within 2%.

ELECTRO-MAGNETIC Electro-magnetic interference(emi) in accordance with MI L-STD-461 A as tested in M I L-STD-462 (when equipped with Option 3)

INTERFERENCE

Any unused plug-in compartments must be covered with a blank plug-in panel (emi shielded) in order to meet emi specifications. See Options section for additional information.

Radiated interference

Interference radiated from the instrument under test within the given limits from 150 kilohertz to 1000 megahertz. Interference conducted out of the instrument under test through the power cord within the given limits from 150 ki lohertz to 25 megahertz. Qualifies under National Safe Transit Committee test procedure 1A, Category

Conducted interference

Transportation (packaged instrument, without plugins)

II.

I Referenced

to Time/Div setting.

2-7

Specifications-7633/R7633

Service TABLE 2-2 ENVIRONMENTAL

Characteristic NOTE

Information

This instrument

will meet the electrical characteristics given in the

Performance Requirement column of the Specifications over the following environmental limits.

Temperature Range Operati ng Non-Operating _55 C to +75 C.

0 0

Altitude Operating Non-Operati ng 15,000 ft. Test limit 50,000 ft.

Transportation

(packaged instrument, without plug-in units) qualifies under National Safe Transit test pro-

cedure 1A, Category II.

TABLE 2-3 PHYSICAL Characteristic Ventilation Information Safe operating temperature maintained by forced cooling. Automatic resetting thermal cutout protects instrument from overheating. Anodized aluminum front panel. Painted cabinet.

Finish 7633 Overall Dimensions (measured at maximum point) Height Width Length Net Weight (instrument only)

12.0 in (30.4 em). 8.7 in (23.0 em). 23.7 in (50.2 em). 30 Ib (13.6 kg).

2-8

Specifications-7633/R7633

TABLE 2-3 (cont.l PHYSICAL

Service

Characteristic

R7633 Overall Dimensions (measured at maximum points) Height Width Length 5.25 in (13.4 em). 19 in (48.3 ern). 23 in (57.96 ern).

Information

Net Weight (instrument

only)

30 Ib (13.6 kg).

STAr'WARD

ACCESSORIES

Standard accessories supplied with the 7633 are given in the Mechanical Parts List, in the Service manual. For optional accessories available for use with this instrument, see the Tektronix, I nc., catalog.

2-9

Specifications-7633/R7633

Service

TABLE

2-4

7633 SYSTEM SPECI FICATIONS Accuracy * EXT CAL INT CAL 0.25% 15 to to 50° C 35° C Acc

Amplifier Plug-In Unit 7A11 7A12

Probe

Bandwidth

Risetime (Calculated) 3.5 ns 4.4 ns 4.4 ns 4.7 ns 6.4 ns 7.0 ns 4.7 ns 5.4 ns 5.4 ns 3.5 ns 3.5 ns 3.5 ns 4.7 ns 4.7 ns 3.5 ns 3.5 ns

SIG OUT BW 60 MHz 55 MHz 55 MHz 55 MHz 45 MHz 40 MHz 50 MHz 50 MHz 50 MHz 60 MHz 60 MHz 15 MHz Tr 5.9 ns 6.4 ns 6.4 ns 6.4 ns 7.8 ns 8.8 ns 7.0 ns 7.0 ns 7.0 ns 5.9 ns 5.9 ns 24 ns 7.0 ns 7.0 ns 5.4 ns 5.4 ns

Integral None P6053B None or P6053B or P6055 P6021 P6022 None P6065A None P6053B None None P6065A None P6056/ P6057 None or P6055/ P6060 None P6056/ P6057 None P6053B

100 MHz 80 MHz 80 MHz 75 MHz 55 MHz 50 MHz 80 MHz 65 MHz 60 MHz 100 MHz 100 MHz 100 MHz 75 MHz 70 MHz 100 MHz 100 MHz

2% 2% 3% 1.5% 1.5% 2% 2% 2% 3% 2% 3%

3% 3% 4% 2.5% 2.5% 3% 3% 4% 4% 3% 4%

4% 4% 5% 3.5% 3.5% 4% 4% 5% 5% 4% 5%

7A13

7A14

7A15A

7A16A

7A17 7A18

2% 3% 3% 4%

3% 4% 4% 5%

4% 5% 5% 6%

50 MHz 50 MHz 65 MHz 65 MHz

7A19

7A22

1.0 MHz, ±10% 100 IVIHz 100 MHz

350 ns, ±9% 3.5 ns 3.5 ns

2%

3%

4%

1.0 MHz, ±10% 60 MHz 60 MHz

350 ns ±9% 5.9 ns 5.9 ns

7A24

7A26

100 MHz 100 MHz

3.5 ns 3.5 ns

2% 3%

3% 4%

4% 5%

60 MHz 60 MHz

5.9 ns 5.9 ns

*Deflection Factor Accuracy. Plug-in gain set at a temperature

within 10°C of the operating temperature.

Bandwidth

checked from O°C to +50°C.

The bandwidth which has a bandwidth

of a vertical plug-in used in the horizontal

compartment

is 2 MHz except for the 7A22

of 850 kHz. The X-Y phase shift between 2 similar units is 2° at 35 kHz.

Section 3-7633 Service

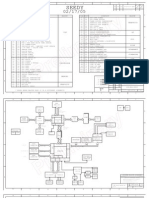

THEORY OF OPERATION

This section begins with a brief discussion of logic fundarnentals followed by a general, block diagrarn description and a detailed description of the circuits that comprise the 7633 Oscilloscope. The circuit description is keyed to the schematic diagrams located in the diagrams section of this manual. Circuits commonly used in the electronics industry are not described in detail. is desired, refer to the following textbooks: If more information on these circuits

Robert C. Baron and Albert T. Piccirilli, 'Digital Logic and Computer Operation', McGraw-Hili, New York, 1967.

Phillip Cutler, 'Semiconductor

Circuit Analysis', McGraw-Hili, New York, 1964.

Lloyd P. Hunter [Ed.}, 'Handbook of Semiconductor Electronics', second edition, McGraw·Hill, New York, 1962.

Jacob Millman and Herbert Taub, 'Pulse, Digital, and Switching Waveforms', McGraw-Hili, New York, 1965.

REV. B, FEB. 1976

3-1

Theory of Operation-7633/R7633

Service

LOGIC FUNDAMENTALS

Digital logic techniques are used to perform many functions within this instrument. operation of the logic circuits are described using logic symbology and terminology. basic introduction to logic concepts. The function and

This portion of the is a

manual is provided to aid in the understanding of these symbols and terms. The following information

SYMBOLS

The operation of circuits within the 7633 which use digital techniques is described using the graphic symbols set forth in military standard M I L·STD-806B. Table 3-1 provides a basic logic reference for the logic devices used within this instrument. Any deviations from the standard symbology, or devices not de·

fined by this standard will be described in the circuit description for the applicable device.

TABLE 3-1 Basic Logic Reference Device AND gate Symbol Description A device with two or more inputs and one output. The output of the AND gate is HI if and only if all of the inputs are at the H I state. Input/Output Input A LO LO HI HI NAND gate A device with two or more inputs and one output. The output of the NAND gate is LO if and or.lv if all of the inputs are at the H I state. Input A LO LO HI HI OR gate A device with two or more inputs and one output. The output of the OR gate is H I if one or more of the inputs are at the H I state. Input A LO LO HI HI NOR gate A device with two or more inputs and one output. The output of the NOR gate is LO if one or more of the inputs are at the H I state. Input A LO LO HI HI B LO HI LO HI B LO HI LO HI Table 'Output X LO LO LO HI 'Output X HI HI HI LO 'Output

:=O-x :=lJ-x

:=D-x :=I>-x

3-2

B

LO HI LO HI

X LO HI HI HI IOutput

B

LO HI LO HI

X HI LO LO LO

Theory TABLE 3-1 (contl Device Inverter Symbol Description

of Operation-7633/R7633

Service

Input/Output Input A LO HI

Table I Output X HI LO

A---{)o-X

LO-state indicator

A device with one input and one output. The output state is always opposite to the input state.

--,

:=O-x :=O-x

A small circle at the input or output of a symbol ind icates that the LO state is the significant state. Absence of the circle ind icates that the H I state is the significant state. Two examples follow: AND gate with at the A input. LO-state ind icator

Input A LO LO HI HI B LO HI LO HI

'Output

X LO HI LO LO

The output of this gate is H I if and only if the A input is LO and the B input is HI. OR gate with the A input: LO-state ind icator at A LO LO HI HI Input B LO HI LO HI

IOutput

X HI HI LO HI

The output of this gate is HI if either the A input is LO or the B input is HI.

Edge symbol

f1

~

1

Normally superimposed on an input line to a logic symbol. Indicates that this input (usually tne trigger input of a flip-flop) responds to the indicated transition of the applied signal.

Triggered (toggle) Flip-Flop

FF

A bistable device and two outputs

with one input (either or both

Input Condition

I Output

Condition

-x

or---- X