Professional Documents

Culture Documents

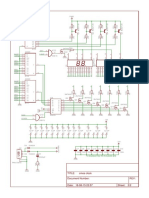

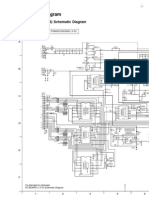

Line Buffer Ver3

Uploaded by

bartel57Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Line Buffer Ver3

Uploaded by

bartel57Copyright:

Available Formats

A X0 X1 Y0 Y1

4H 10174

B Z

W

A X0 X1 Y0 Y1

4J 10174

B Z

W

CD3E

1RC3

CD2E

1RC2

CD1E

1RC1

CD0E

1RC0

VD1E

1RV1

VD0E

1RV0

VD1E

VD0E

10105

11

RM4

10 2G 7

6

A X0 X1 Y0 Y1

4K 10174

B Z

W

B1SL*

7

B1FLIP*

B1CLK

CI

CP

9

3

2

15

9

14

6

7

10136

5H

Q0 Q1 Q2 Q3 S1

11

13

7

5

6

D0 D1 D2 D3 S2

CP

14

15

R67

22

RM8

DI DO

DI DO

18

DI DO

DI DO

16

3

9

D

D

Q

Q

3L

6 RM14

2

1RC0

1RV1

13

DI DO

17

14

DI DO

18

15

DI DO

12

DI DO

16

WE

22

WE

A0

A0

A1

RM11

14

10133

11

RM11

19

15

1RV0

RM1

6J 10

A1

6K 3

A2

A2

6K 10

A3

A3

6K 13

A4

A4

6L 10

A5

A5

6L 13

A6

A6

10

A7

10

A7

6J 3

6L 3

5L

MB7072

RM8

9

RM13

Q

Q

3M

RM14

1RC3

1RC2

11

1RC1

10133

5M

MB7072

BS0

BS0

BS1

BS1

RM7

17

19

15

13

R65

CI

6J 13

4

5

7

9

4

5

7

9

14

15

7

9

14

15

4

5

RM12

13

12

10107

14

3

14

10136

1012

11

5G

Q0 Q1 Q2 Q3 S1

D0 D1 D2 D3 S2

CO

RM7

RM11

1

B1LATCH

1012

HD0 to HD7

from VIDEO

board via

10124 TTL

to ECL

translator

B1HLD

Rev. 3 / 2007-03-23

TRS02-CLK

Line Buffer 1

Schematic Drawn by Markus Karrer Ostermayer

You might also like

- CMOS clock circuit schematicDocument1 pageCMOS clock circuit schematicSRIKANTHNo ratings yet

- Hpt-4240 v5 Psu Circuit DiagramDocument1 pageHpt-4240 v5 Psu Circuit Diagrambadrick4130No ratings yet

- Jadwal SMP Moving OneDocument2 pagesJadwal SMP Moving OneArofaNo ratings yet

- An Send EnteDocument2 pagesAn Send EnteRonald Condori BGNo ratings yet

- Nobreak Manger III - Onda SenoidalDocument1 pageNobreak Manger III - Onda SenoidalFenix Automação100% (1)

- Schema Electrica de Conectare A Procesorului 8086 La 16kW X 16b de Tip 558PP3 Si 16kW X 16b de Tip 537PY10ADocument2 pagesSchema Electrica de Conectare A Procesorului 8086 La 16kW X 16b de Tip 558PP3 Si 16kW X 16b de Tip 537PY10AValeria SerioghinaNo ratings yet

- Circuit diagram of an AT89C51 microcontroller based systemDocument1 pageCircuit diagram of an AT89C51 microcontroller based systemSói Ăn RauNo ratings yet

- BK BambooDocument1 pageBK BambooAT_No1No ratings yet

- Titanium Custom 1100a PDocument13 pagesTitanium Custom 1100a PVictor Rambo100% (1)

- 10606-Figure 1Document1 page10606-Figure 1novanecNo ratings yet

- Proyecto 3Document1 pageProyecto 3fer89chopNo ratings yet

- Toshiba 20hl67 20hlk67Document45 pagesToshiba 20hl67 20hlk67SNOWBALL2008No ratings yet

- Schem AnticDocument1 pageSchem Anticthanhv_25100% (1)

- Daewoo DVG 6000DDocument12 pagesDaewoo DVG 6000DOssian Valera PinedaNo ratings yet

- Computer-Generated Circuit DiagramDocument1 pageComputer-Generated Circuit Diagramatomo33No ratings yet

- Lexsen Cx3 Crossover SCHDocument1 pageLexsen Cx3 Crossover SCHJavier Castellanos BarrazaNo ratings yet

- D C B A: BipolarDocument4 pagesD C B A: Bipolarjurandir21No ratings yet

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- Scott Bernardi PT2399 Echo DelayDocument3 pagesScott Bernardi PT2399 Echo DelayMuhammad Ma'ruf AsyhariNo ratings yet

- Bueno - DSN 06/05/2012 F:/bueno - DSN: File Name: DateDocument1 pageBueno - DSN 06/05/2012 F:/bueno - DSN: File Name: DateOswaldo LucioNo ratings yet

- Kitpicv4 23 10 2013Document1 pageKitpicv4 23 10 2013kipi0811No ratings yet

- Compact title for circuit diagram documentDocument3 pagesCompact title for circuit diagram documentAdrian PeterNo ratings yet

- Conversor AdDocument1 pageConversor AdJherson Andrade TenorioNo ratings yet

- IO Door Board SchematicDocument2 pagesIO Door Board Schematicvilla1960No ratings yet

- Plano FinalDocument1 pagePlano FinalVictor LunaNo ratings yet

- Self Stoping Counter Asynchronous Modulus 13Document2 pagesSelf Stoping Counter Asynchronous Modulus 13Faris Azhari AbdulfattahNo ratings yet

- LEDgn 7-Segment Display CircuitDocument1 pageLEDgn 7-Segment Display Circuitkonan_heriNo ratings yet

- Evens C-500S: TitleDocument1 pageEvens C-500S: TitleLeosonido Reyes100% (1)

- E1 SW1 BT1 Battery: 1 2 3 4 5 6 7 8 1 6 1 5 1 4 1 3 1 2 1 1 1 0 9 VCC ANT Di/PDocument2 pagesE1 SW1 BT1 Battery: 1 2 3 4 5 6 7 8 1 6 1 5 1 4 1 3 1 2 1 1 1 0 9 VCC ANT Di/PJeevan Landge PatilNo ratings yet

- E1 SW1 BT1 Battery: 1 2 3 4 5 6 7 8 1 6 1 5 1 4 1 3 1 2 1 1 1 0 9 VCC ANT Di/PDocument2 pagesE1 SW1 BT1 Battery: 1 2 3 4 5 6 7 8 1 6 1 5 1 4 1 3 1 2 1 1 1 0 9 VCC ANT Di/PJeevan Landge PatilNo ratings yet

- SOHAG 500 BUSBAR PROTECTION E00R PRE FINALDocument66 pagesSOHAG 500 BUSBAR PROTECTION E00R PRE FINALSherifNo ratings yet

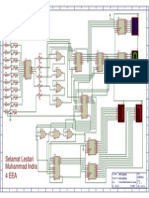

- Skema Calculator SederhanaDocument1 pageSkema Calculator SederhanaSelamat LestariNo ratings yet

- Nobreak SMS Net Station 1200VA uST1200BiFX Esquema Elétrico - UnlockedDocument1 pageNobreak SMS Net Station 1200VA uST1200BiFX Esquema Elétrico - UnlockedFernandoBeliever64% (14)

- Compo SentDocument3 pagesCompo SentBadri RiadhNo ratings yet

- Diagrama Electrico TVs Lider 8823-5VA42 PDFDocument1 pageDiagrama Electrico TVs Lider 8823-5VA42 PDFRobert VicuñaNo ratings yet

- Pma64Xxm: Osd-GDocument1 pagePma64Xxm: Osd-GOksanaHontsharNo ratings yet

- J1 2 1 320V circuit diagramDocument1 pageJ1 2 1 320V circuit diagramaladinthewizardNo ratings yet

- Bogner XTC 100B PreampDocument1 pageBogner XTC 100B Preampprimus2No ratings yet

- Page Revision Sheet Number: N.C: No ConnectionDocument4 pagesPage Revision Sheet Number: N.C: No Connectioncentauro2013No ratings yet

- Compact Circuit Diagram of an Inverter Bypass Switching BoardDocument1 pageCompact Circuit Diagram of an Inverter Bypass Switching BoardOmarNo ratings yet

- Arduino L298 Shield SCHDocument1 pageArduino L298 Shield SCHAlbin CGNo ratings yet

- Sri Lanka Institute of Information Technology: Midterm Marks SheetDocument20 pagesSri Lanka Institute of Information Technology: Midterm Marks SheetSahan Harinda NagodawithanaNo ratings yet

- CPU Board Logic Diagram System 6 PinballDocument0 pagesCPU Board Logic Diagram System 6 PinballMauricio RaúlNo ratings yet

- GPL32200A EMUBOARD SchematicDocument9 pagesGPL32200A EMUBOARD SchematicFrancis TaisantNo ratings yet

- SAP-1 Simple As Possible Computer Schematic DiagramDocument1 pageSAP-1 Simple As Possible Computer Schematic Diagrampong74ls100% (5)

- 5.1. SC-Board (1 of 3) Schematic DiagramDocument14 pages5.1. SC-Board (1 of 3) Schematic DiagramDark NeuhausNo ratings yet

- SemaforoDocument1 pageSemaforoalianzanotteNo ratings yet

- L289N ModuleDocument1 pageL289N ModuleHùng NguyenNo ratings yet

- Toda E Qualquer Alteração Será Feita Sem Prévio AvisoDocument2 pagesToda E Qualquer Alteração Será Feita Sem Prévio AvisodiegoNo ratings yet

- Gc150ata 01Document5 pagesGc150ata 01ValdairVelozoSoaresNo ratings yet

- Circuit diagram with multiple componentsDocument1 pageCircuit diagram with multiple componentsNo KidderNo ratings yet

- Silver TV Portable Black & White Diagrama PDFDocument1 pageSilver TV Portable Black & White Diagrama PDFjaguiro100% (2)

- Stepped BP EqDocument1 pageStepped BP EqdsajlkfNo ratings yet

- 5x5x5 5 FinalDocument1 page5x5x5 5 FinalIngLLimpiNo ratings yet

- SDR BPFDocument2 pagesSDR BPFRavindran KodakkattilNo ratings yet

- Electronic Circuit Design Ideas: Edn Series for Design EngineersFrom EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersRating: 5 out of 5 stars5/5 (2)