Professional Documents

Culture Documents

Unidade Lógica e Aritmética

Uploaded by

Pablo CarvalhoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Unidade Lógica e Aritmética

Uploaded by

Pablo CarvalhoCopyright:

Available Formats

Projeto de uma Unidade Lgica e Aritmtica

Giovani Pivato, Valci Costa de Oliveira Universidade de Caxias do Sul, CARVI, DPEI Engenharia Eltrica giovanipivato@gmail.com, vcoliveira@rge-rs.com.br Resumo

Implementao de uma Unidade Lgica Aritmtica usando Linguagem de Hardware VHDL, capaz de realizar operaes pr-determinadas com operandos de 8 bits. . Palavras-chave: ULA, Unidade Lgica, Unidade Aritmtica, Unidade Lgica-Aritmtica, Mux, Multiplexador, Somador Completo, Subtrator.

simulaes implementados em VHDL, constam no anexo deste trabalho.

2. Reviso bibliogrfica

A linguagem VHDL possibilita descrever em software o comportamento, funcionalidade de um elemento de hardware ou at de um sistema fsico inteiro. Uma entidade (entity) uma abstrao que descreve um sistema, uma placa, um chip, uma funo ou, at mesmo, uma porta lgica. Na declarao de uma entidade, descreve-se o conjunto de entradas e sadas. Os ports correspondem a pinos e so tratados como objetos de dados. Pode-se atribuir valores ou obt-los de ports. Cada entrada ou sada possui um modo (mode) de operao. Os modos possveis so: In, Out, buffer, inout. Respectivamente, permitem entrada de dados, sada de dados, sada de dados com possibilidade de realimentao e a ultima pode substituir qualquer uma das outras. A arquitetura de uma entidade pode ser descrita de trs formas distintas, mas que, em geral, conduzem a uma mesma implementao funcional. As descries so: comportamentais, por fluxo de dados ou estrutural. As regras bsicas para formao de nomes so, o primeiro caractere deve ser uma letra, o ltimo no pode ser underscore, no so permitidos 2 underscores em seqncia e maiscula / minscula so equivalentes. Os sinais so de vital importncia em virtualmente todos sistemas eletrnicos, podendo transmitir dados internamente ou externamente ao sistema, assumindo assim um papel muito importante em VHDL. Os sinais externos so apresentados na entity e os sinais internos so apresentados na architecture.

1. Introduo

Este artigo tem o propsito de expor a implementao de uma unidade lgica e aritmtica, usando-se uma linguagem de hardware (VHDL), atravs de uma ferramenta computacional (ISE verso 11.1). A execuo do trabalho teve inicio com o estudo e introduo na linguagem VHDL, sua sintaxe, forma de estruturao, comandos e suas particularidades por ser distinta de uma programao usual, como por exemplo, C++. Aps o estudo da linguagem, verificou-se a forma de utilizao da ferramenta computacional ISE verso 11.1, que permite que estruturas escritas na linguagem VHDL sejam sintetizadas, simuladas e inseridas em FPGAs. Utilizando a linguagem e a ferramenta j citadas, foi criada uma entidade que soma 1 bit, aps, interligando esta entidade que soma 1 bit de forma adequada a linguagem, construiu-se uma entidade de soma 8 bits. Na seqncia, foram criadas uma entidade que comporta-se como um MUX, uma entidade que comporta-se como uma unidade aritmtica, uma entidade que comporta-se como uma unidade lgica e aps uma entidade top, que utiliza e interliga todas as outras entidades citadas, de forma orientada a se comportar como uma ULA. Foi simulado o comportamento da ULA na ferramenta de simulao existente no ISE 11.1, buscando verificar a assertividade do projeto executado. Este artigo tem na seqncia uma breve reviso terica, os passos do desenvolvimento, resultados obtidos, concluses e os cdigos das entidades e

3. Desenvolvimento

Para obter uma ULA com as funcionalidades demonstradas na tabela 1, foram desenvolvidas seis entidades em VHDL e interligadas de forma adequada. Na seqncia ser abordado o desenvolvimento de cada entidade e sua funcionalidade.

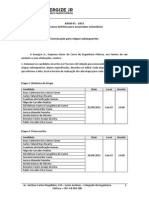

1 IMPLEMENTAO (Entidade ULA) Tabela1 OPERAO Y <= A Y <= B Y <= A +1 COM COUT Y <= B +1 COM COUT Y <= A + B SEM COUT Y <= A + B + CIN COM COUT Y <= A - 1 SEM COUT Y <= B - 1 SEM COUT Y <= A and B Y <= A or B Y <= not A Y <= not B Y <= A xor B Y <= A nand B Y <= 1, se A=B, 0 se diferente de B Y <= 1 se A>B, 0 se menor ou igual a B Atravs da ferramenta de simulaes, foi realizado o teste de funcionalidade da entidade soma1. Visto ser uma entidade simples, foi testada toda a tabela verdade e obteve-se o resultado esperado em todas as combinaes de entrada. A segunda entidade criada denominou-se soma8, que tem a funcionalidade de um somador de 8 bit`s. sua implementao se deu a partir da associao de oito somadores completos de 1 bit (entidade soma1), como pode ser observado no cdigo fonte desta entidade (anexo), as entradas e sadas desta entidade foram declaradas do tipo std_logic_vector para comportar os 8 bits`s. Os carry-out dos somadores foram ligados internamente atravs de sinais, sendo que o carry-out de sada da entidade corresponde ao carry-out final da soma de 8 bits. A entidade soma8 por ser mais complexa e ter 256 possibilidades de entradas distintas, assim, foi testada por amostragem. Foram inseridos valores de entrada e verificadas as sadas para os casos testados. Utilizando-se o somador de 8 bits para as operaes que contemplam Carry-out, foi implementada a entidade Aritmetico, que tem a funo de realizar as operaes aritmticas da ULA. As demais operaes, ou seja, aquelas que no contemplam operaes com Carry-out, foram implementadas diretamente, o que viabilizado pelo uso da biblioteca STD_LOGIC_UNSIGNED. A sada da entidade controlada por um multiplexador 8:1, que determina o valor a ser escrito na sada de acordo com o sinal de seleo que h no momento, sendo que as trs situaes em que se utiliza o componente soma8, esto comutadas, ligadas no sinal S0. Tambm foram utilizados trs multiplexadores 2:1, em cada um das entradas do componente soma8 (SA, SB, CIN), que tem como objetivo, no caso das entradas SA e SB, escrever os valores pr-determinados para A e B nos casos em que h somas do tipo A+1 com Carry-out. No caso no CIN, o multiplexador tem a simples funo de habilitar o uso do Carry-in na soma, fato que ocorre somente quando o Sinal de Seleo 0101. A quarta entidade criada, denominada logic, visa realizar as operaes lgicas da ULA demonstrada na tabela1. Partindo-se da tabela, foram extradas as funes referentes a cada situao do sinal de seleo, que foram implementadas atravs do uso de um multiplexador 8:1. As situaes que demandavam, alm do sinal de seleo, outras condies foram implementadas com o uso da clusula AND, ou seja,

SEL 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

UNIDADE Aritmtica Aritmtica Aritmtica Aritmtica Aritmtica Aritmtica Aritmtica Aritmtica Lgica Lgica Lgica Lgica Lgica Lgica Lgica Lgica

A primeira entidade a ser desenvolvida foi denominada soma1, que tem a funcionalidade de um somador completo de um bit. A implementao desta entidade se deu a partir da tabela verdade de um somador completo, demonstrada na tabela2. Desta, extraiu-se as equaes da sada e do carry-out (cout). Tabela2 ENTRADAS SADAS A B CIN Y COUT 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 As equaes que descrevem a sada Y e o Cout so: Y <= (A Xor B) Xor Cin; Cout <= ((A and B)or (Cin and (A xor B)));

para que o valor de sada fosse o determinado, as duas condies deveriam ser atendidas (sinal de seleo determinado + outra condio). A quinta entidade denominada MUX, um multiplexador 2:1. Tem a simples funo de determinar o valor que ser inscrita na sada Y da ULA de acordo com o primeiro bit(MSB) do sinal de seleo. Finalmente, a ULA propriamente dita, entidade top, uma associao de todas as entidades descritas anteriormente, tem a funo de executar as operaes aritmticas e lgicas e escrever o valor esperado na sada, de acordo com a tabela1. Foram utilizados dois sinais internos do tipo Std_logic_vector de 8 bits, que tem a funo de transportar o sinala de sada da unidade lgica (SL) e da unidade aritmtica(SA) at o multiplexador, que controla a sada geral da ULA. Os testes das entidades Aritmtico, Logic, Mux e ULA foram executados exatamente como os testes da entidade Soma8: fez-se a atribuio dos valores aleatrios nas entradas e observou-se se as sadas correspondiam as valores esperados. 2 IMPLEMENTAO (Entidade ULA_2) Aps a implementao da ULA, conforme descrito acima, partiu-se para a implementao de uma soluo alternativa, tendo como objetivo a busca pela soluo mais eficiente, ou seja, que execute as mesmas operaes ocupando menos hardware. Construiu-se uma nova entidade Arith_2, operador aritmtico alternativo para a ULA. Os componentes soma1 e soma8 so os mesmos utilizados na entidade AriTmetico. A sada da entidade Arith_2 controlada por um multiplexador 8:1, que faz a escolha do sinal a ser escrito no sinal de sada Y da entidade. Assim como na entidade Aritmtico, as operaes que no utilizam Carry-out so executadas diretamente. No entanto, as operaes que envolvem Carry-out foram implementadas com a utilizao de 3 somadores completos de oito bits, do tipo soma8. Em cada situao so escritos valores nas estradas do somador, definidos de acordo com a tabela 1. Foram utilizados 3 sinais do tipo_std_logic_vector de 8 bits, interligados sada de cada um dos somadores. O multiplexador controla a sada a ser habilitada. Foram utilizados, complementarmente, 2 multiplexadores, sendo um deles detinado a controlar o valor de entrada no Carry-In, e um destinado a controlar o valor a ser escrito no Carry-out. Para viabilizar a utilizao dos Trs somadores, foram necessrios 5 sinais do tipo std_logic_vector de 8 bits e 4 sinais do tipo std_logic.

O restante da implementao foi idntica primeira descrita, sendo que para a composio da soluo alternativa mudou-se apenas a Unidade Lgica, tendo o resto da implementao permanecido inalterado. Para a realizao dos testes, foi utilizada a mesma metodologia descrita na implementao anterior.

4. Resultados obtidos

Os resultados obtidos para os testes de todas as entidades indicaram que estas atingiram os objetivos, ou seja, realizaram as operaes de forma a que o resultado obtido nas sadas estivesse de acordo com o determinado para a tabela de solues do problema. Com relao comparao entre as implementaes, pode-se afirmar que a primeira implementao apresentou os resultados mais satisfatrios. A tabela abaixo apresenta os resultados obtidos:

Implementao N de Slices utilizados N de Slices disponves Utilizao

1 71 4656 1% Implementao (ULA) 2 77 1920 4% Implementao (ULA_2) A primeira implementao (ULA) utilizou, no total, 13 sinais internos s entidades: 7 soma8, 4 aritmtico, 2 ULA. A segunda implementao (ULA_2), por sua vez, utilizou 18 sinais: 7 soma8, 9 Arith_2, 2 ULA.

5. Concluses

Aps o desenvolvimento das duas solues e simulao das mesmas, como pode ser observado no corpo deste trabalho e nos resultados obtidos a primeira implementao apresenta vantagens em relao segunda. A primeira implementao ocupa uma rea de hardware significativamente menor do que a segunda. Em relao funcionalidade, as duas implementaes atendem a tabela verdade proposta para esta ULA, logo, ficou evidente a possibilidade de vrias e diferentes implementaes para soluo de um mesmo problema. Das solues desenvolvidas a escolhida foi a primeira implementao, por se mostrar mais eficiente na utilizao do hardware e por conseqncia, no desempenho do circuito implementado. Observa-se tambm, que a utilizao de um nmero menor de sinais internos contribuiu para a eficincia da

primeira implementao, demonstrando que as rotinas/estruturas das entidades criadas pelo programador tm um papel fundamental no s na questo funcionalidade, mas tambm, na eficincia e desempenho que esta implementao ter. Durante o desenvolvimento deste projeto foram enfrentadas dificuldades, sobretudo, pelo desconhecimento das particularidades da linguagem VHDL e da utilizao da ferramenta ISE 11.1. Pelo exposto ao longo deste trabalho e com base nos resultados e argumentaes j realizadas, entendeuse por escolher a primeira implantao da ULA.

Anexo 1 Cdigos fonte das implementaes

1 IMPLEMENTAO ENTIDADA SOMA1 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Soma1 is port( A,B,Cin :in std_logic; Y, Cout: out std_logic); end Soma1; architecture Behavioral of Soma1 is begin Y <= (A Xor B) Xor Cin; Cout <= ((A and B)or (Cin and (A xor B))); end Behavioral; ENTIDADA SOMA8 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity soma8 is Port ( A, B: in std_logic_vector ( 7 downto 0); Cin: in std_logic; Cout: out std_logic; Y : out std_logic_vector ( 7 downto 0)); end soma8; architecture Behavioral of soma8 is component soma1 is port( A,B,Cin :in std_logic; Y, Cout: out std_logic); end component soma1; Signal C0, c1, c2, c3, c4,c5, c6: std_logic; Begin somador1: soma1 port map ( A =>A(0), B=>B(0), Cin=>cin, cout=>c0, Y=>Y(0)); somador2: soma1 port map ( A =>A(1), B=>B(1), Cin=>c0, cout=>c1, Y=>Y(1)); somador3: soma1 port map ( A =>A(2), B=>B(2), Cin=>c1, cout=>c2, Y=>Y(2)); somador4: soma1 port map ( A =>A(3), B=>B(3), Cin=>c2, cout=>c3, Y=>Y(3)); somador5: soma1 port map ( A =>A(4), B=>B(4), Cin=>c3, cout=>c4, Y=>Y(4)); Somador6: soma1 port map ( A =>A(5), B=>B(5), Cin=>c4, cout=>c5, Y=>Y(5)); Somador7: soma1 port map ( A =>A(6), B=>B(6), Cin=>c5, cout=>c6, Y=>Y(6)); Somador8: soma1 port map ( A =>A(7), B=>B(7), Cin=>c6, cout=>cout,Y=>Y(7)); end Behavioral;

ENTIDADE ARITMETICO

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ARITMETICO is port( A,B : in std_logic_vector (7 downto 0 ); Cin :in std_logic; Y: out std_logic_vector ( 7 downto 0); Cout: out std_logic; Sel: in std_logic_vector ( 2 downto 0)); End ARITMETICO; architecture NICE of ARITMETICO is component soma8 is Port ( A, B: in std_logic_vector ( 7 downto 0); Cin: in std_logic; Cout: out std_logic; Y : out std_logic_vector ( 7 downto 0)); end COMPONENT soma8; SIGNAL S0, SA, SB: std_logic_vector (7 downto 0); SIGNAL SIN: std_logic; Begin Y <= A WHEN SEL = "000" ELSE B WHEN SEL = "001" ELSE A + B WHEN SEL = "100" ELSE A - 1 WHEN SEL = "110" ELSE B-1 WHEN SEL = "111" ELSE S0; somador: soma8 port map (A=>SA ,B=> SB, Cin=>Sin, cout=>cout, Y => S0); SA <= "00000001" WHEN SEL = "011" ELSE A; SB <= "00000001" WHEN SEL ="010" ELSE B; SIN <= CIN WHEN SEL ="101" ELSE '0'; end NICE; ENTIDADE LOGIC library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity logic is Port (A, B : in std_logic_vector ( 7 downto 0); Sel : in std_logic_vector ( 2 downto 0); Y: out std_logic_vector ( 7 downto 0)); end logic; architecture nova of logic is begin

Y <= A AND B WHEN SEL = "000" ELSE A OR B WHEN SEL = "001" ELSE NOT A WHEN SEL = "010" ELSE NOT B WHEN SEL = "011" ELSE A XOR B WHEN SEL = "100" ELSE A NAND B WHEN SEL = "101" ELSE "00000001" WHEN SEL = "110" AND A = B ELSE "00000000" WHEN SEL = "110" AND A /= B ELSE "00000001" WHEN SEL = "111" AND A > B ELSE "00000000"; end nova; ENTIDADE MUX library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity mux is port ( Y_LOGIC: IN std_logic_vector ( 7 downto 0); Y_ARITH: IN std_logic_vector ( 7 downto 0); SEL: IN std_logic ; Y: OUT std_logic_vector (7 downto 0)); end mux; architecture solar of mux is begin Y <= Y_ARITH WHEN SEL = '0' ELSE Y_LOGIC; end SOLAR; ENTIDADE ULA SOLUO FINAL library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ULA is port( A,B : in std_logic_vector ( 7 downto 0); Cin :in std_logic; Y: out std_logic_vector (7 downto 0); Cout: out std_logic; Sel: in std_logic_vector ( 3 downto 0)); end ULA; architecture unit of ULA is COMPONENT LOGIC IS Port (A, B : in std_logic_vector ( 7 downto 0); Sel : in std_logic_vector ( 2 downto 0); Y: out std_logic_vector ( 7 downto 0)); END COMPONENT LOGIC;

COMPONENT ARITMETICO IS port( A,B : in std_logic_vector ( 7 downto 0); Cin :in std_logic; Y: out std_logic_vector (7 downto 0); Cout: out std_logic; Sel: in std_logic_vector ( 2 downto 0)); END COMPONENT ARITMETICO; COMPONENT MUX IS port ( Y_LOGIC: IN std_logic_vector ( 7 downto 0); Y_ARITH: IN std_logic_vector ( 7 downto 0); SEL: IN std_logic ; Y: OUT std_logic_vector (7 downto 0)); END COMPONENT MUX; SIGNAL SL, SA : STD_LOGIC_VECTOR (7 DOWNTO 0); begin UNIDADE_LOGICA: LOGIC PORT MAP ( A => A, B => B, SEL => SEL (2 DOWNTO 0) , Y => SL); UNIDADE_ARITMETICA: ARITMETICO PORT MAP ( A => A, B=>B, Cin=>cin, COUT=>COUT, Y=> SA, sel => sel (2 DOWNTO 0)); UNIDADE_MUX: MUX PORT MAP ( Y_LOGIC => SL, Y_ARITH => SA, SEL => SEL(3), Y => Y); end unit; 2 IMPLEMENTAO SOLUO ALTERNATIVA DESCARTADA POR COMPROVADAMENTE SER MENOS EFICIENTE ENTIDADA SOMA1 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Soma1 is port( A,B,Cin :in std_logic; Y, Cout: out std_logic); end Soma1; architecture Behavioral of Soma1 is begin Y <= (A Xor B) Xor Cin; Cout <= ((A and B)or (Cin and (A xor B))); end Behavioral; ENTIDADA SOMA8 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity soma8 is Port ( A, B: in std_logic_vector ( 7 downto 0); Cin: in std_logic;

Cout: out std_logic; Y : out std_logic_vector ( 7 downto 0)); end soma8; architecture Behavioral of soma8 is component soma1 is port( A,B,Cin :in std_logic; Y, Cout: out std_logic); end component soma1; Signal C0, c1, c2, c3, c4,c5, c6: std_logic; Begin somador1: soma1 port map ( A =>A(0), B=>B(0), Cin=>cin, cout=>c0, Y=>Y(0)); somador2: soma1 port map ( A =>A(1), B=>B(1), Cin=>c0, cout=>c1, Y=>Y(1)); somador3: soma1 port map ( A =>A(2), B=>B(2), Cin=>c1, cout=>c2, Y=>Y(2)); somador4: soma1 port map ( A =>A(3), B=>B(3), Cin=>c2, cout=>c3, Y=>Y(3)); somador5: soma1 port map ( A =>A(4), B=>B(4), Cin=>c3, cout=>c4, Y=>Y(4)); Somador6: soma1 port map ( A =>A(5), B=>B(5), Cin=>c4, cout=>c5, Y=>Y(5)); Somador7: soma1 port map ( A =>A(6), B=>B(6), Cin=>c5, cout=>c6, Y=>Y(6)); Somador8: soma1 port map ( A =>A(7), B=>B(7), Cin=>c6, cout=>cout,Y=>Y(7)); end Behavioral;

ENTIDADE ARITH_2

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Arith_2 is port( A,B : in std_logic_vector (7 downto 0 ); Cin :in std_logic; Y: out std_logic_vector ( 7 downto 0); Cout: out std_logic; Sel: in std_logic_vector ( 2 downto 0)); end Arith_2; architecture alternativa of Arith_2 is component soma8 is Port ( A, B: in std_logic_vector ( 7 downto 0); Cin: in std_logic; Cout: out std_logic; Y : out std_logic_vector ( 7 downto 0)); end COMPONENT soma8; SIGNAL S1, S2, S3, SA1, SB1: std_logic_vector (7 downto 0); SIGNAL SIN, SOUT1, SOUT2, SOUT3: std_logic; begin Y <= A WHEN SEL = "000" ELSE B WHEN SEL = "001" ELSE S1 WHEN SEL = "010" ELSE S2 WHEN SEL = "011" ELSE

A + B WHEN SEL = "100" ELSE S3 WHEN SEL = "101" ELSE A - 1 WHEN SEL = "110" ELSE B - 1; SA1 <= "00000001"; SB1 <= "00000001"; SIN <= CIN WHEN SEL = "101" ELSE '0'; COUT <= SOUT1 WHEN SEL = "010" ELSE SOUT2 WHEN SEL = "011" ELSE SOUT3; somador1: soma8 port map (A=> A ,B=> SB1, Cin=> Sin, cout=> SOUT1, Y => S1); somador2: soma8 port map (A=> SA1 ,B=> B, Cin=> Sin, cout=> SOUT2, Y => S2); somador3: soma8 port map (A=> A ,B=> B, Cin=> Sin, cout=> SOUT3, Y => S3);

end alternativa; ENTIDADE LOGIC library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity logic is Port (A, B : in std_logic_vector ( 7 downto 0); Sel : in std_logic_vector ( 2 downto 0); Y: out std_logic_vector ( 7 downto 0)); end logic; architecture nova of logic is begin Y <= A AND B WHEN SEL = "000" ELSE A OR B WHEN SEL = "001" ELSE NOT A WHEN SEL = "010" ELSE NOT B WHEN SEL = "011" ELSE A XOR B WHEN SEL = "100" ELSE A NAND B WHEN SEL = "101" ELSE "00000001" WHEN SEL = "110" AND A = B ELSE "00000000" WHEN SEL = "110" AND A /= B ELSE "00000001" WHEN SEL = "111" AND A > B ELSE "00000000"; end nova; ENTIDADE MUX library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity mux is port ( Y_LOGIC: IN std_logic_vector ( 7 downto 0); Y_ARITH: IN std_logic_vector ( 7 downto 0); SEL: IN std_logic ; Y: OUT std_logic_vector (7 downto 0)); end mux; architecture solar of mux is begin Y <= Y_ARITH WHEN SEL = '0' ELSE Y_LOGIC; end SOLAR; ENTIDADE ULA_2

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ULA_2 is port( A,B : in std_logic_vector ( 7 downto 0); Cin :in std_logic; Y: out std_logic_vector (7 downto 0); Cout: out std_logic; Sel: in std_logic_vector ( 3 downto 0)); end ULA_2; architecture alternate of ULA_2 is COMPONENT LOGIC IS Port (A, B : in std_logic_vector ( 7 downto 0); Sel : in std_logic_vector ( 2 downto 0); Y: out std_logic_vector ( 7 downto 0)); END COMPONENT LOGIC; COMPONENT ARITH_2 IS port( A,B : in std_logic_vector ( 7 downto 0); Cin :in std_logic; Y: out std_logic_vector (7 downto 0); Cout: out std_logic; Sel: in std_logic_vector ( 2 downto 0)); END COMPONENT ARITH_2; COMPONENT MUX IS port ( Y_LOGIC: IN std_logic_vector ( 7 downto 0); Y_ARITH: IN std_logic_vector ( 7 downto 0); SEL: IN std_logic ; Y: OUT std_logic_vector (7 downto 0)); END COMPONENT MUX; SIGNAL SL, SA : STD_LOGIC_VECTOR (7 DOWNTO 0); begin

UNIDADE_LOGICA: LOGIC PORT MAP ( A => A, B => B, SEL => SEL (2 DOWNTO 0) , Y => SL); UNIDADE_ARITMETICA: ARITH_2 PORT MAP ( A => A, B=>B, Cin=>cin, COUT=>COUT, Y=> SA, sel => sel (2 DOWNTO 0)); UNIDADE_MUX: MUX PORT MAP ( Y_LOGIC => SL, Y_ARITH => SA, SEL => SEL(3), Y => Y); end alternate;

You might also like

- Apostila Arcadismo IDocument3 pagesApostila Arcadismo IPablo CarvalhoNo ratings yet

- Anarede Primeiros Passo GraficoDocument19 pagesAnarede Primeiros Passo Graficojeffersonc61No ratings yet

- Tutorial Windows 8 Wireless!!sDocument6 pagesTutorial Windows 8 Wireless!!sanonimo98No ratings yet

- Apresentacão Institucional 4T16 EquatorialDocument33 pagesApresentacão Institucional 4T16 EquatorialPablo CarvalhoNo ratings yet

- Física - Energia 04 - Energia HidraulicaDocument34 pagesFísica - Energia 04 - Energia HidraulicaFísica Concurso Vestibular100% (8)

- Apostila UNBDocument195 pagesApostila UNBPablo CarvalhoNo ratings yet

- Programação em LADDERDocument23 pagesProgramação em LADDERnilsoneryNo ratings yet

- Aneel Atlas Da Energia Eletrica Do Brasil Blog - Conhecimentovaleouro - Blogspot.com by @viniciusf666Document199 pagesAneel Atlas Da Energia Eletrica Do Brasil Blog - Conhecimentovaleouro - Blogspot.com by @viniciusf666JeffholandaNo ratings yet

- VR01.01-00.080 5 EdicaoDocument9 pagesVR01.01-00.080 5 EdicaoPablo CarvalhoNo ratings yet

- Edital Pibex 2016 - 2017Document24 pagesEdital Pibex 2016 - 2017Pablo CarvalhoNo ratings yet

- BoletimEspecial 20151022Document1 pageBoletimEspecial 20151022Pablo CarvalhoNo ratings yet

- Monitoramento Da QEEDocument29 pagesMonitoramento Da QEEPablo CarvalhoNo ratings yet

- Memorial de Instalações ElétricasDocument19 pagesMemorial de Instalações ElétricasMaria MachadoNo ratings yet

- Edital de ConvocaçãoDocument2 pagesEdital de ConvocaçãoPablo CarvalhoNo ratings yet

- BD VHDL Exercicios (Memoria)Document17 pagesBD VHDL Exercicios (Memoria)Pablo CarvalhoNo ratings yet

- SM04 14-01 001Document56 pagesSM04 14-01 001Luis Eduardo NeryNo ratings yet

- Edital Restaurante Universitário - RUDocument12 pagesEdital Restaurante Universitário - RUPablo CarvalhoNo ratings yet

- Artigo Motor DC e PID AnalógicoDocument9 pagesArtigo Motor DC e PID AnalógicolucapetaNo ratings yet

- Apostila HSTDocument79 pagesApostila HSTjrappeltNo ratings yet

- Apostila Ubuntu.8.0.4Document56 pagesApostila Ubuntu.8.0.4Viviane AraújoNo ratings yet

- Aprimoramentos 2Document8 pagesAprimoramentos 2Ana Clara MileipNo ratings yet

- Forno Turbo A Gás - R.27 - 2019 - 250319XXXXXX - 070720XXXXXXDocument24 pagesForno Turbo A Gás - R.27 - 2019 - 250319XXXXXX - 070720XXXXXXPaulo RicardoNo ratings yet

- Modelo ART MGDocument3 pagesModelo ART MGWilson Tadeu100% (1)

- LAUDO GuilhotinaDocument5 pagesLAUDO GuilhotinaWeslley CandeiraNo ratings yet

- Apqp PpapDocument2 pagesApqp PpapAlec SalesNo ratings yet

- Como Testar Pontes Retificadoras (INS028)Document4 pagesComo Testar Pontes Retificadoras (INS028)Juarez Müller CavalheiroNo ratings yet

- ABNT NBR 16172-Determinação de DescontinuidadesDocument8 pagesABNT NBR 16172-Determinação de DescontinuidadesPaulo Cesar Firmino100% (1)

- Manual Compressor AL7003 SDocument39 pagesManual Compressor AL7003 SFrancisco BritoNo ratings yet

- PDF Ms X Power Inverter A - CompressDocument69 pagesPDF Ms X Power Inverter A - CompressOlney Joner100% (2)

- Iniciaaao A Computaaao 1361970249Document67 pagesIniciaaao A Computaaao 1361970249Antônio Ely Pinho VenâncioNo ratings yet

- Manual Instrucoes RC PDFDocument30 pagesManual Instrucoes RC PDFrodriguesantonio1No ratings yet

- Resumo Do Guia BABOK 3 v1.1Document29 pagesResumo Do Guia BABOK 3 v1.1ougaskeNo ratings yet

- Mecanica de Bicicleta Aula 1 PDFDocument32 pagesMecanica de Bicicleta Aula 1 PDFAlex Sandro Heleno da Silva100% (2)

- Manual Sonic 2013 PDFDocument288 pagesManual Sonic 2013 PDFJuscelio DamascenaNo ratings yet

- Aula 01Document25 pagesAula 01idalmirNo ratings yet

- Manual Geladeira DFN52Document28 pagesManual Geladeira DFN52EduardoNo ratings yet

- Material Didatico GruaDocument32 pagesMaterial Didatico GruaMarcos Aurelio100% (15)

- ScaniaDocument28 pagesScaniaMateus Alves marinhoNo ratings yet

- Curso de Informática para Concursos - João Antônio PDFDocument5 pagesCurso de Informática para Concursos - João Antônio PDFandreacarlaleao0% (1)

- 61 Injecao Electronic A de Motores Diesel - EDC, PLD, UI e Common RailDocument4 pages61 Injecao Electronic A de Motores Diesel - EDC, PLD, UI e Common Railmonteirossp100% (2)

- WB-O2 NanoDocument16 pagesWB-O2 NanoMarcos CondeNo ratings yet

- Lâminas Diesel - 2017 - 330 A 3438 KVA 50HzDocument2 pagesLâminas Diesel - 2017 - 330 A 3438 KVA 50HzAriadny CoelhoNo ratings yet

- Manual Consul PDFDocument10 pagesManual Consul PDFMárcio BussNo ratings yet

- Elaboração de PDTIDocument152 pagesElaboração de PDTIEscola Superior de Redes94% (48)

- Conversão Tamanho de Roupas EUA X BrasilDocument7 pagesConversão Tamanho de Roupas EUA X BrasilJordan ArleyNo ratings yet

- Manual de Identdade Visual - RF Comunicação VisualDocument11 pagesManual de Identdade Visual - RF Comunicação VisualRafael BighettiNo ratings yet

- Catalgoo Wy50qt3 - ScooterDocument46 pagesCatalgoo Wy50qt3 - ScooterCarlos RodriguesNo ratings yet

- 00 - Apostila Centro de Usinagem Romi-18!02!2008Document181 pages00 - Apostila Centro de Usinagem Romi-18!02!2008Beto SilvaNo ratings yet

- Manual 0001P140 - PRIME - 140 - Port-Ing-Esp PDFDocument282 pagesManual 0001P140 - PRIME - 140 - Port-Ing-Esp PDFJuanfer SteccaNo ratings yet

- Manual Prático Do SheetCam Rev1.2Document10 pagesManual Prático Do SheetCam Rev1.2Guilherme Pedal0% (1)