Professional Documents

Culture Documents

ch7 Fets New Part A

Uploaded by

Nada AliaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ch7 Fets New Part A

Uploaded by

Nada AliaCopyright:

Available Formats

FETs is also a three terminal devices.

For the FET an electric field is established by the charges present that will control the conduction path of the output circuit without the need for direct contact between the controlling and controlled quantities.

Chapter 7 Part A

BJTs

(i) Current-controlled devices

Differences

FETs

(i) Voltage-controlled devices

FIELD-EFFECT TRANSISTORS (FETs)

Current IC is a direct function of the level of IB. (ii) Bipolar device (npn & pnp) Conduction level is a function of two carriers, electrons and holes. Current ID is a function of the VGS applied to the input circuit. (ii) Unipolar device (n-channel & p-channel) Conduction level is a function of one type of carrier, either electrons (n-channel) or holes (p-channel). 2

CONSTRUCTION and CHARACTERISTICS of JFETs

Types of FETs : (i) Junction FETs (JFET) and (ii) Metal-Oxide-Semiconductor FETs (MOSFET) MOSFET can be divided to two types: (a) Depletion type and (b) Enhancement type. The MOSFET transistor has become one of the most important devices used in the design and construction of integrated circuits for digital computers. Its thermal stability and other general characteristics make it extremely popular in computer circuit design.

3

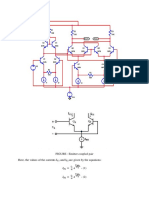

Ex: n-channel JFETs

The major part of the structure is the n-type material that forms the channel between the embedded layers of p-type material. The top of the n-type channel is connected through an ohmic contact to a terminal referred to as the drain (D), while the lower end of the same material is connected through an ohmic contact to a terminal referred to as the source (S). The two p-type materials are connected together and to the gate (G) terminal. Therefore, the drain and source are connected to the ends of the n-type channel and the gate to the two layers of p-type material

Under no-bias condition, there are two p-n junctions. The result is a depletion region at each junction. A depletion region is that region void of free carriers 4 and therefore unable to support conduction through the region.

VGS = 0V, VDS some Positive Value In this figure, a positive voltage VDS has been applied across the channel and the gate has been connected directly to the source to establish the condition VGS=0V.

Analogy

The result is the gate and source terminal at the same potential and a depletion region in the low end of each p-material similar to the distribution of the no-bias condition. The instant voltage VDD (=VDS) is applied, the electrons will be drawn to the drain terminal, establishing the conventional current ID. The path of charge flow clearly reveals that the drain and source currents are equivalent (ID=IS). The flow of charge is limited solely by the resistance of the n-channel between drain 6 and source.

The source of water pressure can be likened to the applied voltage from drain to source that will establish a flow of water (electrons) from the spigot (source). The gate, through an applied signal (potential) controls the flow of water (charge) to the drain

5

It is noted here that the depletion region is wider near the top of both p-type materials. Assuming a uniform resistance in the n-channel, the resistance of the channel can be broken down to the divisions shown in the figure. The current ID will establish the voltage levels through the channel as indicated on the same figure. For example, the upper region of the p-type material will be reverse-biased by about 1.5V, with the lower region only reverse-biased by 0.5V. Recall from the discussion of the diode operation that the greater the applied reverse bias, the wider the depletion region. The fact that the p-n junction is reverse biased for the length of the channel results in a gate current of zero amperes. The fact that IG=0A is an important characteristics of the JFET. 7

As the voltage VDS is increased from 0 to a few volts, the current will increase as determined by Ohms law. The relative straightness of the plot reveals that for the region of low values of VDS, the resistance is essentially constant. As VDS increases and approaches a level referred to as VP, the depletion region will widen, causing a noticeable reduction in the channel width. The reduced path of conduction causes the resistance to increase and the curve in the graph to occur. The more horizontal the curve, the higher the resistance. If VDS is increased to a level where it appears that the two depletion regions would touch as shown in the figure, the condition is referred to as Pinch off will result.

In the saturation region, the level of ID remains essentially the same. Therefore, once VDS > VP the JFET has the characteristics of a source current. As shown in the previous figure (output characteristics), the current is fixed at ID=IDSS but the voltage VDS (for levels > VP) is determined by the applied load.

VGS < 0 V VGS is the voltage from gate to source and is the controlling voltage of the JFET. For the n-channel device the controlling voltage VGS is made more and more negative from its VGS = 0V level. In other words, the gate terminal will be set at lower and lower potential levels as compared to the source. In the figure, a negative voltage of 1V has been applied between the gate and source terminals for a low level of VDS. The effect of the applied negative-bias VGS is to establish depletion regions similar to those obtained with VGS =0V but at lower levels of VDS. The result of applying a negative bias to the gate is to reach the saturation level at a lower level of VDS. The resulting saturation level for ID has been reduced and in fact will continue to decrease as VGS is made more and more negative.

The notation of IDSS is derived from the fact that it is the Drain-to-Source current with a Short-circuit connection from gate to source. IDSS is the maximum drain current for a JFET and is defined by the conditions VGS = 0V and VDS > VP

9

10

The pinch-off voltage continues to drop in a parabolic manner as VGS becomes more and more negative. Eventually, VGS when VGS = -VP will be sufficiently negative to establish a saturation level that is essentially 0 mA, for all practical purposes the device has been turned off.

Example: N-Channel JFET characteristics with IDSS=8mA and Vp=-4V

Voltage-Controlled Resistor

previous slide The region to the left of the pinch-off locus is referred to as ohmic or voltage-controlled resistance region. In this region, the JFET can actually be employed as a variable resistor whose resistance is controlled by the applied gate-to-source voltage. Note that the slope of each curve and therefore the resistance of the device between drain and source for VDS < VP is a function of the applied voltage VGS. As VGS becomes more and more negative, the slope of each curve becomes more and more horizontal, corresponding with an increasing resistance level. The following equation will provide a good approximation to the resistance level in terms of the applied voltage VGS. Refer back to Fig. in

Where ro is the resistance with VGS = 0V and rd the resistance at a particular level of VGS. The level of VGS that results in ID = 0 mA is defined by VGS = VP with VP being a negative voltage for n-channel devices (and a positive voltage for p-channel JFETs).

11

Example: For an n-channel JFET with ro equal to 10 k (VGS =0V, VP= -6V), the above equation will result in 40 k at VGS = -3V.

12

p-Channel Devices The p-channel JFET is constructed in exactly the same manner as the n-channel device. The defined current directions are reversed as are the actual polarities for the voltage VGS and VDS.

Symbols

n-channel JFET The arrow is pointing in for n-channel device to represent the direction in which IG would flow if the p-n junction were forward-biased.

p-channel JFET The only difference in the symbol is the direction of the arrow.

For the p-channel device, the channel will be constricted by increasing positive voltages from gate to source and the double-subscript notation for VDS will result in negative voltages for VDS on the above output characteristics which has an IDSS of 6 mA and a pinch-off voltage of VGS = +6V. (The minus signs for VDS simply indicate that the source is at a higher potential than 13 the drain.)

14

SUMMARY (a) The maximum current is defined as IDSS and occurs when VGS = 0V and VDS|VP|. (b) For gate-to-source voltages VGS less than (more negative than) the pinch-off level, the drain current is 0A (ID=0A). (c) For all levels of VGS between 0V and the pinch-off level, the current ID will range between IDSS and 0A, respectively.

TRANSFER CHARACTERISTICS For the BJTs, the output current IC and input controlling current IB were related by beta. A linear relationship exists between IC and IB. Double the level of IB and IC will increase by a factor of two also. The above linear relationship does not exist between the output and input quantities of a JFET. The relationship between ID and VGS is defined by Shockleys equation. The squared term of the equation will result in a nonlinear relationship between ID and VGS, producing a curve that grows exponentially with decreasing magnitudes of VGS. DC analysis can be performed using a graphical approach and mathematical approach. Graphical approach is more direct and easier to apply. However, it require a plot of above equation to represent the device and a plot of the network equation relating the same variables. The solution is defined by the point of intersection of the two curves.

Note: For p-channel JFETs a similar list mentioned above can be developed.

15

16

The transfer characteristics defined by Shockleys equation are unaffected by the network in which the devices is employed.

If the relationship were linear, the plot of ID versus VGS would result in a straight line between IDSS and VP. However, a parabolic curve will result because the vertical spacing between steps of VGS on the drain characteristics decreases noticeably as VGS becomes more and more negative. Compare the spacing between VGS = 0 V and VGS = -1 V to that between VGS = -3 V and pinch-off. The change in VGS is the same but the resulting change in ID is quite different. A quick, efficient method of plotting ID versus VGS given only the levels of IDSS and VP and Shockleys equation. Applying Shockleys Equation Examining a few specific Levels. (i) VGS = 0 V

Obtaining transfer curve: When VGS = 0 V, ID = IDSS When VGS = VP, ID = 0 mA The transfer characteristics are a plot of an output current versus an input-controlling quantity. Therefore, there is a direct transfer from input to output variables.

17

18

(ii) VGS = VP

Using basic algebra, we can obtain an equation for the resulting level of VGS for a given level of ID.

(iii) Selected curve; ex. VGS = -1 V

We can test the above equation using the previous output characteristics.

Note the care taken with the negative signs for VGS and VP in the calculations above. The loss of one sign would result in a totally erroneous result. It should be obvious from the above that the level of ID can be found for any level of VGS.

19 20

Shorthand Method

(ii) If we choose ID=IDSS/2, we find that

Since the transfer curve must be plotted so frequently, it would be quite Advantageous to have a shorthand method for plotting the curve in the quickest, most efficient manner while maintaining an acceptable degree of accuracy. i) If we specify VGS to be one-half the pinch-off value VP, the resulting level of ID will be the following, as determined by Shockleys equation: As conclusion, the transfer curve can be sketched to a satisfactory level of accuracy simply using the four plot points.

The result specifies that the drain current will always be one-fourth of the saturation level IDSS as long as the gate-to-source voltage is one-half the pinch-off value.

21

22

Example (1): Sketch the transfer curve defined by IDSS = 12 mA and VP = - 6V. Solution: Four points;

Example (2): Sketch the transfer curve for a p-channel defined by IDSS = 4 mA and VP = 3V. Solution:

23

24

IMPORTANT RELATIONSHIP

DEPLETION-TYPE MOSFET Basic Construction

A slab of p-type material is formed from a silicon base and is referred to upon which the device will be constructed. In some cases the substrate is internally connected to the source terminal. However, many discrete devices provide an additional terminal labeled SS, resulting in a four-terminal device. The source and drain terminals are connected through metallic contacts to n-doped regions linked by an n-channel. The gate is also connected to a metal contact surface but remains insulated from the n-channel by a very thin silicon dioxide (SiO2) layer.

For the BJT configuration, IB is normally the first parameter to be determined. For the JFET, it is normally VGS.

25

SiO2 is a insulator: (i) Therefore, there is no direct electrical connection between the gate terminal and the channel of a MOSFET.

26

SiO2 is a insulator: (ii) Therefore, it construct very high input impedance of the device. Then it support the fact that the gate current (IG) is essentially zero amperes for dc-biased configuration. Metal-Oxide-Semiconductor FET or another name Insulated-Gate FET (IGFET) Metal: for the drain, source and gate connections to the proper surface- in particular the gate terminal and the control to be offered by the surface area of the contact. Oxide: Silicon dioxide insulating layer. Semiconductor: the basic structure on which the n- and p-type regions are diffused.

27

Basic Operation and Characteristics

The gate-to-source voltage VGS is set to zero volts by the direct connection from one terminal to the other and a voltage VDS is applied across the drain-to-source terminals. The results is an attraction for the positive potential at the drain by the free electrons of the n-channel and a current similar to that established through the channel of the JFET. In fact, the resulting current with VGS = 0V continues to be labeled IDSS.

28

Let set VGS to a negative voltage such as 1 V. The negative potential at the gate will tend to pressure electrons toward the p-type substrate (like charges repel) and attract holes from the p-type substrate (opposite charge attract). Depending on the magnitude of the negative bias established by VGS, a level of recombination between electrons and holes will occur that will reduce the number of free electrons in the n-channel available for conduction. The more negative the bias, the higher rate of recombination. The resulting level of drain current is therefore reduced with increasing negative bias for VGS.

29

30

For positive values of VGS, the positive gate will draw additional electrons (free carriers) from the p-type substrate and establish new carriers through the collisions resulting between accelerating particles. As the gate-to-source voltage, VGS continues to increase in the positive direction reveals that the drain current will increase at a rapid rate for the reasons listed above. The vertical spacing between the VGS = 0V and VGS = +1V curves is a clear indication of how much the current has increased for the 1 V change in VGS. Due to the rapid rise, the user must be aware of the maximum drain current rating since it could be exceeded with a positive gate voltage. As revealed above, the application of a positive gate-to-source voltage has enhanced the level of free carriers in the channel compared to that encountered with VGS =0V. For this reason, the region of positive gate voltages on the drain or transfer characteristics is often referred to as the enhancement region, with the region between cut-off and the saturation level of IDSS referred to as the depletion region.

Example (3): Sketch the transfer characteristics for an n-channel depletion type MOSFET with IDSS = 10 mA and VP = -4 V.

Solution

Mind that ID increases very rapidly with increasing positive values of VGS. In other words, be conservative with the choice of values to be substituted into Shockleys equation. In this case, we will try +1V as follows:

31

32

p-Channel Depletion Type MOSFET

The construction of a p-channel depletion type MOSFET is exactly the reverse of that n-channel depletion type MOSFET. There is now an n-type substrate and a p-type channel. The terminals remain as identified but all the voltage polarities and the current directions are reversed. VDS will have negative values and ID will have positive values since the defined direction is now reversed. The reversal in VGS will result in a mirror image for the transfer characteristics.

Symbols

The symbols chosen try to reflect the actual construction of the device. The lack of a direct connection (due to the gate insulation) between the gate and channel is represented by a space between the gate and the other terminals of the symbol. The vertical line representing the channel is connected between the drain and source and is supported by the substrate. Two symbols are provided for each type of channel to reflect the fact that in some cases the substrate is externally available while in Others it is not. For most of the analysis, the substrate and source will be connected and lower symbols will be employed.

33

34

ENHANCEMENT TYPE MOSFET

Although there are some similarities in construction and mode of operation between depletion-type and enhancement type MOSFET are quite different from anything obtained thus far. The transfer curve is not defined by Shockleys equation and the drain current is now cut off until the gate-to-source voltage VGS reaches a specific magnitude. Basic Construction of n-channel Enhancement type MOSFET A slab of p-type material is formed from a silicon base and is again referred to as substrate. Note here the absence of a channel between the two n-doped regions. This is the primary difference between the construction of depletion type and enhancement type MOSFETs.

35

Basic Operation and Characteristics

(i) VGS = 0 V and a voltage applied between the drain and source of the device, VDS will result in a current of effectively zero amperes. With VDS some positive voltage, VGS =0V and terminal SS directly connected to the source, there are in fact two reversebiased p-n junctions between the n-doped regions and the p-substrate to oppose any significant flow between the drain and source. (ii) Both VDS and VGS have been set at some positive voltage greater than 0V, establishing the drain and gate at a positive potential with respect to the source. The positive potential at the gate will pressure the holes in the p-substrate along the edge of the SiO2 layer to leave the area and enter deeper regions of the p-substrate. The result is a depletion region near the SiO2 insulating layer void of holes.

36

However, the electrons in the p-substrate (the minority carriers of the material) will be attracted to the positive gate and accumulate in the region near the surface of the SiO2 layer. The SiO2 layer and its insulating qualities will prevent the negative carriers from being absorbed at the gate terminal. As VGS increases in magnitude, the concentration of electrons near the SiO2 Surface increases until eventually the induced n-type region can support a measurable flow between drain and source. The level of VGS that results in the significant increase in drain current is called thethreshold voltage ,VT. On specification sheets it is referred to as VGS(Th). Since the channel is nonexistent with VGS = 0V and enhanced by the application of a positive gate-to-source voltage, this type of MOSFET is called an enhancement-type MOSFET. Both depletion and enhancement type MOSFETs have enhancement-type regions but the label was applied to the latter since it is its only mode operation. As VGS is increased beyond the threshold level, the density of free carriers in the induced channel will increase, resulting in an increased level of drain current. However, if we hold VGS constant and increase the level of VDS, the drain current will eventually reach a saturation level as occurred for the JFET and depletion type MOSFET. The leveling off of ID is due to a pinching-off process depicted by the narrower channel at the drain end of the induced 37 channel.

KVL to the terminal voltages of the MOSFET, we find that

If VGS is held fixed at some value such as 8 V and VDS is increased from 2 to 5 V, the voltage VDG will drop from 6 to 3 V and the gate will become less and less positive with respect to the drain. This reduction in gate-to-drain voltage VDG will in turn reduce the attractive forces for free carriers (electrons) in this region of the induced channel, causing a reduction in the effective channel width. Eventually, the channel will be reduced to the point of pinched-off and a saturation condition will be established. Any further increase in VDS at the fixed value of VGS will not affect the saturation level of ID until breakdown conditions are encountered. 38

The drain characteristics shown below reveal that at VGS = 8V, saturation occurred at a level of VDS = 6V. In fact, the saturation level for VDS is related to the level of applied VGS by Obviously, for a fixed value of VT, then the higher the level of VGS, the more the saturation level for VDS as shown by the locus of saturation levels. As the levels of VGS increased from VT to 8V, the resulting saturation level for ID also increased from a level of 0 to 10 mA. It is quite noticeable that the spacing between the levels of VGS increased as the magnitude of VGS increased, resulting in ever-increments in drain current.

For values of VGS less than the threshold level, the drain current of an Enhancement type MOSFET is 0 mA. For levels of VGS > VT, the drain current is related to the applied gate-to-source voltage by the following nonlinear relationship:

It is the squared term that results in the nonlinear relationship between ID and VGS.The term k is a constant that is a function of the construction of the device. The value of k can be determined from the following equation where ID(on) and VGS(on) are the values of each at a particular point on the characteristics of the device.

Ex: substituting ID(on) = 10mA when VGS(on) = 8V yields

39

40

10

A general equation for ID for the characteristics shown in the previous slide results in: Substituting VGS = 4V, we find that

Example (4): How to plot the transfer characteristics given the levels of k and VT as included below for a particular MOSFET:

First, a horizontal line is drawn at ID = 0 mA from VGS = 0V to VGS = 4V. Next, a level of VGS greater than VT such as 5 V is chosen.

At VGS = VT, the squared term is 0 and ID = 0mA Finally, additional levels of VGS are chosen and the resulting levels of ID obtained.

41

42

p-Channel Enhancement-Type MOSFETs

The construction of a p-channel enhancement-type MOSFETs is exactly the reverse of n-channel type. That is , there is now an n-type substrate and pdoped regions under the drain and source connections. All the voltage polarities and the current directions are reversed. The increasing levels of current resulting from increasing negative values of VGS.

Symbols

The symbols try to reflect the actual construction of the device. The dashed line between drain and source was chosen to reflect the fact that a channel does not exist between the two under no-bias conditions. It is, in fact, the only difference between the symbols for the depletion-type And enhancement-type MOSFETs.

43

44

11

Example (4): Given; VGS(on) = 10V will give ID (on) = 3 mA. VGS(Th) = 3V. Plot the transfer characteristics. SUMMARY

For

For VGS = 8, 10, 12, and 14 V, ID will be 1.525, 3 (as defined), 4.94 and 7.38 mA, respectively.

45

46

47

12

You might also like

- Sample Exercises Mat 181: (Answer)Document12 pagesSample Exercises Mat 181: (Answer)Nada AliaNo ratings yet

- Arrangement of Atoms in MetalsDocument12 pagesArrangement of Atoms in MetalsNada AliaNo ratings yet

- Granatum. Literature Survey Discover That Flavonoids Are Known To Possess Antioxidant andDocument1 pageGranatum. Literature Survey Discover That Flavonoids Are Known To Possess Antioxidant andNada AliaNo ratings yet

- Perfect Score SBP Fizik SPM 2011 QuestionDocument53 pagesPerfect Score SBP Fizik SPM 2011 QuestionSamion AwaldinNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Manual Controlador Factor Potencia 320Document15 pagesManual Controlador Factor Potencia 320Hector_Cornejo_5673No ratings yet

- 1Document40 pages1Vladimir BecejacNo ratings yet

- Iot Based Smart Solar Street Light Battery/Panel Fault DetectionDocument6 pagesIot Based Smart Solar Street Light Battery/Panel Fault DetectionEmmanuel AjibolaNo ratings yet

- EL7532 fn7435Document8 pagesEL7532 fn7435csclzNo ratings yet

- Chumbaka c520b Component ListDocument4 pagesChumbaka c520b Component ListSahrulRashidNo ratings yet

- Silicon NPN Triple Diffused: ApplicationDocument8 pagesSilicon NPN Triple Diffused: ApplicationMario Rosas VargasNo ratings yet

- 100 M0Document1 page100 M0felipeintegraNo ratings yet

- Electronic Slot Car Controller Mysteries Revealed - JayGee RacingDocument13 pagesElectronic Slot Car Controller Mysteries Revealed - JayGee RacingBeen DeeNo ratings yet

- BJT FundamentalsDocument33 pagesBJT FundamentalsSamreen ShabbirNo ratings yet

- Block Diagram of I.C. Timer (Such As 555) and Its WorkingDocument12 pagesBlock Diagram of I.C. Timer (Such As 555) and Its Workingkaran007_m100% (1)

- Z-Source Converters Overcome LimitationsDocument12 pagesZ-Source Converters Overcome Limitationsravirnjn88No ratings yet

- Sursa de Tensiune - DatasheetDocument2 pagesSursa de Tensiune - DatasheetAdrianaNo ratings yet

- LG W1941SDocument39 pagesLG W1941SGunvant K. BhopleNo ratings yet

- 555 Ignition Coil DriverDocument3 pages555 Ignition Coil Drivertim schroderNo ratings yet

- ED Lesson PlanDocument5 pagesED Lesson PlanGeetha MNo ratings yet

- BJT Gibert MultiplierDocument5 pagesBJT Gibert MultiplierJyoti GoyalNo ratings yet

- Locating Faults AG en US1Document3 pagesLocating Faults AG en US1Neelakandan MasilamaniNo ratings yet

- Open Elective BTech 2nd Yr 2023 24 v2Document19 pagesOpen Elective BTech 2nd Yr 2023 24 v2bhaivarun65No ratings yet

- L060 Push Pull (2UP)Document10 pagesL060 Push Pull (2UP)srikanthkmsNo ratings yet

- ETI 1978-12 DecemberDocument132 pagesETI 1978-12 DecemberCarlos Soares100% (1)

- Combiflex 1MRK 513 003 BENDocument28 pagesCombiflex 1MRK 513 003 BENRanjit RjtNo ratings yet

- Description: Technical DataDocument17 pagesDescription: Technical DataDhivya NNo ratings yet

- Implementation and Simulation of Half Bridge Series Resonant Inverter in Zero Voltage SwitchingDocument5 pagesImplementation and Simulation of Half Bridge Series Resonant Inverter in Zero Voltage Switchingwhite_lonelinessNo ratings yet

- SELECT RC102 ManualDocument2 pagesSELECT RC102 Manualabhaya2806No ratings yet

- BJM CORP ALL-TEST™ Tech Note: Trans01: Theme: Transformer Testing - 3 Phase TransformersDocument2 pagesBJM CORP ALL-TEST™ Tech Note: Trans01: Theme: Transformer Testing - 3 Phase TransformersvijaysatawNo ratings yet

- CBSE Sample Paper 2: General InstructionDocument9 pagesCBSE Sample Paper 2: General Instructionkg4freeNo ratings yet

- Written Report Transducers PDFDocument11 pagesWritten Report Transducers PDFJudy Ann Bernalte VargasNo ratings yet

- Ug1075 Zynq Ultrascale PKG Pinout PDFDocument234 pagesUg1075 Zynq Ultrascale PKG Pinout PDFanhxcoNo ratings yet

- IJPEM 1261129 1141Dec2011EnergyHarvesting PDFDocument14 pagesIJPEM 1261129 1141Dec2011EnergyHarvesting PDFChimzy IwumuneNo ratings yet

- MFJ 989D PDFDocument20 pagesMFJ 989D PDFLucian FaraonNo ratings yet