Professional Documents

Culture Documents

Electrostatic Discharge Sensitivity Measurement

Uploaded by

Nam Nguyễn HữuOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electrostatic Discharge Sensitivity Measurement

Uploaded by

Nam Nguyễn HữuCopyright:

Available Formats

AN1181 APPLICATION NOTE

ELECTROSTATIC DISCHARGE SENSITIVITY MEASUREMENT

by Microcontroller Division Applications

This application note describes a procedure for determining the susceptibility of microcontroller devices to ESD damage.

1 REFERENCE DOCUMENTS

1.1 REFERENCE DOCUMENTS (INTERNAL ST REFERENCES)

s s

0061692 "Reliability Test Specification for Product Qualification" SOP2614 "Reliability Procedure for Product Qualification"

1.2 OTHER REFERENCES

s s s

CDF-AEC-Q100-002 "Human Body Model ESD test" CDF-AEC-Q100-003 "Machine Model ESD test" ESD Association standard draft DS5.3 - 1993 Draft Standard for ESD sensitivity textCharged Device Model (CDM) Component Testing ESD Association standard draft DS5.3.1 - 1996 Charged Device Model (CDM) NonSocketed Mode JEDEC STANDARD JESD22-C101 "Field- induced Charged Device Model" JEDEC STANDARD JESD22-A114A "Human Body Model" JEDEC STANDARD JESD22-A115A "Machine Model" ESD Association standard draft DS5.2 - 1996 "Machine Model" ESD Association Standard ESD STM 5.1 - 1998 "Human Body Model" EIAJ Provisional Standard EDX-4702 "Charged Device Model"

s s s s s s

AN1181/0100

1/7

ELECTROSTATIC DISCHARGE SENSITIVITY MEASUREMENT

2 DEFINITIONS

DUT (Device under test): a product evaluated for its sensitivity to ESD ESD (Electrostatic discharge): the transfer of electrostatic charge between bodies at different electrostatic potentials Electrostatic Discharge Sensitivity: an ESD voltage level which causes part failure ESD simulator: an instrument that simulates the models described in this specification Human Body Model (HBM) ESD: an ESD pulse simulating the human body discharge to a device Machine Model (MM) ESD: an ESD pulse approximating a pulse from a machine or mechanical equipment Maximum Withstanding Voltage: the maximum ESD voltage at which the product passes the failure criteria requirements specified in Section 4. PUT: pin under test Non-supply Pins: all input, output, bi-directional and clock pins except power pins and non connected pins. Power Pins all power supply, external voltage source and ground pins Like-named Power Pins: Power Pins with similar names and functions. i.e. VDD1 - VDD2, VCC1 - VCC2, GND1 - GND2. Ringing current: the damped high frequency current oscillation usually following the pulse rise time

3 GENERAL

s s s

ESD pulse simulator and DUT For HBM see FIGURE 1 For MM see FIGURE 2

3.1 MEASUREMENT EQUIPMENT 3.1.1 For HBM and MM An oscilloscope and current probe with a minimum bandwidth of 350 MHz. Maximum cable length of current probe is 1 meter. Evaluation loads: a) low inductance, 1000 Volt, 500 ohm +/- 1% sputtered film resistor b) tinned copper shorting wire

2/7

ELECTROSTATIC DISCHARGE SENSITIVITY MEASUREMENT

3.2 EQUIPMENT QUALIFICATION Must be performed during initial testing for equipment acceptance, after repairs that may affect the waveform and at least once per year, unless different recommendation from Tester Supplier. For HBM and MM the tester must meet the requirements of TABLE 1 and TABLE 2 at all voltage levels on the highest pin count test socket with both the shorting wire and 500 load. 3.3 WAVEFORM VERIFICATION Must be performed every 6 months as a minimum. For CDM the use of 1GHz oscilloscope is allowed.

4 PROCEDURE

All units must be tested per applicable Data Sheet (Static and dynamic parameters). Sample size according to spec. 0061692 for HBM and MM, minimum sample size 3 devices. For HBM and MM each sample shall be stressed at one voltage level using all pin combinations specified in TABLE 3, applying 3 positive and 3 negative pulses for each pin combination, unless different requirements in the detail specification. Minimum time between pulses is 1 second. Note A: for HBM and MM under responsibility of the involved Product Group Q&R Dept. following derogations may be applied in agreement with ESD Associations Standard ESD STM5.1 1998 (February 1998) and JEDEC Standard JESD22- A114A and JEDEC Standard JES22 - A 115 A applying one positive and one negative pulse for each pin combination, unless different requirements in the detailed specification. If more than one pulse is requested, minimum time between pulses is 500 milliseconds. Note B: For HBM and MM 3 new components may be used at each voltage level or pin combination if desired. This will eliminate any step stress hardening effect, and will reduce the possibility of early failure due to cumulative stress on power pins. However, if a single set of 3 components are stressed at each level, then to avoid missing possible ESD vunerability windows, it is recommended not to miss any stress step. Failure criteria: A product passes a voltage level if all units stressed at that voltage level pass. A unit will be defined as a failure if, after exposure to ESD pulses, it no longer meets the data sheet requirements (static and dynamic parameters). Note : Cumulative damage effects may be eliminated by retesting at the failure voltage step using a new sample.

3/7

ELECTROSTATIC DISCHARGE SENSITIVITY MEASUREMENT

Table 1. Waveform Specification For Human Body Model Voltage level (V) 1000.00 2000.00 4000.00 8000.00 Ipeak for Ipeak for Rise Time Rise Time Decay Time for Short Ips 500 * for Short tr for 500* trr Short td (ns) (A) Ipr(A) (ns) (ns) 0.6-0.74 .375-.55 2-10 5-25 130-170 1.2-1.48 NA 2-10 NA 130-170 2.4-2.96 NA 2-10 NA 130-170 4.8-5.92 NA 2-10 NA 130-170 Ringing Current IR (A) 15% of Ips and Ipr 15% of I ps and Ipr 15% of I ps and Ipr 15% of I ps and Ipr

* The 500 load is used only during Equipment Qualification as specified in Section 3.2 Table 2. Waveform Specification For Machine Model Voltage Leve (V) 200 400 Positive First Major Pulse Positive First Positive Second Current at 100ns Peak Current Period for Peak CurPeak Current for for 500* I100 for Short, Ips1 Short, tpm rent for (A) Short, Ips2 (A) (A) (ns) 500* Ipr (A) 67% to 90% of 2.8-3.8 66-90 NA NA Ips1 67% to 90% of 66-90 0.85 to 1.2 0.29 10% 5.8-8

Ips1

* The 500 load is used only during Equipment Qualification as specified in Section 3.2 Table 3. Pin Combinations For Integrated Circuits (HBM and MM) Pin combina- Connect Individually to Tertion minal A 1 Connect Individually Floating Pins (unconnectto Terminal B ed) (Ground) All pins except PUT and first power pin(s) All pins except PUT and second power pin(s) All pins except PUT and Nth power pin(s) All power pins All pins not under test and all power pins

3 4 5*

All pins one at a time, except the pin(s) connected to Ter- First power pin(s) minal B All pins one at a time, except the pin(s) connected to Ter- Second power pin(s) minal B All pins one at a time, except the pin(s) connected to TerNth power pin(s) minal B All other Non-supply Each Non-supply pin pins except PUT Each corresponding Each Inverting input pin Non-inverting pin

* For Integrated Circuits with operational amplifier functions

4/7

ELECTROSTATIC DISCHARGE SENSITIVITY MEASUREMENT

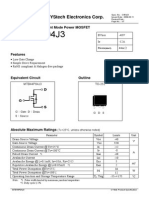

Figure 1. Typical Equivalent HBM ESD Circuit

R1

S1

1500 ohm Terminal A

High Voltage Pulse Generator C1 DUT 100 pF S2 socket short R2

Terminal B

500 ohm

Notes: The performance of any simulator is influenced by its parasitic capacitance and inductance. Precautions must be taken in tester design to avoid recharge transients and multiple pulses. R2, used for Equipment Qualification as specified in Section 3.2 shall be a low inductance, 1000 Volts, 500 resistor with 1% tolerance. Piggybacking of DUT sockets is permitted if waveform in socket is within spec limits. Reversal of terminals A and B to achieve dual polarity is not permitted. S2 should be closed 10 to 100 milliseconds after the pulse delivery period to ensure the DUT socket is not left in charge state. S2 should be opened at least 10 milliseconds prior to the delivery of the next pulse.

5/7

ELECTROSTATIC DISCHARGE SENSITIVITY MEASUREMENT

Figure 2. Typical Equivalent MM ESD Circuit

S1

Terminal A

High Voltage Pulse Generator C1 DUT 200 pF S2 socket short R2 500 ohm R1 Terminal B

10 K to 10 M

ohm

Note: The performance of any simulator is influenced by its parasitic capacitance and inductance. Resistor R1, in series with switch S2, ensures a slow discharge of the device. Precautions must be taken in tester design to avoid recharge transients and multiple pulses. R2, used for Equipment Qualification as specified in Section 3.2 shall be low inductance, 1000 Volts, 500 resistor with 1% tolerance. Piggybacking of DUT sockets is permitted if waveform in socket is within spec limits. Reversal of terminals A and B to achieve dual polarity is not permitted. S2 should be closed 10 to 100 milliseconds after the pulse delivery period to ensure the DUT socket is not left in charge state. S2 should be opened at least 10 milliseconds prior to the delivery of the next pulse.

6/7

ELECTROSTATIC DISCHARGE SENSITIVITY MEASUREMENT

"THE PRESENT NOTE WHICH IS FOR GUIDANCE ONLY AIMS AT PROVIDING CUSTOMERS WITH INFORMATION REGARDING THEIR PRODUCTS IN ORDER FOR THEM TO SAVE TIME. AS A RESULT, STMICROELECTRONICS SHALL NOT BE HELD LIABLE FOR ANY DIRECT, INDIRECT OR CONSEQUENTIAL DAMAGES WITH RESPECT TO ANY CLAIMS ARISING FROM THE CONTENT OF SUCH A NOTE AND/OR THE USE MADE BY CUSTOMERS OF THE INFORMATION CONTAINED HEREIN IN CONNEXION WITH THEIR PRODUCTS."

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of STMicroelectronics. The ST logo is a registered trademark of STMicroelectronics 2000 STMicroelectronics - All Rights Reserved. Purchase of I2C Components by STMicroelectronics conveys a license under the Philips I2C Patent. Rights to use these components in an I2C system is granted provided that the system conforms to the I2C Standard Specification as defined by Philips. STMicroelectronics Group of Companies Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain Sweden - Switzerland - United Kingdom - U.S.A. http://www.st.com

7/7

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Major Changes For 2020 NECDocument7 pagesMajor Changes For 2020 NECLCDpanelNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- VT Sizing Calculation For 132 KV Cable Feeder: Page 1 of 8Document8 pagesVT Sizing Calculation For 132 KV Cable Feeder: Page 1 of 8Chilukuri Jithendra100% (1)

- Common Mistakes in Electrical Wiring PracticeDocument37 pagesCommon Mistakes in Electrical Wiring PracticeSanda Kinithi100% (1)

- The 555: A Versatile Timer (Marston)Document8 pagesThe 555: A Versatile Timer (Marston)jimdigriz100% (1)

- Technical Spesification of Distribution Transformer 33/0.416 KVDocument14 pagesTechnical Spesification of Distribution Transformer 33/0.416 KVAhmed Ja100% (1)

- Installation Manual Solar Controller PDFDocument11 pagesInstallation Manual Solar Controller PDFLhenzCNo ratings yet

- Siemens MotorsDocument105 pagesSiemens MotorsAhmed M.FarahatNo ratings yet

- Liebert Iton: I S I SDocument2 pagesLiebert Iton: I S I SnammarisNo ratings yet

- N Din To64 Rfi Ing PDFDocument4 pagesN Din To64 Rfi Ing PDFshekooferiahiNo ratings yet

- MLC Capacitor Catalogue-221392Document55 pagesMLC Capacitor Catalogue-221392pinheiroNo ratings yet

- T8500CT0601EPR4 - TeSys Essential Guide 2013 LRDocument46 pagesT8500CT0601EPR4 - TeSys Essential Guide 2013 LRCbdtxd PcbtrNo ratings yet

- B44P04Document7 pagesB44P04aldo_suviNo ratings yet

- Solar PV1 F Cable Technical Data SheetDocument1 pageSolar PV1 F Cable Technical Data SheetKelvin ChngNo ratings yet

- Switched Reluctance Motor (SRM)Document8 pagesSwitched Reluctance Motor (SRM)Ömer Faruk AbdullahNo ratings yet

- CTEK 250 Dual ManualDocument24 pagesCTEK 250 Dual ManualGeorgeNo ratings yet

- The Multi-TesterDocument34 pagesThe Multi-TesterDianarra VergaraNo ratings yet

- Left LegendDocument2 pagesLeft Legendmugenyi rashidNo ratings yet

- Power Thyristor Data SheetsDocument72 pagesPower Thyristor Data SheetsArt Del R SalongaNo ratings yet

- 8DJH Produktblatt EN Screen PDFDocument2 pages8DJH Produktblatt EN Screen PDFHung Cuong PhamNo ratings yet

- DistributionSystem SinglePhaseTransformerDocument5 pagesDistributionSystem SinglePhaseTransformerReparrNo ratings yet

- CR3CM Ac03Document4 pagesCR3CM Ac03Hanif Rathore PrinceNo ratings yet

- Musical Siren Lab Project ReportDocument8 pagesMusical Siren Lab Project ReportMahipal_Singh_Deora100% (3)

- ETS12-01-03 - Limiting Fuse Link For Oil SwitchgearDocument12 pagesETS12-01-03 - Limiting Fuse Link For Oil SwitchgearTerex14253No ratings yet

- PC-EE-591 - Virtual LabDocument2 pagesPC-EE-591 - Virtual LabkbhowalNo ratings yet

- A Brief Review of PLN DISTRIBUTION SYSTEM PDFDocument30 pagesA Brief Review of PLN DISTRIBUTION SYSTEM PDFRavi BhandariNo ratings yet

- Djatiroto - Motor 950kWDocument2 pagesDjatiroto - Motor 950kWandrieysyah2525No ratings yet

- ARC 630i: MMA Welding With Long Lead and Arc GougingDocument2 pagesARC 630i: MMA Welding With Long Lead and Arc GougingBeshoy RedaNo ratings yet

- Catalogo Luces R M BZ 3 PDFDocument3 pagesCatalogo Luces R M BZ 3 PDFCesarLimaNo ratings yet

- AUXILIARES, SINALIZAÇÃO E RELÉ DE DISPARO RXMS-1, RXMA-1 e Etc 508015 (EN) PDFDocument20 pagesAUXILIARES, SINALIZAÇÃO E RELÉ DE DISPARO RXMS-1, RXMA-1 e Etc 508015 (EN) PDFleonardoNo ratings yet

- Oleveon 236 E PC INOX: Offer Text Product Features and Key DataDocument1 pageOleveon 236 E PC INOX: Offer Text Product Features and Key Dataahmed saberNo ratings yet