Professional Documents

Culture Documents

Design of Low Power Column Bypass Multiplier Using FPGA

Uploaded by

Nsrc Nano ScientifcOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design of Low Power Column Bypass Multiplier Using FPGA

Uploaded by

Nsrc Nano ScientifcCopyright:

Available Formats

Design of Low Power Column Bypass Multiplier using FPGA

AIM: The main aim of the project is to design and implement Design of Low Power Column Bypass Multiplier using FPGA. AB !"AC!: It is well known that multipliers consume most of the power in DSP computations. Hence, it is very important for modern DSP systems to develop low power multipliers to reduce the power dissipation.. In this paper, we presents low power !olumn "ypass multiplier design methodology that inserts more num"er of #eros in the multiplicand there"y reducing the num"er of switching activities as well as power consumption. The switching activity of the component used in the design depends on the input "it coefficient. This means if the input "it coefficient is #ero, corresponding row or column of adders need not "e activated. If multiplicand contains more #eros, higher power reduction can "e achieved. To reduce the switching activity is to shut down the idle part of the circuit, which is not in operating condition. $se of look up ta"le is an added feature to this design. %urther low power adder structure reduces the switching activity. %le&i"ility is another critical re'uirement that mandates the use of programma"le components like %P()s in such devices.

Propose# met$o#:

V.Mallikarjuna (Project manager)

ISO: 9001- 2008 CERTIFIED COMPANY

Na'()r

Mobile No: +91-8297578555. Branch !: "#$ ra%a$ &

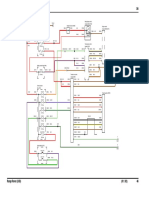

In this paper we can replace the adder with *+, and -+, compressor. )nd modify this multiplier with pipeline architecture. .hich will reduce the area , power and delay BL%C& DIAG"AM:

%ig+ ) */* multiplier structure.

!%%L : 0ilin& 1.,IS2, 3odelsim 4.*c. APPLICA!I%' AD(A'!AG) :

V.Mallikarjuna (Project manager) Mobile No: +91-8297578555. Branch !: "#$ ra%a$ &

ISO: 9001- 2008 CERTIFIED COMPANY

Na'()r

In this paper we have presented a new methodology for designing of low power parallel multiplier with reduced switching. !ompared with the row "ypassing or array multipliers, we can prove that our proposed low power multiplier achieves higher power reduction with lower hardware overhead. ")F)")'C) : 5scal T. !. !hen, Sandy .ang, and 6i .en .u, .3inimi#ation of Switching )ctivities of Partial Products for Designing 7ow Power 3ultipliers., IEEE Transactions on VLSI Systems, vol. 88, no. -. 9ajendra 3. Patrikar, :. 3urali, 7i 2r Ping, .Thermal distri"ution calculations for "lock level placement in em"edded systems., Microelectronics Reliability **;,<<*= 8,1 8-* Hichem >elhadj, >ehroo# ?ahiri, )l"ert Tai .Power sensitive design techni'ues on %P() devices, Proceedings of International conference on IC Taipai. ). .u, .High performance adder cell for low power pipelined multiplier , in Proc. IEEE Int. Symp. on Circuits and Systems, vol. *, pp. @A 4<. S. Hong, S. :im, 3.!. Papaefthymiou, and ..2.Stark, .7ow power parallel multiplier design for DSP applications through coefficient optimi#ation , in Proc. of T elft! "nnual IEEE Int. "SIC#S$C onf., pp. ,B4 ,1<.

V.Mallikarjuna (Project manager)

ISO: 9001- 2008 CERTIFIED COMPANY

Na'()r

Mobile No: +91-8297578555. Branch !: "#$ ra%a$ &

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- One Manual P1 8-2Document62 pagesOne Manual P1 8-2Bebliuc AlexNo ratings yet

- SLT Replication TechonologyDocument53 pagesSLT Replication TechonologyKoushik Pal100% (1)

- Occ CompleteDocument25 pagesOcc CompleteMayur Mestry100% (1)

- How To Cluster Odoo 12 With PostgreSQL Streaming Replication For High Availability - SeveralninesDocument13 pagesHow To Cluster Odoo 12 With PostgreSQL Streaming Replication For High Availability - SeveralninesIdris IdrisNo ratings yet

- Ipf Troubleshooting GuideDocument173 pagesIpf Troubleshooting GuideSpy Ball100% (2)

- Conmed System 2450 Manual de ServicioDocument36 pagesConmed System 2450 Manual de ServicioAnonymous zt7KHu100% (8)

- Igs NT Gecon Marine SPTM 3 2Document228 pagesIgs NT Gecon Marine SPTM 3 2foroNo ratings yet

- Arithmetic Logic UnitDocument5 pagesArithmetic Logic UnitNarendra AchariNo ratings yet

- Ramdump Modem 2021-03-20 17-17-18 PropsDocument11 pagesRamdump Modem 2021-03-20 17-17-18 PropsДенис ФеофанычNo ratings yet

- Regin Regio Midi EngDocument2 pagesRegin Regio Midi EngMc EswaranNo ratings yet

- Matching in Analog Integrated Circuits: Viswakiran Popuri 10/28/2009Document9 pagesMatching in Analog Integrated Circuits: Viswakiran Popuri 10/28/2009Mahesh Gowtham Reddy NNo ratings yet

- Automatic TransmissionDocument5 pagesAutomatic Transmissionolyga mgolNo ratings yet

- Bba 1003Document2 pagesBba 1003api-3782519No ratings yet

- Vlan-Rutas EstaticasDocument5 pagesVlan-Rutas EstaticasJuan CarlosNo ratings yet

- 4IT1 01R Rms 20190822Document24 pages4IT1 01R Rms 20190822Shehan MorawakaNo ratings yet

- Common Clock (SRAN16.1 02)Document83 pagesCommon Clock (SRAN16.1 02)VVL0% (1)

- Biostar A78dg-A2t Rev 6.0 SCHDocument46 pagesBiostar A78dg-A2t Rev 6.0 SCHИван ИвановNo ratings yet

- DA - Intake Air Temperature (IAT) Sensor - Pinpoint Test (Computers and Control Systems) - ALLDATA RepairDocument6 pagesDA - Intake Air Temperature (IAT) Sensor - Pinpoint Test (Computers and Control Systems) - ALLDATA RepairJesus SanchezNo ratings yet

- 12 Memory 3Document15 pages12 Memory 3max scalomNo ratings yet

- Sai Vidya Institute of Technology: Course: 15ec663 - Digital System Design Using VerilogDocument27 pagesSai Vidya Institute of Technology: Course: 15ec663 - Digital System Design Using VerilogShivaprasad B KNo ratings yet

- ??????? ??? ?????? ?? ???????? ???????? ????? ?????Document206 pages??????? ??? ?????? ?? ???????? ???????? ????? ?????Abhishek MishraNo ratings yet

- Cloud Backup: Set-And-Forget Cost-Efficient Backups For ONTAP Data Wherever It LivesDocument1 pageCloud Backup: Set-And-Forget Cost-Efficient Backups For ONTAP Data Wherever It LivesDiego Donoso PayneNo ratings yet

- Things To Know : Instruction Format Instructions Can Have 1, 2 or No OperandsDocument9 pagesThings To Know : Instruction Format Instructions Can Have 1, 2 or No OperandsMS. AYESHA SIDDIKA TONNYNo ratings yet

- SKR4307-Mobile Application: Lab 3b - Android ServiceDocument6 pagesSKR4307-Mobile Application: Lab 3b - Android ServiceAisya ZuhudiNo ratings yet

- 18 DiplexorDocument3 pages18 DiplexorFernando GutiérrezNo ratings yet

- 12 December 1960Document68 pages12 December 1960dusan.papez9216No ratings yet

- Global Flexible Power SolutionsDocument8 pagesGlobal Flexible Power SolutionsTBS Máy Phát ĐiệnNo ratings yet

- CS1354Document6 pagesCS1354Manoj BhoyeNo ratings yet

- ITU T A5 TD New G.1028.2Document7 pagesITU T A5 TD New G.1028.2Dana AlhalabiNo ratings yet

- Final Mad-Unit-4Document69 pagesFinal Mad-Unit-4Pooja jadhavNo ratings yet