Professional Documents

Culture Documents

An 369

Uploaded by

mailmanager8946Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

An 369

Uploaded by

mailmanager8946Copyright:

Available Formats

AES3/EBU Reference Design

Version 1.1, February 2005

Application Note

Introduction

The Audio Engineering Society and the European Broadcasting Union developed the AES3/EBU digital audio transmission standard. AES3/EBU is a serial point-to-point interface that carries digital audio data over a standard cable. Audio data is typically in pulse code modulation (PCM) format. The reference design also supports compressed audio and non-audio data transmission. The information sent over the AES3/EBU is (non-return to zero) NRZ coded with the BPM (bi-phase mark code) so clock and data can be recovered on the receive side of the interface. The AES3/EBU reference design provides both a transmitter and a receiver. The receiver extracts the data and the clock from an incoming AES3/EBU stream and stores the parallel audio data and control bits into a FIFO buffer. The received information can be extracted from the FIFO buffer for processing, or sent directly to the transmitter. The AES3/EBU nominal data rate is directly related to the source audio sample rate. The receiver's input data rate is set at compile time to a fixed frequency, supporting PCM sample rates up to 192 kHz. The transmitter takes parallel data from a FIFO buffer, performs serialization, parity bit generation, bi-phase coding, and appends the appropriate X,Y, Z header. It performs null-packet stuffing when no audio data is present in the transmit FIFO buffer. The transmit clock may be derived from an asynchronous source or it may be locked to an extracted receive clock via an external voltage-controlled crystal oscillator (VCXO). Altera supplies the AES3/EBU reference design as Verilog HDL source code. The reference design includes transmit and receive blocks, testbenches, which allow you to test the Verilog HDL source code, Quartus II implementation constraints, and demonstrations that run on Altera Stratix GX and Cyclone Video Demonstration Boards.

For more information on the Stratix GX Video Demonstration Board see the Stratix GX Video Demonstration Board Data Sheet; for more information on the Cyclone Video Demonstration Board see the Cyclone Video Demonstration Board Data Sheet. The reference design can also address the Sony/Philips digital interface (S/PDIF), if the electrical interface for S/PDIF is adhered to.

Altera Corporation AN-369-1.1

1 Preliminary

AES3/EBU Reference Design

For S/PDIF, some differences exist in the interpretation of the channel status block registers, but the reference design needs no changes for S/PDIF.

This application note includes the following topics:

Functional Description on page 3 Getting Started on page 16

Features

AES3/EBU transmit and receive functionality Control channel status block capture on the receiver Control channel status block insertion for the transmitter Hardware cyclic redundancy code (CRC) checking on the receiver Hardware CRC generation on the transmitter S/PDIF compatibility

2 Preliminary

Altera Corporation

Functional Description

Functional Description

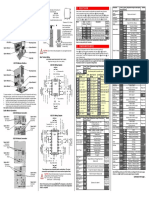

Figure 1. Block Diagram

Figure 1 shows the reference design block diagram.

Stratix or Cyclone Device 27-MHz Clock PLL Five-Times Oversample

FIFO Buffer 192 Channel Status User Bit Validity Bit 24 24 Stratix GX Video Development Board only, e.g., for digital audio reference signal (DARS) implementation VCXO Control Registers PLL Audio Left Audio Right Request Left Request Right 6.144 MHz 24 24 AES3 Transmitter AES3/EBU Out

AES3/EBU In

AES3 Receiver

27 MHz VCXO MK2069

Altera Corporation

3 Preliminary

AES3/EBU Reference Design

The AES3/EBU reference design comprises the following elements:

AES3/EBU transmitter AES3/EBU receiver PLL for the system clock (derived from 27 MHz) PLL to derive the transmit clock from the VCXOs 27-MHz output, if a lock to the receive clock is needed, (Stratix GX Video Demonstration Board only)

Table 1 shows the reference design signals.

Table 1. Signals Name

clk_in reset_n aes_in aes_out aes_clk_out (1) mk2064_rv (1) mk2064_clrn (1) mk2064_fv (1) mk2064_sv (1) mk2064_ld (1) ics660_sel (1) ddr_clk_fb_in (1) ddr_clk_fb_out (1) vcxo_out (1) pll_locked (1) ld_led

Note to Table 1:

(1) Stratix GX Video Demonstration Board demonstration only..

Required

Yes Yes Yes Yes No No No No No No no No No No Yes Yes

Direction

Input Input Input Output Output Output Output Output Output Output Output Input Output Output Output Output System clock.

Description

Asynchronous reset (active low). AES3/EBU input. AES3/EBU output. AES3/EBU recovered clock. Control VCXO divider on the Stratix GX Video Demonstration Board. Clear VCXO on the Stratix GX Video Demonstration Board. Control VCXO divider on the Stratix GX Video Demonstration Board. Control VCXO divider on the Stratix GX Video Demonstration Board. Control VCXO on the Stratix GX Video Demonstration Board. Bypass divider on the Stratix GX Video Demonstration Board. To access enhanced PLL (re-using DDR PLL on the Stratix GX Video Demonstration Board). To access enhanced PLL (re-using DDR PLL on the Stratix GX Video Demonstration Board). To access enhanced PLL (re-using DDR PLL on the Stratix GX Video Demonstration Board). PLL lock status. Check status.

4 Preliminary

Altera Corporation

Functional Description

Receiver

Figure 2 shows the receiver. Figure 2. AES3/EBU Receiver

Five-Times Oversample Receiver Clock 192 AES3/EBU In 8 Deserializer Word Aligner Formatter 24 Audio Left 24 Audio Right Validity Bit User Data Bit Parity Bit Check Channel Status Block

Channel Status Data CRCC Check

The receiver comprises the following elements:

Deserializer Word aligner Formatter (to re-construct frames) Parity check CRC check

Table 2 shows the receiver signals.

Table 2. Receiver Signals (Part 1 of 2) Name

clk_rx reset_n aes_in rxclk_out channel_left[27:0] channel_right[27:0] wrusedw[3:0] oe reset_fifo

Direction

Input Input Input Output Output Output Input Output Output Receiver reset (active low). AES3/EBU input. Recovered clock output.

Description

Five-times oversample receiver clock.

Recovered audio and control signals (left channel). Recovered audio and control signals (left channel). FIFO buffer level. Enables the transmit module when ready. Resets FIFO buffer when re-synchronization is in progress.

Altera Corporation

5 Preliminary

AES3/EBU Reference Design

Table 2. Receiver Signals (Part 2 of 2) Name

wreq_sig_a wreq_sig_b

Direction

Output Output

Description

Write request signal (left channel) for the FIFO buffer. Write request signal (right channel) for the FIFO buffer.

Deserializer

The serial data stream from the LVDS input buffer is oversampled using a local asynchronous clock and converted into a parallel 8-bit word. The rxclk_out signal is generated to determine when the 8-bit word is available. Because of the nature of the digital oversampling algorithm, this clock may exhibit a large amount of jitter. In applications that need a low jitter recovered clock, the rxclk_out signal may be fed through an external VCXO to remove the jitter caused by resample block. 1 In the Stratix GX video demonstration board demonstration, the rxclk_out signal is sent through a VCXO to clean the jitter caused by the oversampling and to allow the transmitter to be locked to the receiver. When the AES3/EBU receiver or transmitter are used independently the system does not require a VCXO.

You can use the output of the VCXO to lock all the AES3/EBU outputs to this AES3/EBU input. Jitter is usually expressed in unit interval (UI), and in the reference design the UI is calculated using the following equation: 1UI = 1/(48,000 Hz 2 32 bit frame 2 bit per sample) = 163 ns The AES3/EBU receiver has been tested against the AES3/EBU standard receiver jitter tolerance mask. The receiver reliably captures data at input jitter levels slightly greater than the maximum specification (see Figure 3).

6 Preliminary

Altera Corporation

Functional Description

Figure 3. Receiver Jitter Tolerance

Figure 4 shows the jitter transfer of the complete system (receiver and transmitter) with a VCXO to smooth the recovered receive clock.

Altera Corporation

7 Preliminary

AES3/EBU Reference Design

Figure 4. JitterWith the VCXO

The red line shows the jitter transfer mask, and the other two responses are the jitter transfer of the entire system with two different oversampling rates. The blue response represents the jitter transfer using the five-times oversampling scheme; the green response shows the same jitter transfer but running a 15-times oversampling scheme. These two cases both pass the jitter transfer mask, and also show the influence of the oversampling frequency on clocking the transmitter. The five times oversampling scheme can be more advantageous because the clocking frequency is lower, but this example shows that higher oversample rates can provide alternative jitter characteristics across the frequency spectrum.. 1 To change the oversampling frequency, you need to change the SAMPLE_INTERVAL in the file aes_rxsample.v, and change the PLL MegaWizard Plug-In set -up (aes_pll.v for the Sratix GX Video Demonstration Board and aes_demo_cvdb.v for the Cyclone Video Demonstration Board) The jitter transfer function depends on the final applications specific VCXO device.

8 Preliminary

Altera Corporation

Functional Description

Figure 5 shows the jitter transfer of the complete system (receiver and transmitter) without a VCXO. Figure 5. JitterWithout the VCXO

The red line shows the jitter transfer mask as specified in the standard. The other two responses being the jitter transfer of the entire system in two slightly different configurations. The blue response represents the jitter transfer using the five times oversampling scheme and the green response shows the same jitter transfer when using a 15-times oversampling scheme. The difference in the two responses illustrates the influence of the oversampling function on the jitter transfer when different oversampling frequencies are used. In this example, the jitter transfer does not pass the AES3/EBU jitter transfer mask, because the system does not use any jitter filtering mechanism such as a VCXO. This configuration shows the receiver jitter tolerance is met and the audio samples can be received reliably. Only when the system has to retransmit using a recovered receive clock is a jitter attenuation mechanism needed. For example, for four AES3/EBU inputs, one input can use a VCXO to cancel out most of the jitter for a clean receive clock. The other inputs can use this clean receive clock, as a reference (audio clock) acting like a DARS input for the system. Figure 6 show the eye diagram with the VCXO; Figure 7 shows the eye diagram without the VCXO.

Altera Corporation

9 Preliminary

AES3/EBU Reference Design

Figure 6. Eye PatternWith the VCXO

Note (1)

Note to Figure 6:

(1) The red line shows the AES3 limits; the blue and green lines show the eye pattern.

10 Preliminary

Altera Corporation

Functional Description

Figure 7. Eye PatternWithout the VCXO

Note (1)

Note to Figure 7:

(1) The red line shows the AES3 limits; the blue and green lines show the eye pattern.

Receive data is oversampled using an internal PLL clock that is set to approximately 5 times the AES3/EBU data rate. For an audio sample rate of 48 kHz, the sample rate is: 5 48,000 Hz 32 bits per channel 2 channels 2 (bi-phase coding) = 30.72 MHz A 5-times oversampling scheme implements data recovery and bit synchronization, which corresponds to a sampling rate of 30.72 MHz. The deserializer provides a fixed frequency sampling of the serial data. Approximately 5 samples are taken for each bit. These samples are accumulated by the deserializer and passed to the oversampling interface in a parallel format. Logic extracts the data from the sets of samples generated by the deserializer. Firstly, the transition points within the received word are determined. These transition points determine the best sample to extract for each data bit. The logic continuously realigns to the transition points in the incoming data, and can therefore adapt to a frequency mismatch between the sampling clock and the incoming data rate. The extracted samples for each data bit are accumulated into a parallel word for processing by the deserializer.

Altera Corporation

11 Preliminary

AES3/EBU Reference Design

Figure 8 shows the 5-times oversampling scheme. Figure 8. Oversampling Scheme

5-Times Oversample Clock Data Sample Extracted Bit 011111000001111111111000000000 1 0 1 1 0 0

Transistion Detected No Transistion Detected (bit extraction based on position relative to previous sample)

Word Aligner

The word aligner scans the incoming data until it finds the Z preamble that indicates the beginning of a status block.

Formatter

The formatter reconstructs the AES3 frame, re-synchronises the channel status block when the AES3 input is un-plugged, and stores the 192 bits of the channel status structure for monitoring. A parity check is also performed on the AES3 input and compared with the parity bit in the AES3 stream. The CRC check is also performed on the channel status structure and compared to the CRC received value.

Channel Status Block

The channel status block accumulates all the control bits as they are received and performs a CRC check on the 191 bits. If the value of the 8bit CRC register is equal to zero, the CRC signal indicates that all the control bits are correct. You can access channel status bits via a 192-bit output bus

VCXO Control

The resample block generates a rxclk_out signal that can be fed through an external VCXO to remove the jitter caused by resample block. The VCXO control sets up the correct divider ratio to generate a 27-MHz

12 Preliminary

Altera Corporation

Functional Description

output that is fed to a second PLL. Figure 1 on page 3 shows how you connect a system where AES3/EBU transmitters must be synchronized to a digital audio reference signal (DARS) input.

Transmitter

Figure 9 shows the transmitter. Figure 9. AES/EBU Transmitter

Transmit Clock 24 Audio Left 24 Audio Right Parity Generator Bi-Phase Coder AES3/EBU Out

Transmit Clock

CRCC Generator

192 Channel Status Data

The transmitter comprises the following elements:

Parity generator Bi-phase coder CRC generator

Table 3 shows the transmittter signals.

Table 3. Transmitter Signals (Part 1 of 2) Name

reset_n aes_clk asb_a[3:0] asb_b[3:0] asw_a[19:0] asw_b[19:0]

Direction

Input Input Input Input Input Input Reset.

Description

Transmit clock (at bit rate). Auxilliary sample bit (left channel). Auxilliary sample bit (right channel). Audio sample word (left channel). Audio sample word (right channel).

Altera Corporation

13 Preliminary

AES3/EBU Reference Design

Table 3. Transmitter Signals (Part 2 of 2) Name

vb_a vb_b udb_a udb_b csb_a csb_b

Direction

Input Input Input Input Input Input

Description

Validity bit (left channel). Validity bit (right channel). User data bit (left channel). User data bit (right channel). CS bit from FIFO buffer (left channel). CS bit from FIFO buffer (right channel). Channel status bit (local) (left channel). Channel status bit (local) (right channel). When "1" read from FIFO buffer; when "0" read from local_ctrl. Enables the tranmitter when data is ready. Read request from the FIFO buffer (left channel). Read request from the FIFO buffer (right channel). AES3/EBU output. Channel left or right.

csb_reg_a[191:0] Input csb_reg_b[191:0] Input local_ctrl oe reg rd_req_a reg rd_req_b reg aes_out reg Ch_B

Input Input Ouput Ouput Ouput Ouput

The transmitter has inputs for channel status. These inputs in the reference design are derived directly from the receiver channel status outputs.

Parity Generator

The parity generator calculates the party of the 24-bit audio and the control bit (V, U, C). The result is then inserted as the last bit of the 32 bit word (P bit).

Bi-Phase Coder

The data is combined with a clock signal of twice the bit rate to code a 1 or a 0 with 2 bits. A 1 is coded with following two bits 01 and a 0 is either coded as a 00 or 11.

CRC Generator

The CRC is generated from the first 184 bits of the status channel block structure. The 8-bit result from the CRC calculation is inserted to form the 192-bit status channel block structure.

14 Preliminary

Altera Corporation

Functional Description

Testbench

Altera supplies three testbenches with the reference design aes_input_tb_cvdb.v, aes_input_tb_svdb.v and aes_tx_tb_svdb.v. The aes_input_tb_cvdb.v testbench is a transmitter and receiver for the the Cyclone Video Demonstration Board; the aes_input_tb_svdb.v testbench is a similar design for the Stratix GX Video Demonstration Board; the aes_tx_tb_svdb.v testbench is for transmit only on the Stratix GX Video Demonstration Board. The two testbenches (aes_input_tb_cvdb.v and aes_input_tb_svdb.v) differ in their use of the VCXO. The aes_input_tb_svdb.v testbench uses the VCXO to remove jitter from the rxclk_out signal before applying it to the transmitter. The aes_input_tb_cvdb.v testbench uses the recovered receive clock directly as the transmiter clock without using the VCXO. The transmit jitter in aes_input_tb_cvdb.v testbench may not be strictly compliant with the AES3/EBU specification, but depends on the jitter of the input signal.

Electrical Interfaces

You can use the AES3/EBU reference design in two different ways depending on the end applicationwith a balanced or unbalanced interface.

Balanced Interfaces

The balanced interface is differential, so you must select differential input and output buffers in the Quartus II software. You need an RS-422 line driver and receiver, and a transformer to provide complete electrical isolation.

Unbalanced Interfaces (AES-3ID)

The unbalanced interface uses only one connector, which saves board space. You can use a 75 coaxial cable as a medium, which can run for hundreds of meters. Both the Cyclone Video Demonstration Board and Stratix GX Video Demonstration Board are re-using the ASI, which provides similar electrical characteristics. The receiver uses a simple transformer followed by a resistor bridge to guarantee the correct bias voltage for the Altera LVDS buffer. For the transmitter, the differential buffer drives the equalizer directly, and its output is electrically isolated through a transformer.

Altera Corporation

15 Preliminary

AES3/EBU Reference Design

Getting Started

This section involves the following steps: 1. 2. 3. 4. 5. System Requirements Install the Design Simulate using the Testbench Compile the Design Use the Demonstrations

System Requirements

The design requires the following hardware and software:

Stratix GX or Cyclone Video Demonstration Board Digital audio source and sink, e.g., Prism Sound dScope series III, or a DSA-1, or Audio Precision 2700 series. PC running the Windows 98/2000/XP software Quartus II version 4.2 or higher ModelSim-Altera version 5.8c

The precompiled libraries for ModelSim-Altera simulator are available from the Altera website at https://www.altera.com/support/software/download/service_packs/ quartus/dnl-qii30sp2.jsp.

Install the Design

To install the reference design, run the .exe and follow the installation instructions. Figure 10 shows the directory structure.

16 Preliminary

Altera Corporation

Getting Started

Figure 10. Directory Structure

auk_aes3 doc Contains the documentation. quartus Contains Quartus II project files. aes3_rxtx_cvdb_demo Contains the reference design demonstration mapped to the Cyclone Video Demonstration Board. aes3_rxtx_svdb_demo Contains the reference design demonstration mapped to the Altera Stratix GX Video Demonstration Board. aes3_tx_svdb_demo Contains the reference design demonstration mapped to the Altera Stratix GX Video Demonstration Board for transmit only. simulate Contains the simulation scripts for each testbench. aes3_rxtx_cvdb Contains the simulation scripts for the Cyclone Video Demonstration Board. aes3_rxtx_svdb Contains the simulation scripts for the Stratix GX Video Demonstration Board. aes3_tx_svdb Contains the simulation scripts for the Stratix GX Video Demonstration Board. source Contains the source files. tb Contains the testbench files.

Table 4 shows the Verilog HDL modules.

Table 4. Verilog HDL Modules (Part 1 of 2) Module

aes_channel_status _block.v aes_demo_cvdb.v aes_demo_svdb.v aes_formatter.v aes_pll.v aes_receiver.v aes_reset.v aes_rxsample.v aes_tx_phy_fifo.v

Description

Channel status block, which stores AES control signal and calculates CRC. AES3/EBU top-level design file for the Cyclone Video Demonstration Board. AES3/EBU top-level design file for the Stratix GX Video Demonstration Board. Formatter, which reconstructs the the frames audio and control. System PLL. Receiver. Reset control that waits for the PLLs to be locked before starting up. Serializer. Transmitter.

Altera Corporation

17 Preliminary

AES3/EBU Reference Design

Table 4. Verilog HDL Modules (Part 2 of 2) Module

aes_vcxo_control.v aes_word_aligner.v fifo.v led.v pll_tx.v ramp.v

Description

Controls the divider inputs of the MK2069 and the divider ics660. Word aligner, which searches for the preamble to synchronize the AES3/EBU input. FIFO buffer left and right channels. Flashing LED. PLL, to clock the AES3/EBU transmiter. Generates ramp-shape audio sample.

Simulate using the Testbench

The reference design includes three testbenches, aes3_input_tb_cvdb.v, aes3_input_tb_svdb.v and aes3_tx_tb_svdb, and a script for simulating with the ModelSim-Altera simulator. To use any of the testbenches, follow these steps:

For more information on the testbenches, see Testbench on page 15. 1. In the ModelSim simulator, choose Change Directory (File menu) and choose auk_aes3\simulate. Choose Execute Macro (Tools menu), choose aes.do, and click OK.

2.

The waveform viewer displays a selection of signals. The simulation runs automatically and provides a pass or fail indication on completion.

Compile the Design

Quartus II project files are provided for the reference design mapped to the Cyclone video demonstration board and the Stratix GX video demonstration board. The .qsf files define the pinout and other compilation directives for the designs. You must compile the designs to produce the device images required for the demonstrations. To compile any of the demonstration designs, open the relevant project in the Quartus II software and choose Start Compilation (Tools menu).

Use the Demonstrations

Figures 10 and 11 shows the demonstration on the Stratix GX or Cyclone Video Demonstration Board.

18 Preliminary

Altera Corporation

Getting Started

Figure 11. Demonstration on the Video Demonstration Boards

PC Interface

AES3/EBU Source & Sink AES Input Demonstration Board AES Output

Figure 12. Demonstration Set Up

To set up the demonstration, follow these steps:

Altera Corporation

19 Preliminary

AES3/EBU Reference Design

1.

Connect an audio source and sink, e.g., a Prism Sound dScope series III or a DSA-1, and a USB-Blaster download cable to a Stratix GX or Cyclone Video Demonstration Board (see Table 5).

Table 5. Connections Demonstration Board Connection Stratix GX

USB-Blaster download cable AES3/EBU receive AES3/EBU transmit JF1 J33 J34

Cyclone

J19 J1 J8

2.

Use the Quartus II Programmer to download the demonstration to the demonstration board.

When the demonstration is running correctly the Cyclone Video Demonstration Board LEDs have the following status:

D0 flashes D1 and D2 illuminate D2 is off

When the demonstration is running correctly the Stratix GX Video Demonstration Board LEDs have the following status:

D13 flashes D6, D9, D10, D11, and D12 illuminate D7 and D8 are off

Figure 13 shows the AES3/EBU output on a Prism Media Products Ltd scope (see Figure 13).

20 Preliminary

Altera Corporation

Resource Usage

Figure 13. AES3/EBU Output

Resource Usage

Table 6 shows the resource usage.

Table 6. Resource Usage Module

Receiver Transmitter Entire reference design on Stratix GX or Cyclone Video Demonstration Board

LEs

229 185 910

Altera Corporation

21 Preliminary

AES3/EBU Reference Design

References

The document uses the following references:

The AES3-2003 AES recommended practice for digital audio engineering Serial transmission format for two-channel linearly represented digital audio data (Revision of AES3-1992), see www.aes.org/standards/b_pub/aes3-2003.pdf The AES information document for digital audio engineeringGuidelines for the use of the AES3 interface, see www.aes.org/standards/b_pub/aes-2id-1996.pdf The AES recommended practice for digital audio engineering Synchronization of digital audio equipment in studio operations, see www.aes.org/standards/b_pub/aes11-2003.pdf.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 www.altera.com Applications Hotline: (800) 800-EPLD Literature Services: literature@altera.com

Copyright 2005 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

22 Preliminary

Altera Corporation

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- TimeQuest User GuideDocument133 pagesTimeQuest User Guideom007No ratings yet

- Pentax: Getting Started Shooting Playback Settings Appendix Operating ManualDocument112 pagesPentax: Getting Started Shooting Playback Settings Appendix Operating Manualmailmanager8946No ratings yet

- (Real Book) Antonio Ongarello - Italian Jazz StandardsDocument27 pages(Real Book) Antonio Ongarello - Italian Jazz Standardsmailmanager8946No ratings yet

- Pentax: Getting Started Shooting Playback Settings Appendix Operating ManualDocument112 pagesPentax: Getting Started Shooting Playback Settings Appendix Operating Manualmailmanager8946No ratings yet

- Audio Delivery Specifications Around the WorldDocument2 pagesAudio Delivery Specifications Around the Worldmailmanager8946No ratings yet

- (Real Book) Antonio Ongarello - Italian Jazz StandardsDocument27 pages(Real Book) Antonio Ongarello - Italian Jazz Standardsmailmanager8946No ratings yet

- Duality Drawings PDFDocument4 pagesDuality Drawings PDFmailmanager8946No ratings yet

- SSL ChannelDocument13 pagesSSL ChannelMoacir RibeiroNo ratings yet

- Mitsubishi ASX User ManualDocument368 pagesMitsubishi ASX User ManualDarren Thoon100% (1)

- K4A4G165WD Samsung PDFDocument69 pagesK4A4G165WD Samsung PDFmailmanager8946No ratings yet

- SSL ChannelDocument13 pagesSSL ChannelMoacir RibeiroNo ratings yet

- Reharmonization - RandyFelts PDFDocument190 pagesReharmonization - RandyFelts PDFmailmanager8946No ratings yet

- Applications of Dynamic Range ControlDocument5 pagesApplications of Dynamic Range Controlmailmanager8946No ratings yet

- SSL InstallationDocument65 pagesSSL Installationmailmanager8946No ratings yet

- Dynamics Processors - Technology & Application Tips: RanenoteDocument28 pagesDynamics Processors - Technology & Application Tips: Ranenotemailmanager8946No ratings yet

- (Real Book) Antonio Ongarello - Italian Jazz StandardsDocument27 pages(Real Book) Antonio Ongarello - Italian Jazz Standardsmailmanager8946No ratings yet

- GiannoulisMassbergReiss Dynamicrangecompression JAES2012 PDFDocument10 pagesGiannoulisMassbergReiss Dynamicrangecompression JAES2012 PDFmailmanager8946No ratings yet

- Arranging and Composing For The Small Ensemble jazz/R&B/jazz-rockDocument183 pagesArranging and Composing For The Small Ensemble jazz/R&B/jazz-rockDato SharikadzeNo ratings yet

- SSL ChannelDocument13 pagesSSL ChannelMoacir RibeiroNo ratings yet

- TimeQuest User GuideDocument133 pagesTimeQuest User Guideom007No ratings yet

- (Real Book) Antonio Ongarello - Italian Jazz StandardsDocument31 pages(Real Book) Antonio Ongarello - Italian Jazz Standardsmailmanager8946No ratings yet

- En50221 V1 PDFDocument86 pagesEn50221 V1 PDFmailmanager8946No ratings yet

- A Guide To MPEG Fundamentals PDFDocument101 pagesA Guide To MPEG Fundamentals PDFAdrian IlieNo ratings yet

- (Real Book) Antonio Ongarello - Italian Jazz StandardsDocument27 pages(Real Book) Antonio Ongarello - Italian Jazz Standardsmailmanager8946No ratings yet

- Paquito DRiveraDocument273 pagesPaquito DRiveramailmanager8946No ratings yet

- A Child Is Born - Lead SheetDocument1 pageA Child Is Born - Lead Sheetmailmanager8946No ratings yet

- SSL ChannelDocument13 pagesSSL ChannelMoacir RibeiroNo ratings yet

- PDFDocument22 pagesPDFmailmanager8946No ratings yet

- En300468 E3Document74 pagesEn300468 E3王建勳No ratings yet

- Arrow Electronics Deca Data Sheet Final PDFDocument2 pagesArrow Electronics Deca Data Sheet Final PDFmailmanager8946No ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Brain Computer Interfaces Meta AnalysisDocument70 pagesBrain Computer Interfaces Meta AnalysiskevNo ratings yet

- 8086 ProgrammingDocument16 pages8086 ProgrammingHariPriyan71% (7)

- COA Imp QUESTIONSDocument4 pagesCOA Imp QUESTIONSkazuma6362No ratings yet

- Nba DocumentDocument8 pagesNba DocumentmanjunathNo ratings yet

- Controllogix Remote I/O Communication Module: User ManualDocument176 pagesControllogix Remote I/O Communication Module: User ManualjesusNo ratings yet

- Edit and move text in documentsDocument6 pagesEdit and move text in documentsluckytypeNo ratings yet

- ATEKO Et Al DEVELOPMENT OF A NEWS DROID AND EVENT REPORTING SYSTEMDocument7 pagesATEKO Et Al DEVELOPMENT OF A NEWS DROID AND EVENT REPORTING SYSTEMBusayo AtekoNo ratings yet

- Composition Processes (1978)Document13 pagesComposition Processes (1978)alexhwangNo ratings yet

- Tic Tac ToeDocument17 pagesTic Tac ToeRishabh TripathiNo ratings yet

- Storage VirtualizationDocument22 pagesStorage VirtualizationDann LaurteNo ratings yet

- 66234en PDFDocument532 pages66234en PDFMarian ButerchiNo ratings yet

- CSS NC II CORE 1: Install & Configure Computer SystemsDocument54 pagesCSS NC II CORE 1: Install & Configure Computer SystemsEric Manrique Talamisan87% (38)

- IX - PartB - CH2 - Data Entry and Keyboard Skills - v2Document4 pagesIX - PartB - CH2 - Data Entry and Keyboard Skills - v2OjasNo ratings yet

- Input-Output StatementsDocument2 pagesInput-Output StatementskasulaumaNo ratings yet

- Televideo 910 912 920 925 950 TerminalsDocument8 pagesTelevideo 910 912 920 925 950 TerminalsEmilie PiepenbrinkNo ratings yet

- 3HAC050965 AM PROFIBUS Anybus Device RW 6-EnDocument40 pages3HAC050965 AM PROFIBUS Anybus Device RW 6-EnFranNo ratings yet

- Laboratory Work 1 Computation of Metrics of Productivity of Computer SystemDocument12 pagesLaboratory Work 1 Computation of Metrics of Productivity of Computer SystemHhhhhh75% (4)

- Xilinx Analog-Digital-Converter (XADC)Document8 pagesXilinx Analog-Digital-Converter (XADC)Mario PajaNo ratings yet

- Chapter 06Document12 pagesChapter 06fatenNo ratings yet

- Validity Checks: Processing ControlsDocument3 pagesValidity Checks: Processing Controlsjhela18No ratings yet

- 51 52 25 123 enDocument2 pages51 52 25 123 enManuelNo ratings yet

- Operating System Concepts 9th Edition Study GuideDocument19 pagesOperating System Concepts 9th Edition Study Guidehotfudge2116100% (2)

- HTTP WWW - Trenchgroup.com Ps Tools Download - PHP File Docudb Psfile Doc 60 Import4ab0be585c3be - Pdf&name Earth Fault Detection Device EFD20Document15 pagesHTTP WWW - Trenchgroup.com Ps Tools Download - PHP File Docudb Psfile Doc 60 Import4ab0be585c3be - Pdf&name Earth Fault Detection Device EFD20danvladimNo ratings yet

- Embedded Systems - WikibookDocument117 pagesEmbedded Systems - WikibookAman AroraNo ratings yet

- Department of Computer ScienceDocument22 pagesDepartment of Computer ScienceTalha RashidNo ratings yet

- CamScanner Scanned DocumentDocument1,284 pagesCamScanner Scanned DocumentGeorgeanne 25100% (1)

- Paper 1 Questions PDFDocument8 pagesPaper 1 Questions PDFQuaye AryeeNo ratings yet

- Siemens 6ES7214 1BG40 0XB0 DatasheetDocument9 pagesSiemens 6ES7214 1BG40 0XB0 DatasheetFelix Eduardo Ossorio GarciaNo ratings yet

- GBS 8200Document3 pagesGBS 8200pitacas100% (1)

- Manuali - Eltex.biz Manuali Siei ARTDriveG-EVDocument214 pagesManuali - Eltex.biz Manuali Siei ARTDriveG-EVRoxana NegoitaNo ratings yet