Professional Documents

Culture Documents

Practicas Full

Uploaded by

LEMNIOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Practicas Full

Uploaded by

LEMNICopyright:

Available Formats

1

1

INSTITUTO POLITECNICO

NACIONAL

UNIDAD PROFESIONAL INTERDISCIPLINARIA EN

INGENIERIA Y TECNOLOGIAS AVANZADAS

PROFESOR: Rodrguez fuentes Miguel ngel

2

2

ndice

Practica 1 compuertas logicas 3

Practica 2 display de 7 segmentos4

Practica 3 problema de diseo de banco6

Practica 4 puerta corrediza..7

Practica 5 detector de unos consecutivo8

Practica 6 teclado del cajero.9

Practica 7 prctica del lser 10

Practica 8 contador de 0 a 999912

Practica 9 diseo jerrquico serial..16

Practica 10 prctica del semforo ..18

Practica 11 contador de 0 a 99 .21

Practica 12 prctica de examen diseo del microondas..23

Practica 13 diseo de una cerradura.26

Practica 14 prctica de mini trminos.28

Practica 15 comparadores en paralelo29

3

3

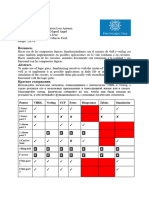

Reporte de prcticas electrnica digital

Practica 1

Implementar en una FPGA las 7compuertas lgicas (NOT, AND, NAND,OR,NOR,XOR Y NOT)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity compuerta is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

f1 : out STD_LOGIC;

f2 : inout STD_LOGIC;

f3 : out STD_LOGIC;

f4 : inout STD_LOGIC;

f5 : out STD_LOGIC;

f6 : inout STD_LOGIC;

f7 : out STD_LOGIC);

end compuerta;

architecture Behavioral of compuerta is

begin

f1<= not a;-- compuerta not

f2<= a and b and c and d; -- compuerta and

f3<= not f2; --f3<= not(a and b and c and d);

f4<= a or b or c or d;

f5<= not f4;

f6<= a xor b xor c xor d;

f7<= not f6;

end Behavioral;

pines de asignacion:

net"a" loc= R17;

net"b" loc= N17;

net"c" loc= L13;

net"d" loc= L14;

net "f1" loc=J15;

net "f2" loc=K15;

net "f3" loc=K14;

net "f4" loc=E17;

net "f5" loc=P15;

net "f6" loc=F4;

net "f7" loc=R4;

4

4

Practica 2:

Disear un circuito digital que muestre en un display de 7 segmentos los 16 smbolos del

sistema hexadecimal, considere un display de nodo comn.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity displaysp3 is

Port ( A,B,C,D,hab3,hab2,hab1,hab0 : in STD_LOGIC;

fa,fb,fc,ffd,fe,ff,fg,an3,an2,an1,an0: inout STD_LOGIC);

end displaysp3;

architecture Behavioral of displaysp3 is

signal entrada: std_logic_vector (3 downto 0);

signal salida: std_logic_vector (6 downto 0);

begin

entrada <= a & b & c & d;

salida <= fa & fb & fc & ffd & fe & ff & fg;

an3 <= hab3;

an2 <= hab2;

an1 <= hab1;

an0 <= hab0;

fa <= salida(6);

fb <= salida(5);

fc <= salida(4);

ffd <= salida(3);

fe <= salida(2);

ff <= salida(1);

fg <= salida(0);

process (entrada)

begin

case entrada is

when "0000" => salida <= "0000001";

when "0001" => salida <= "1001111";

when "0010" => salida <= "0010010";

when "0011" => salida <= "0000110";

when "0100" => salida <= "1001100";

when "0101" => salida <= "0100100";

when "0110" => salida <= "0100000";

when "0111" => salida <= "0001111";

when "1000" => salida <= "0000000";

when "1001" => salida <= "0000100";

when "1010" => salida <= "0001000";

5

5

when "1011" => salida <= "1100000";

when "1100" => salida <= "0110001";

when "1101" => salida <= "1000010";

when "1110" => salida <= "0110000";

when "1111" => salida <= "0111000";

when others => salida <= "1111111";

end case;

end process;

end Behavioral;

asignacion de pines:

net "A" loc=R17;

net "B" loc=N17;

net "C" loc=L13;

net "D" loc=L14;

net "fa" loc=l18;

net "fb" loc=f18;

net "fc" loc=d17;

net "ffd" loc=d16;

net "fe" loc=g14;

net "ff" loc=j17;

net "fg" loc=h14;

net "hab3" loc=K17;

net "hab2" loc=K18;

net "hab1" loc=H18;

net "hab0" loc=G18;

net "an3" loc=f17;

net "an2" loc=h17;

net "an1" loc=c18;

net "an0" loc=f15;

6

6

3.-practica de problema de diseo: una alarma de banco est diseada para verificar 4

seales de entrada, la lnea A es la de un interruptor secreto, la lnea B es de un sensor de

presin bajo la caja fuerte dentro de una bveda, la lnea C proviene de un reloj y la lnea D

est conectada a un interruptor de la bveda. Las siguientes condiciones generan 1 lgico:

A: el interruptor secreto est cerrado

B: la caja fuerte est en su posicin.

C: el reloj est entre las 10:00 y 14:00 horas(horas laborables)

D: la puerta de la bveda est cerrada.

Obtenga el circuito del sistema de alarma que produzca un 1 lgico cuando la caja es

extrada y el interruptor secreto est cerrado, o cuando se abre la bveda fuera del horario

de trabajo, o cuando se abre la bveda y el interruptor secreto est abierto.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

--use IEEE.NUMERIC_STD.ALL;

entity banco is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

D : in STD_LOGIC;

F : out STD_LOGIC);

end banco;

architecture Behavioral of banco is

signal entrada:std_logic_vector(3 downto 0);

begin

entrada <= A & B & C & D;

process (entrada)

begin

case entrada is

when "0000"=>F<='1';

when "0010"=>F<='1';

when "0100"=>F<='1';

when "0110"=>F<='1';

when "1000"=>F<='1';

when "1001"=>F<='1';

when "1010"=>F<='1';

when "1011"=>F<='1';

when "1100"=>F<='1';

when others =>F<='0';

end case;

end process;

end Behavioral;

7

7

Asignacin de pines:

net "A" loc= r17;

net "B" loc= n17;

net "C" loc= l13;

net "D" loc= l14;

net "F" loc= j14;

4.-problema de diseo: control de una puerta corrediza automtica. La entrada P al sistema

indica cuando un sensor detecta a una persona al frente de la puerta (p=1 indica que una

persona es detectada). La entrada H indica cuando la puerta debe mantenerse manualmente

abierta (H=1) sin importar si se detecta una persona . La entrada C indica cuando la puerta es

forzada a permanecer cerrada. Las ultimas 2 entradas pueden ser configuradas por el

ususario con unas llaves. Una salida F abre la puerta cuando F=1. Se requiere abrir la puerta

si la puerta esta configurada para mantenerse manualmente abierta , osi la puerta no esta

configurada para mantenerse manualmente abierta pero se detecta una persona. Sin

embargo en ambos casos la puerta solo se abrir si no est configurada para permenecer

cerrada. Obtenga el circuito para este sistema.

Codigo en VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity puerta is

Port ( P : in STD_LOGIC;

H : in STD_LOGIC;

C : in STD_LOGIC;

F : out STD_LOGIC);

end puerta;

architecture Behavioral of puerta is

signal entrada:std_logic_vector(2 downto 0);

begin

entrada <= P & H & C;

process(entrada)

begin

case entrada is

when"100"=>F<='1';

when"010"=>F<='1';

when"110"=>F<='1';

when others =>F<='0';

end case;

end process;

end Behavioral;

8

8

asignacion de pines:

net "P" loc=r17;

net "H" loc=n17;

net "C" loc=l13;

net "F" loc=r4;

5.-problema de diseo: se requiere implementar un circuito que detecte la ocurrencia de un

patrn de al menos tres unos adyacentes en una entrada de 8 bits, y la salida ser 1 en este

caso. Las entradas son a, b, c, d, e, f, g, h y la salida es y. Este tipo de circuitos son

ampliamente utilizados en el procesamiento de imgenes para detectar cosas, o para

detectar palabras especficas en un audio digitalizado. Obtener el circuito detector.

ibrary IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity detector_unos is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

e : in STD_LOGIC;

f : in STD_LOGIC;

g : in STD_LOGIC;

h : in STD_LOGIC;

y : out STD_LOGIC);

end detector_unos;

architecture Behavioral of detector_unos is

begin

y<=(a and b and c)

or (b and c and d)

or (c and d and e)

or (d and e and f)

or (e and f and g)

or (f and g and h);

end Behavioral;

Asignacin de pines:

net "a" loc=r17;

net "b" loc=n17;

net "c" loc=l13;

net "d" loc=l14;

net "e" loc=k17;

net "f" loc=k18;

net "g" loc=h18;

net "h" loc=g18;

net "y" loc=r4;

9

9

6- problemas de diseo:

Se requiere disear el circuito de un convertidor cuya salida es un cdigo de 4 bits (w,x,y,z)

correspondientes las teclas de un teclado matricial de un cajero automtico de 12 teclas de (

7 seales) . El teclado tiene la siguiente configuracin , el primer rengln tiene la siguiente

configuracin, el primer rengln tiene las teclas 1, 2, 3, el segundo rengln tiene 4,5,6 y el

tercer rengln tiene 7,8,9 y el ultimo rengln tiene al * 0 y # . las salidas del teclado matricial

son 7 seales, 54 corresponden a los renglones (r1,r2,r3,r4) y a las 3 columnas (c1, c2,c3). Al

oprimir cualquier tecla produce que las dos salidas valgan 1, correspondientes al rengln y

columna correspondiente yes a la tecla. Se desea que la tecla 0 a 9 se codifiquen desde

0000 hasta 1001 respectivamente. Codifique la tecla * como 1010, # como 1011 y asuma

que 1111 significa que ninguna tecla se esta oprimiendo.

Cdigo:

ibrary IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity teclado_cajero is

Port ( r1 : in STD_LOGIC;

r2 : in STD_LOGIC;

r3 : in STD_LOGIC;

r4 : in STD_LOGIC;

c1 : in STD_LOGIC;

c2 : in STD_LOGIC;

c3 : in STD_LOGIC;

w : out STD_LOGIC;

x : out STD_LOGIC;

y : out STD_LOGIC;

z : out STD_LOGIC);

end teclado_cajero;

architecture Behavioral of teclado_cajero is

begin

w<=(r3 and c2)

or (r3 and c3)

or (r4 and c1)

or (r4 and c3)

or ((not r1) and (not r2) and (not r3) and (not r4) and (not c1) and (not c2) and (not c3));

x<=(r2 and c1)

or (r2 and c2)

or (r2 and c3)

or (r3 and c1)

or ((not r1) and (not r2) and (not r3) and (not r4) and (not c1) and (not c2) and (not c3));

y<=(r1 and c2)

or (r1 and c3)

or (r2 and c3)

10

10

or (r3 and c1)

or (r4 and c1)

or (r4 and c3)

or ((not r1) and (not r2) and (not r3) and (not r4) and (not c1) and (not c2) and (not c3));

z<=(r1 and c1)

or (r1 and c3)

or (r2 and c2)

or (r3 and c1)

or (r3 and c3)

or (r4 and c3)

or ((not r1) and (not r2) and (not r3) and (not r4) and (not c1) and (not c2) and (not c3));

end Behavioral;

Asignacin de pines:

net "r1" loc=r17;

net "r2" loc=n17;

net "r3" loc=l13;

net "r4" loc=l14;

net "c1" loc=k17;

net "c2" loc=k18;

net "c3" loc=h18;

net "w" loc=r4;

net "x" loc=f4;

net "y" loc=p15;

net "z" loc=e17;

7.-prctica circuito secuencial (circuito controlador de laser)

Diseo del programa en VHDL de un sistema para cirujia laser. El cirujano activa ellaser

presionando momentanamente un boton y permanecer activo durante 25 ns, asuma que el

periodo de seal de reloj es de 10ns.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

entity laser is

Port ( b : in STD_LOGIC;

mclk : in STD_LOGIC;

x : out STD_LOGIC;

clksal : out STD_LOGIC);

end laser;

architecture Behavioral of laser is

11

11

signal clkdiv: std_logic_vector(25 downto 0);

type estados is (off1,on1,on2,on3,off2);

signal presente,siguiente: estados;

begin

--divisor de frecuencia

process(mclk)

begin

if (mclk'event and mclk='1') then

clkdiv <= clkdiv + 1;

end if;

end process;

clksal <= clkdiv(25);

-- maquina de estados

--transiciones

process (presente,b)

begin

case presente is

when off1 => x<= '0';

if (b='0') then

siguiente <= off1;

else

siguiente <= on1;

end if;

when on1=> x <='1';

siguiente <= on2;

when on2=> x <='1';

siguiente <= on3;

when on3=> x <='1';

siguiente <= off2;

when off2 => x<= '0';

if (b='0') then

siguiente <= off1;

else

siguiente <= off2;

end if;

end case;

end process;

-- reloj maquina de estados

process (clkdiv(25))

begin

12

12

if (clkdiv(25)'event and clkdiv(25)='1') then

presente <= siguiente;

end if;

end process;

end Behavioral;

asignacion de pines:

net"b" loc=b18;

net"mclk" loc=b8;

net"x" loc=j14;

net"clksal" loc=j15;

8.- disear un programa en VHDL que sea un contador de 0 a 9999

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

entity contador9999 is

Port ( reset : in STD_LOGIC;

hold : in STD_LOGIC;

clk : in STD_LOGIC;

seg : out STD_LOGIC_VECTOR (6 downto 0);

an : out STD_LOGIC_VECTOR (3 downto 0);

unidad : out STD_LOGIC_VECTOR (3 downto 0);

decena : out STD_LOGIC_VECTOR (3 downto 0);

centena: out STD_LOGIC_VECTOR (3 downto 0);

millar: out STD_LOGIC_VECTOR (3 downto 0));

end contador9999;

architecture Behavioral of contador9999 is

signal clkdiv: std_logic_vector(21 downto 0);

signal q,r,p,s,dato:std_logic_vector(3 downto 0); --unidad y decena esto se hace para dejar

unidad y decena como salida y no como inout

signal aux:std_logic_vector(1 downto 0);

begin

-- divisor de frecuencia

process(clk)

begin

if (clk'event and clk='1') then

clkdiv<= clkdiv+1;

end if;

end process;

13

13

--contador de decadas

process(clkdiv(21),reset,hold)

begin

if reset='1' then

q<="0000";

r<="0000";

p<="0000";

s<="0000";

elsif(clkdiv(21)'event and clkdiv(21)='1') then

if hold='0' then

q<= q+1;

if q="1001" then

q<="0000";

r<=r+1;

if (r="1001") then

r<="0000";

p<=p+1;

if (p="1001") then

p<="0000";

s<=s+1;

if (s="1001") then

s<="0000";

end if;

end if;

end if;

end if;

else

q<=q;

r<=r;

p<=p;

s<=s;

end if;

end if;

end process;

unidad<=q;

decena<=r;

centena<=p;

millar<=s;

process(dato)

begin

14

14

case dato is

when "0000" => seg <= "0000001";

when "0001" => seg <= "1001111";

when "0010" => seg <= "0010010";

when "0011" => seg <= "0000110";

when "0100" => seg <= "1001100";

when "0101" => seg <= "0100100";

when "0110" => seg <= "0100000";

when "0111" => seg <= "0001111";

when "1000" => seg <= "0000000";

when "1001" => seg <= "0000100";

when "1010" => seg <= "0001000";

when "1011" => seg <= "1100000";

when "1100" => seg <= "0110001";

when "1101" => seg <= "1000010";

when "1110" => seg <= "0110000";

when "1111" => seg <= "0111000";

when others => seg<= "1111111";

end case;

end process;

process(clkdiv(18))

begin

if (clkdiv(18)'event and clkdiv(18)='1') then

aux<=aux+1;

end if;

end process;

process(aux)

begin

if (aux="00") then --activar el display unidad

dato<= q;

an<= "1110";

elsif (aux="01") then

dato <= r; --decenas

an<="1101";

elsif (aux="10") then

dato <= p; --centenas

an<="1011";

else

dato<= s; --millares

15

15

an<="0111";

-- end if;

-- if (aux="0") then

--dato <= p; --centenas

--an<="1011";

-- else

--dato<= s; --millares

--an<="0111";

end if;

end process;

end Behavioral;

Asignacin de pines:

net"clk" loc=b8;

net"unidad<0>" loc=j14;

net"unidad<1>" loc=j15;

net"unidad<2>" loc=k15;

net"unidad<3>" loc=k14;

net"decena<0>" loc=e17;

net"decena<1>" loc=p15;

net"decena<2>" loc=f4;

net"decena<3>" loc=r4;

net"hold" loc=b18;

net"an<3>" loc=f15;

net"an<2>" loc=c18;

net"an<1>" loc=h17;

net"an<0>" loc=f17;

net"seg<0>" loc=h14;

net"seg<1>" loc=j17;

net"seg<2>" loc=g14;

net"seg<3>" loc=d16;

net"seg<4>" loc=d17;

net"seg<5>" loc=f18;

net"seg<6>" loc=l18;

16

16

9.- diseo jerrquico de comparador serial.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity comparador2_serial is

Port ( a1 : in STD_LOGIC;

a2 : in STD_LOGIC;

b1 : in STD_LOGIC;

b2 : in STD_LOGIC;

G : out STD_LOGIC;

L : out STD_LOGIC);

end comparador2_serial;

architecture Behavioral of comparador2_serial is

begin

G<= (a2 and (not b2)) or (a2 and a1 and (not b1)) or (a1 and (not b2) and (not b1));

L<= ((not a2) and b2) or ((not a1) and b2 and b1) or ((not a2) and (not a1) and b1);

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity comparador2_serial is

Port ( a1 : in STD_LOGIC;

a2 : in STD_LOGIC;

b1 : in STD_LOGIC;

17

17

b2 : in STD_LOGIC;

G : out STD_LOGIC;

L : out STD_LOGIC);

end comparador2_serial;

architecture Behavioral of comparador2_serial is

begin

G<= (a2 and (not b2)) or (a2 and a1 and (not b1)) or (a1 and (not b2) and (not b1));

L<= ((not a2) and b2) or ((not a1) and b2 and b1) or ((not a2) and (not a1) and b1);

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity comparador2_serial is

Port ( a1 : in STD_LOGIC;

a2 : in STD_LOGIC;

b1 : in STD_LOGIC;

b2 : in STD_LOGIC;

G : out STD_LOGIC;

L : out STD_LOGIC);

end comparador2_serial;

architecture Behavioral of comparador2_serial is

begin

G<= (a2 and (not b2)) or (a2 and a1 and (not b1)) or (a1 and (not b2) and (not b1));

L<= ((not a2) and b2) or ((not a1) and b2 and b1) or ((not a2) and (not a1) and b1);

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.all;

package pack is

component comparador2_serial

Port ( a1 : in STD_LOGIC;

a2 : in STD_LOGIC;

b1 : in STD_LOGIC;

b2 : in STD_LOGIC;

G : out STD_LOGIC;

L : out STD_LOGIC);

end component comparador2_serial;

18

18

end pack;

asignacin de pines:

net "a1" loc ="G18";

net "a2" loc ="H18";

net "a3" loc ="K18";

net "a4" loc ="K17";

net "b1" loc ="L14";

net "b2" loc ="L13";

net "b3" loc ="N17";

net "b4" loc ="R17";

net "G" loc ="J14";

net "L" loc ="J15";

10.-Practica dise;ar un programa en VHDL semaforo

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity semaforo is

Port ( et : in STD_LOGIC;

wt : in STD_LOGIC;

19

19

mclk : in STD_LOGIC;

clksal : out STD_LOGIC;

d5,d4,d3,d2,d1,d0 : out STD_LOGIC);

end semaforo;

architecture Behavioral of semaforo is

signal clkdiv: std_logic_vector(25 downto 0);

type estados is (s0, s1, s2, s3,s4,s5,s6,s7,s8, s9);

signal presente, siguiente: estados;

signal daux:std_logic_vector(5 downto 0);

begin

--divisor de frecuencia

process(mclk)

begin

if (mclk'event and mclk='1') then

clkdiv<=clkdiv+1; --contador

end if;

end process;

clksal<= clkdiv(25); --frecuencia de salida

--maquina de estados

--transiciones

process(presente,et,wt)

begin

case presente is

when s0 => daux <= "001100";

siguiente <= s1;

when s1 => daux <= "001100";

siguiente <= s2;

when s2 => daux <= "001100";

siguiente <= s3;

when s3 => daux <= "001100";

if (et='1' or wt='1') then

siguiente <= s4;

else

siguiente <= s0;

end if;

20

20

when s4 => daux <= "010100";

siguiente <= s5;

when s5 => daux <= "100001";

siguiente <= s6;

when s6 => daux <= "100001";

siguiente <= s7;

when s7 => daux <= "100001";

siguiente <= s8;

when s8 => daux <= "100001";

siguiente <= s9;

when s9 => daux <= "100010";

siguiente <= s0;

end case;

end process;

d5 <= daux(5);

d4 <= daux(4);

d3 <= daux(3);

d2 <= daux(2);

d1 <= daux(1);

d0 <= daux(0);

--reloj de la maquina de estados

process(clkdiv(25))

begin

if(clkdiv(25)'event and clkdiv(25)='1') then

presente<= siguiente; --cambio de estado

end if;

end process;

end Behavioral;

asignacin de pines:

net "d5" loc=r4;

net "d4" loc=f4;

net "d3" loc=p15;

net "d2" loc=e17;

net "d1" loc=k14;

net "d0" loc=k15;

net "et" loc=r17;

21

21

net "wt" loc=n17;

net "mclk" loc=b8;

11.-Disenar un contador de 0 a 99

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

entity Contador is

Port ( reset : in STD_LOGIC;

hold : in STD_LOGIC;

clk : in STD_LOGIC;

seg : out STD_LOGIC_VECTOR (6 downto 0);

an : out STD_LOGIC_VECTOR (3 downto 0);

unidad : out STD_LOGIC_VECTOR (3 downto 0);

decena : out STD_LOGIC_VECTOR (3 downto 0));

end Contador;

architecture Behavioral of Contador is

signal clkdiv: std_logic_vector(21 downto 0);

signal q,r,dato:std_logic_vector(3 downto 0); --q y r seran los valores que daran el salto de

unidad a decena

signal aux:std_logic_vector(0 downto 0);

begin

-- divisor de frecuencia

process(clk)

begin

if (clk'event and clk='1') then

clkdiv<= clkdiv+1;

end if;

end process;

--contador de unidades y decadas

process(clkdiv(21),reset,hold)

begin

if reset='1' then

q<="0000";

r<="0000";

--p<="0000";

--s<="0000";

elsif(clkdiv(21)'event and clkdiv(21)='1') then

if hold='0' then

q<= q+1;

22

22

if q="1001" then

q<="0000";

r<=r+1;

if (r="1001") then

r<="0000";

end if;

end if;

else

q<=q;

r<=r;

end if;

end if;

end process;

unidad<=q;

decena<=r;

process(dato)

begin

case dato is

when "0000" => seg <= "0000001";

when "0001" => seg <= "1001111";

when "0010" => seg <= "0010010";

when "0011" => seg <= "0000110";

when "0100" => seg <= "1001100";

when "0101" => seg <= "0100100";

when "0110" => seg <= "0100000";

when "0111" => seg <= "0001111";

when "1000" => seg <= "0000000";

when "1001" => seg <= "0000100";

when "1010" => seg <= "0001000";

when "1011" => seg <= "1100000";

when "1100" => seg <= "0110001";

when "1101" => seg <= "1000010";

when "1110" => seg <= "0110000";

when "1111" => seg <= "0111000";

when others => seg<= "1111111";

end case;

end process;

process(clkdiv(18))

begin

if (clkdiv(18)'event and clkdiv(18)='1') then

23

23

aux<=aux+1;

end if;

end process;

process(aux)

begin

if (aux="0") then --muestra unidades

dato<= q;

an<= "1110";

else

dato <= r; --muetra decenas

an<="1101";

end if;

end process;

end Behavioral;

Asignacion de pines:

net"clk" loc=b8;

net"unidad<0>" loc=j14;

net"unidad<1>" loc=j15;

net"unidad<2>" loc=k15;

net"unidad<3>" loc=k14;

net"decena<0>" loc=e17;

net"decena<1>" loc=p15;

net"decena<2>" loc=f4;

net"decena<3>" loc=r4;

net"hold" loc=b18;

net"an<3>" loc=f15;

net"an<2>" loc=c18;

net"an<1>" loc=h17;

net"an<0>" loc=f17;

net"seg<0>" loc=h14;

net"seg<1>" loc=j17;

net"seg<2>" loc=g14;

net"seg<3>" loc=d16;

net"seg<4>" loc=d17;

net"seg<5>" loc=f18;

net"seg<6>" loc=l18;

12.- programa en VHDL examen de micro ondas

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

24

24

entity microondas is

Port ( clk : in STD_LOGIC;

p : in STD_LOGIC;

b : in STD_LOGIC;

stl : in STD_LOGIC_VECTOR (2 downto 0);

st : in STD_LOGIC_VECTOR (2 downto 0);

reset : in STD_LOGIC;

gm : out STD_LOGIC;

m : out STD_LOGIC;

as : out STD_LOGIC);

end microondas;

architecture Behavioral of microondas is

signal clkdiv:std_logic_vector(25 downto 0 );

type estados is(seguridad,espera,calentar,alarma);

signal presente,siguiente:estados;

begin

-- divisor de frecuencias

process(clk)

begin

if clk'event and clk='1' then

clkdiv <= clkdiv+1;

end if;

end process;

--registro de estados

process(clkdiv(25),reset)

begin

if reset='1' then

presente <= seguridad;

elsif clkdiv(25)'event and clkdiv(25)='1' then

presente <= siguiente;

end if;

end process;

--asignacion de salidas

process(clkdiv(25),reset)

begin

if reset='1' then

gm <= '0';

m <= '0';

as <= '0';

elsif clkdiv(25)'event and clkdiv(25)='1' then

case presente is

when seguridad =>

gm <= '0';

25

25

m <= '0';

as <= '0';

when espera =>

gm <= '0';

m <= '0';

as <= '0';

when calentar =>

gm <= '1';

m <= '1';

as <= '0';

when alarma =>

gm <= '0';

m <= '0';

as <= '1';

end case;

end if;

end process;

-- transicion de entrada

process(stl,st,b,p,presente)

begin

siguiente <= seguridad; --cambio al estado siguiente

case presente is

when seguridad =>

if p='0' then

siguiente <= seguridad;

else

siguiente <= espera;

end if;

when espera =>

if b='0' then

siguiente <=espera;

else

siguiente <= calentar;

end if;

when calentar =>

if p='0' then

siguiente <= seguridad;

elsif stl<st then

siguiente <= calentar;

elsif stl >= st then

siguiente <= alarma;

end if;

when alarma =>

siguiente <= seguridad;

end case;

26

26

end process;

end Behavioral;

asignacion de pines:

net"clk" loc=b8;

net"gm" loc=j14;

net"m" loc=j15;

net"as" loc=k15;

net"p" loc=g18;

net"b" loc=h18;

13 practica de cerradura:disenar un programa que introduzca secuencia de unos y ceros

preestablecida para abrir la puerta.

Codigo en VHDL

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use IEEE.std_logic_unsigned.all;

entity cerradura is

Port ( reset : in STD_LOGIC;

enter : in STD_LOGIC;

i : in STD_LOGIC;

clk : in STD_LOGIC;

mal : out STD_LOGIC;

ok : out STD_LOGIC);

end cerradura;

architecture Behavioral of cerradura is

signal q: std_logic_vector(17 downto 0);

signal delay1, delay2, delay3:std_logic;

signal pulso: std_logic;

signal reg,dato: std_logic_vector(7 downto 0);

signal s: std_logic_vector(3 downto 0);

begin

---Divisor a 190 Hz aprox

process(clk)

begin

if (clk'event and clk='1') then

q<=q+1;

end if;

27

27

end process;

--Eliminador de rebotes y genera un pulso

process(q(17), reset, enter)

begin

if(reset='1') then

delay1<='0';

delay2<='0';

delay3<='0';

elsif(q(17)'event and q(17)='1') then

delay1<=enter;

delay2<=delay1;

delay3<=delay2;

end if;

end process;

pulso<= delay1 and delay2 and not delay3;

--registro de corrimiento entrada serial salida paralela

process(pulso,i,reset)

begin

if reset='1' then

reg<= "00000000";

elsif(pulso'event and pulso='1') then

reg<= i & reg(7 downto 1);

end if;

end process;

--contador

process(pulso,reset)

begin

if reset='1' then

s<="0000";

elsif(pulso'event and pulso='1') then

s<= s+1;

end if;

end process;

-- Comparador

dato<="10110111";

process(reg,dato,s)

begin

if(reg=dato and s="1000") then

28

28

ok<='1';

mal<='0';

else

ok<='0';

mal<='1';

end if;

end process;

end Behavioral;

asignacion de pines:

net"reset" loc=h13;

net"enter" loc=b18;

net"i" loc=r17;

net"mal" loc=j14;

net"ok" loc=r4;

net"clk" loc=b8;

14.- programa de miniterminos:

Codigo en VHDL:

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity practica2 is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

f1 : out STD_LOGIC;

f2 : out STD_LOGIC);

end practica2;

architecture Behavioral of practica2 is

begin

f1<= (NOT A AND NOT B AND C) OR (NOT A AND B AND NOT C) OR (A AND NOT B AND NOT C)

OR (A AND B AND C);

f2<= (A OR B OR C) AND (A OR NOT B OR NOT C) AND (NOT A OR B OR NOT C) AND (NOT A OR

NOT B OR C);

end Behavioral;

asignacion de pines:

NET "A" LOC= R17;

NET "B" LOC= N17;

NET "C" LOC= L13;

NET "f1" LOC= R4;

29

29

NET "f2" LOC= F4;

15 programa de comparador el paralelo:

Cdigo en VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use work.pack.all;

entity cuerpo is

Port ( a1,a2,a3,a4 : in STD_LOGIC;

b1,b2,b3,b4 : in STD_LOGIC;

G,L : out STD_LOGIC);

end cuerpo;

architecture Behavioral of cuerpo is

signal G1,G2,L1,L2 : std_logic;

begin

t1: comparador2_paralelo port map (a1=>a1,a2=>a2,b1=>b1,b2=>b2,G=>G1,L=>L1);

t2: comparador2_paralelo port map (a1=>a3,a2=>a4,b1=>b3,b2=>b4,G=>G2,L=>L2);

t3: comparador2_paralelo port map (a1=>G1,a2=>G2,b1=>L1,b2=>L2,G=>G,L=>L);

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity comparador2_paralelo is

Port ( a1 : in STD_LOGIC;

a2 : in STD_LOGIC;

b1 : in STD_LOGIC;

b2 : in STD_LOGIC;

G : out STD_LOGIC;

L : out STD_LOGIC);

end comparador2_paralelo;

architecture Behavioral of comparador2_paralelo is

begin

G<= (a2 and (not b2)) or (a2 and a1 and (not b1)) or (a1 and (not b2) and (not b1));

L<= ((not a2) and b2) or ((not a1) and b2 and b1) or ((not a2) and (not a1) and b1);

end Behavioral;

30

30

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity comparador2_paralelo is

Port ( a1 : in STD_LOGIC;

a2 : in STD_LOGIC;

b1 : in STD_LOGIC;

b2 : in STD_LOGIC;

G : out STD_LOGIC;

L : out STD_LOGIC);

end comparador2_paralelo;

architecture Behavioral of comparador2_paralelo is

begin

G<= (a2 and (not b2)) or (a2 and a1 and (not b1)) or (a1 and (not b2) and (not b1));

L<= ((not a2) and b2) or ((not a1) and b2 and b1) or ((not a2) and (not a1) and b1);

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity comparador2_paralelo is

Port ( a1 : in STD_LOGIC;

a2 : in STD_LOGIC;

b1 : in STD_LOGIC;

b2 : in STD_LOGIC;

G : out STD_LOGIC;

L : out STD_LOGIC);

end comparador2_paralelo;

architecture Behavioral of comparador2_paralelo is

begin

G<= (a2 and (not b2)) or (a2 and a1 and (not b1)) or (a1 and (not b2) and (not b1));

L<= ((not a2) and b2) or ((not a1) and b2 and b1) or ((not a2) and (not a1) and b1);

end Behavioral;

asignacion de pines:

net "a1" loc ="G18";

net "a2" loc ="H18";

31

31

net "a3" loc ="K18";

net "a4" loc ="K17";

net "b1" loc ="L14";

net "b2" loc ="L13";

net "b3" loc ="N17";

net "b4" loc ="R17";

net "G" loc ="J14";

net "L" loc ="J15";

You might also like

- Aprender Arduino, electrónica y programación con 100 ejercicios prácticosFrom EverandAprender Arduino, electrónica y programación con 100 ejercicios prácticosRating: 4.5 out of 5 stars4.5/5 (14)

- Aprender Arduino, prototipado y programación avanzada con 100 ejerciciosFrom EverandAprender Arduino, prototipado y programación avanzada con 100 ejerciciosRating: 5 out of 5 stars5/5 (5)

- Examen 1 DSDDocument4 pagesExamen 1 DSDAaronNo ratings yet

- P1-2 CLO ElectrologicDocument21 pagesP1-2 CLO Electrologicmiguel recillasNo ratings yet

- Ejercicios Resueltos VHDL2006Document13 pagesEjercicios Resueltos VHDL2006elfrich50% (2)

- Ejericios Propuestos VHDLDocument8 pagesEjericios Propuestos VHDLShaadNo ratings yet

- Ejemplos Basicos VHDLDocument19 pagesEjemplos Basicos VHDLmaylee25No ratings yet

- Microelectronica Parcial 2Document16 pagesMicroelectronica Parcial 2Alonso CalderonNo ratings yet

- P10 DDMDocument9 pagesP10 DDMSÁNCHEZ HERNÁNDEZ ALEJANDRANo ratings yet

- RelojDocument3 pagesRelojBOMJNo ratings yet

- Practica 3 DigitalesDocument14 pagesPractica 3 DigitalesMAURICIO REYES ROSERONo ratings yet

- Practica 3 PDFDocument6 pagesPractica 3 PDFpyp4y100% (1)

- 06 - Diseño MSI Con VHDL - 1Document15 pages06 - Diseño MSI Con VHDL - 1Levis BrisaNo ratings yet

- Modulo 2 Display 7 SegmentosDocument19 pagesModulo 2 Display 7 SegmentosAlejandra TéllezNo ratings yet

- Práctica2 VLSIDocument11 pagesPráctica2 VLSIMaximiliano Quiñones ReyesNo ratings yet

- Taller Digitales 2do CorteDocument6 pagesTaller Digitales 2do CorteEdward EstacioNo ratings yet

- Contador VHDL de 0 A 99Document2 pagesContador VHDL de 0 A 99lee47100% (1)

- Tarea DomiciliariaDocument16 pagesTarea DomiciliariaCarolinaRiveraNo ratings yet

- Reyesdeberquarus 2Document16 pagesReyesdeberquarus 2Rosa CastroNo ratings yet

- Examen VHDL CodigoDocument11 pagesExamen VHDL CodigoElias Sulub CetzNo ratings yet

- Práctica 2 - Compuertas Lógicas - Medina Oscar 4-A MAADocument9 pagesPráctica 2 - Compuertas Lógicas - Medina Oscar 4-A MAAOSCAR ADRIAN MEDINA DURANNo ratings yet

- Implementacion Basica de PicoblazeDocument14 pagesImplementacion Basica de PicoblazeFabian BallenNo ratings yet

- Ejercicios Resueltos VHDL2006Document13 pagesEjercicios Resueltos VHDL2006Ale KeyNo ratings yet

- Diseño de Logica Secuencial Con VHDLDocument35 pagesDiseño de Logica Secuencial Con VHDLinghectorr100% (1)

- Prob DiversosDocument14 pagesProb DiversosLeslie_g_mNo ratings yet

- Actividad 1 Diseño de Sistemas DigitalesDocument8 pagesActividad 1 Diseño de Sistemas Digitalesluis centeno fawcettNo ratings yet

- Referencia Rápida VHDLDocument4 pagesReferencia Rápida VHDLerick mondragon quintanaNo ratings yet

- Proyectos en ArduinoDocument11 pagesProyectos en ArduinoJuan David SolarteNo ratings yet

- Practica1 DesarrolloDocument16 pagesPractica1 DesarrolloDanielEscalonaNo ratings yet

- Programación en VHDLDocument17 pagesProgramación en VHDLsinchyNo ratings yet

- A4 2 Equipo 4Document11 pagesA4 2 Equipo 4EDSON JARED NEVAREZ GARCIANo ratings yet

- Pwm2 - Control de MotorDocument4 pagesPwm2 - Control de Motorjavier_valdivia_42No ratings yet

- Test BenchDocument21 pagesTest BenchFernando MartinezNo ratings yet

- Informe Quartus Sistemas Digitales IIDocument15 pagesInforme Quartus Sistemas Digitales IIMilagrosSanchezNo ratings yet

- Practica 2 SEDADocument9 pagesPractica 2 SEDACarlos M del RíoNo ratings yet

- Actividad 2 SolucionDocument16 pagesActividad 2 SolucionAndres ZaensNo ratings yet

- Práctica 5 - Sumador Completo - Medina Oscar 4ADocument8 pagesPráctica 5 - Sumador Completo - Medina Oscar 4AOSCAR ADRIAN MEDINA DURANNo ratings yet

- Interrupciones, Adc y PWM Practica 3Document8 pagesInterrupciones, Adc y PWM Practica 3Marco A RichterNo ratings yet

- EXAMEN ORDINARIO - DigDocument9 pagesEXAMEN ORDINARIO - DigluisNo ratings yet

- Compuertas VHDLDocument14 pagesCompuertas VHDLRamses Olivares100% (1)

- Capitulo 11Document12 pagesCapitulo 11Oscar SierraNo ratings yet

- Tarea 1 Flip Flops Bojorquez 5EBDocument13 pagesTarea 1 Flip Flops Bojorquez 5EBMoises BojorquezNo ratings yet

- 2 Dispositivos Integrados - Unidad FPGA VHDLDocument111 pages2 Dispositivos Integrados - Unidad FPGA VHDLAgustina Gutierrez PariNo ratings yet

- Práctica 7 Electrónica Digital IIDocument3 pagesPráctica 7 Electrónica Digital IIOctavio MontoyaNo ratings yet

- Practica - 10 ContadoresDocument8 pagesPractica - 10 ContadoresWilber GutierrezNo ratings yet

- Flip FlopsDocument25 pagesFlip FlopsAngel RodriguezNo ratings yet

- Examen Parcial de Arquitectura de ComputadorasDocument8 pagesExamen Parcial de Arquitectura de ComputadorasYaku Marisol Rodrigo VitónNo ratings yet

- Practica4 Logica Combinacional (Mendoza-Rodriguez)Document18 pagesPractica4 Logica Combinacional (Mendoza-Rodriguez)Iván RodríguezNo ratings yet

- Arquitectura ALUDocument20 pagesArquitectura ALUZachary Higgins0% (1)

- Ejercicios de VHDLDocument10 pagesEjercicios de VHDLdark_0No ratings yet

- Carpeta de TP Mecatronica IIDocument81 pagesCarpeta de TP Mecatronica IIAgustín TorresNo ratings yet

- Juego MastermindDocument13 pagesJuego MastermindFreddy JironNo ratings yet

- Ejemplos Practicos VHDLDocument18 pagesEjemplos Practicos VHDLEduardo Garcia Breijo84% (25)

- VAZQCARR6IM1P2Document38 pagesVAZQCARR6IM1P2pepeNo ratings yet

- Práctica5 VLSIDocument14 pagesPráctica5 VLSIMaximiliano Quiñones ReyesNo ratings yet

- Lab #4Document7 pagesLab #4Anonymous cIu2jy1R1No ratings yet

- IC3 Sol Jun2022 Sem2Document9 pagesIC3 Sol Jun2022 Sem2eduNo ratings yet

- Proyecto-Sistema Seguridad Caja FuerteDocument15 pagesProyecto-Sistema Seguridad Caja FuerteSantiago SamNo ratings yet

- ISLD Cursada 2020. Ejemplos de Diseño en VHDL. Anexo para PARTE 1 y 2Document14 pagesISLD Cursada 2020. Ejemplos de Diseño en VHDL. Anexo para PARTE 1 y 2Dward NoizeNo ratings yet

- Practica 7 (Maquina de Estado Finito) PDFDocument7 pagesPractica 7 (Maquina de Estado Finito) PDFLeonardo Mora100% (1)

- Semana 1Document23 pagesSemana 1Jose Jesus García GarcíaNo ratings yet

- Informe Corto Máq. de Los Ángeles (Enunciado) (Autoguardado)Document4 pagesInforme Corto Máq. de Los Ángeles (Enunciado) (Autoguardado)MelanieAlfonsoNo ratings yet

- Triángulos I: Academia Preuniversitaria "JOHANN MENDELDocument11 pagesTriángulos I: Academia Preuniversitaria "JOHANN MENDELMarcela AlejandraNo ratings yet

- TAREADocument2 pagesTAREASamy Diaz100% (1)

- Positi Vis MoDocument2 pagesPositi Vis Mobrayan Snader Sierra RiverosNo ratings yet

- Rio - Diseno y Analisis Dinamico de Un Sistema de Transmision de Minimo Peso para Una Bicicleta D...Document96 pagesRio - Diseno y Analisis Dinamico de Un Sistema de Transmision de Minimo Peso para Una Bicicleta D...Anibal Fuentes MagañaNo ratings yet

- Diagrama de Procesamiento de Pedidos Utilizando La Tecnología de La Información en Una Bodega y Las Técnicas de Control.Document4 pagesDiagrama de Procesamiento de Pedidos Utilizando La Tecnología de La Información en Una Bodega y Las Técnicas de Control.Alexander HernandezNo ratings yet

- Sesión 08Document15 pagesSesión 08CarolinaNo ratings yet

- MEDICION DEL TRABAJODocument171 pagesMEDICION DEL TRABAJORamon Asiu CorralesNo ratings yet

- ActividadDocument2 pagesActividadAndrea Forero0% (1)

- Transductores y AplicacionesDocument42 pagesTransductores y AplicacionestonaNo ratings yet

- Wuolah Free Comandos Mathematica Matematica DiscretaDocument38 pagesWuolah Free Comandos Mathematica Matematica DiscretaMari GómezNo ratings yet

- 03 Turbinas HidraulicasDocument19 pages03 Turbinas HidraulicassaulleivaNo ratings yet

- Pirela WerginnDocument109 pagesPirela WerginnMineyomar Romero100% (1)

- Filtros Activos Por APROXIMACIÓN - KArizmendi - LZimmermann - MRosales - ADávilaDocument35 pagesFiltros Activos Por APROXIMACIÓN - KArizmendi - LZimmermann - MRosales - ADávilaKARLA PATRICIA ARIZMENDI GUERRANo ratings yet

- Camara Hilton FinalDocument20 pagesCamara Hilton FinalJulio César Canahuire VilcaNo ratings yet

- Unidad 02 Noción y Operaciones Con FraccionesDocument58 pagesUnidad 02 Noción y Operaciones Con FraccionesMarcos PascualNo ratings yet

- 15 Minutos LibroDocument57 pages15 Minutos LibroMarina GiménezNo ratings yet

- 7 PDFDocument13 pages7 PDFNicolas Arevalo RamirezNo ratings yet

- Modelos DeterminísticosDocument8 pagesModelos DeterminísticosElsa Janeth Acuña Camargo0% (1)

- Manejo Quirúrgico de La Luxación Acromioclavicular Grado III Con Sistema de Anclaje Doble BotónDocument5 pagesManejo Quirúrgico de La Luxación Acromioclavicular Grado III Con Sistema de Anclaje Doble BotónAlfonso Molina Oncólogo OrtopedistaNo ratings yet

- Sistemas de Transmisión de Movimiento PDFDocument15 pagesSistemas de Transmisión de Movimiento PDFDennis SoláNo ratings yet

- Derivada 2Document71 pagesDerivada 2Josue TunqueNo ratings yet

- Tubo de BourdonDocument5 pagesTubo de BourdonLuIzinn GlezNo ratings yet

- Surf HardDocument2 pagesSurf HardRicardo TorresNo ratings yet

- Método Grafico de CremonaDocument4 pagesMétodo Grafico de CremonaLuis Alfredo Curasi TrujillanoNo ratings yet

- Calculadora, Computadora y FuturoDocument6 pagesCalculadora, Computadora y FuturoJennifer Catalina Villatoro Gil67% (3)

- Alioth y MetatronDocument10 pagesAlioth y MetatronLeonid Zegarra YanquiNo ratings yet

- Aprovechamiento Del Calor ResidualDocument5 pagesAprovechamiento Del Calor ResidualOficina de ProyectosNo ratings yet