Professional Documents

Culture Documents

Tutorial Digital Control Loop Design

Uploaded by

Phạm Văn TưởngOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tutorial Digital Control Loop Design

Uploaded by

Phạm Văn TưởngCopyright:

Available Formats

Digital Control Loop Design

- 1 - Powersimtech Inc.

www.powersimtech.com

SmartCtrl Tutorial

Digital Control Loop Design

Digital Control Loop Design

- 2 - Powersimtech Inc.

www.powersimtech.com

SmartCtrl

1

is a general-purpose controller design software specifically for power electronics application.

This tutorial is intended to guide you, step by step, to design the digital control loop of a buck converter

and simulate it with PSIM.

The Digital control feature is only available in the SmartCtrl 2.0 Pro. The design procedure begins with

the design of the analog control loop. After that, the analog regulator is translated into the digital

domain taking into account several specific parameters of the digital design.

The first step is to select the power converter and the type of control, i.e., the plant to be controlled. In

this case, it is a voltage mode controlled Buck converter (Figure 1).

Figure 1 Plant selection.

The second step is to introduce the data corresponding to the plant, sensor and compensator. First,

plant parameters are defined (Figure 2).

1

SmartCtrl is copyright 2009-2012 by Carlos III University of Madrid, GSEP Power Electronics Systems Group, Spain

Digital Control Loop Design

- 3 - Powersimtech Inc.

www.powersimtech.com

Figure 2 Plant parameters dialog box.

Sensor parameters are defined in the corresponding dialog box (Figure 3). When a digital control loop is

designed, only Voltage Divider sensor must be selected.

Figure 3 Sensor parameters dialog box

Digital Control Loop Design

- 4 - Powersimtech Inc.

www.powersimtech.com

After selecting the regulator type (Type 3, Type 2 or PI), a new dialog box appears (Figure 4). Modulator

parameters are defined in this dialog box. Trailing edge unity gain modulator is selected for this case

(Vp=1, Vv=0, tr=10us).

Figure 4 Regulator dialog box. Modulator parameters.

Figure 5 Solution map window

The third step is to select the requirements of the control loop, i.e., to define the required cross over

frequency of the open loop transfer function fc and the phase margin PM. In SmartCtrl the user can

select graphically a solution inside the stable design space, called Solution Map (Figure 5), which defines

Digital Control Loop Design

- 5 - Powersimtech Inc.

www.powersimtech.com

the set of (fc, PM) resulting in a stable design. In this case, the selected cross over frequency is fc=4.5

kHz, and the selected phase margin is PM=50.

The analog loop is already designed (Figure 6). The Bode plot and Nyquist plot can be used to analyze

the stability, and the transient plot can be used to check the time domain performance. Once the analog

regulator has been determined, the digital control capability of SmartCtrl 2.0 can be used to calculate

the digital regulator. The procedure implemented in the Digital Control Module (Version 1.0) consist on

converting the analog design in a digital regulator by means of discretization (bilinear transformation) of

the analog regulator, taking into account some additional aspects of digital control.

Figure 6 Graphs corresponding to the analog regulator design.

The fourth step is to find the digital regulator, which can be calculated only after completing the design

steps of an analog regulator. In the icon bar, the user can find the icon (Figure 7) to open the Digital

settings dialog box. It can also be opened trough the menu Design->Digital Control.

Digital Control Loop Design

- 6 - Powersimtech Inc.

www.powersimtech.com

Figure 7 Icon to open the Digital control settings dialog box

The digital settings box appears, asking for the specific digital parameters (Figure 9): sampling

frequency, bits number and accumulated delay. The sampling frequency is often the same as the

switching frequency, but it can be different. Note that the sampling frequency must be a multiple or

submultiple of the switching frequency.

The bits number is related with the rounding of coefficients of digital compensator. Depending on each

case, a different number of bits can be enough to obtain a digital regulator similar to analog regulator,

as it will be detailed later. Note that bits number is referred only to the regulator coefficients

calculation.

Figure 8. Time diagram to represent the time delays considered in the digital regulator calculation

Accumulated delay is the time between the sampling instant and the PWM pulse effective updating

(Figure 8), which is the falling edge in the trailing edge pulse width modulator. Therefore, accumulated

delay includes analog to digital conversion delay, calculations delay and modulator delay, i.e., the sum of

all delays in the digital control loop. In general, the sampling instant may not be the initial instant of the

PWM period, as in this case.

Output voltage

(controlled quantity)

Driving

signals

Actual control

pulse updating

Accumulated delay

Sampling instants

tPWM= delay of modulator

TS=sampling period

TSW=switching period

time

Duty cycle value

PWM ramp

tPWM

Duty cycle

value

updating

Digital Control Loop Design

- 7 - Powersimtech Inc.

www.powersimtech.com

Figure 9 Digital settings dialog box

When digital settings have been completed, the check box Calculate digital compensator must be

checked. Then, the digital regulator is calculated, and icons to represent transfer function involving the

digital regulator are enabled (Figure 10).

Digital factors sweep dialog box (Figure 11) allows for changing dynamically the digital settings and

evaluate graphically the results. In the example of Figure 11 the number of bits has been changed, and

the results corresponding to 6 bits are shown. As it can be seen, digital open loop and analog open loop

transfer functions are different in magnitude (low frequencies) and in phase (medium and high

frequencies). It means that the selected number of bits is not enough to represent the coefficients of

the digital regulator, as it is the case of Figure 10, where 10 bits were selected. Note that in Figure 10

the magnitude of analog and digital responses are very similar, and phase responses are also very similar

except in high frequency range. Note that digital and analog regulators are different near of the half of

sampling frequency, regardless the selected number of bits, and the digital response takes into account

the accumulated delay, which is not included in the analog transfer functions.

Digital Control Loop Design

- 8 - Powersimtech Inc.

www.powersimtech.com

Figure 10 Graphs corresponding to analog and digital design. In the icon bar, the icon to represent the digital open loop gain

Tz is highlighted.

Digital Control Loop Design

- 9 - Powersimtech Inc.

www.powersimtech.com

Figure 11 Digital factors sweep dialog box. Results corresponding to 6 bits to represent the coefficients of the digital

regulator are shown.

Once the digital regulator has been calculated, the entire design can be exported to PSIM, and then

simulated (fifth step). In Figure 12 it is shown the corresponding icon. When clicking this icon, the export

dialog box appears (Figure 13). In order to simulate the digital regulator, z-domain coefficients must

be selected.

Digital Control Loop Design

- 10 - Powersimtech Inc.

www.powersimtech.com

Figure 12 Icon to export the design obtained in SmartCtrl to PSIM

Figure 13 Exporting options dialog box to generate the PSIM schematic.

The design is exported to a PSIM schematic, including a file where all converter and controller

parameters are contained.

Digital Control Loop Design

- 11 - Powersimtech Inc.

www.powersimtech.com

Figure 14 PSIM schematic result of the exportation of a SmartCtrl design (digital regulator)

In the PSIM schematic the power stage and the digital control stage appear. A trailing edge pulse width

modulator is included. In this particular implementation, the modulator introduces a time delay equal to

D/fsw, there D is duty cycle corresponding to the steady state operating point, and fsw is the switching

frequency. A time delay block is added to take into account the additional time delays in the control

loop, in such a way that the total time delay in control loop is equal to the value of accumulated delay

introduced by the user. The value of this time delay is automatically calculated by SmartCtrl.

A first test is to perform a time domain simulation to check that the steady state operating point is

achieved, i.e., output voltage equal to 4 V in this case (Figure 15). Note that in this first test a long

enough time simulation must be selected, in order to achieve steady state operation.

Digital Control Loop Design

- 12 - Powersimtech Inc.

www.powersimtech.com

Figure 15 Time domain simulation. Steady state operation is achieved.

The sixth step to simulate and compare the digital regulator is to include in the PSIM schematic the

components to perform an AC sweep to calculate the open loop transfer function (Tz) with PSIM. These

components are detailed in Figure 16. The result of the simulation is shown in Figure 17.

Digital Control Loop Design

- 13 - Powersimtech Inc.

www.powersimtech.com

Figure 16 Blocks to be added to perform an AC Sweep in order to obtain the open loop transfer function Tz

Figure 17 Result of the PSIM AC Sweep

Digital Control Loop Design

- 14 - Powersimtech Inc.

www.powersimtech.com

In order to compare the obtained AC response and the theoretical calculated with SmartCtrl, the digital

transfer function data must be exported to a text file. In Figure 18 the menu to export the

aforementioned data is shown. In Figure 19 the digital open loop transfer function export dialog box is

shown. The parameters have been selected in order to be similar to the AC sweep parameters selected

in PSIM (Figure 16).

Figure 18 Exportation of the digital open loop transfer function from SmartCtrl to a text file

Figure 19 Digital open loop export dialog box.

Digital Control Loop Design

- 15 - Powersimtech Inc.

www.powersimtech.com

Once SmartCtrl data have been exported to a text file, it has to be open, and the name of the first

column must be changed by the name Frequency, in order to be merged in Simview and compared

with PSIM simulation results. In Figure 20 digital open loop transfer function calculated with SmartCtrl

and AC sweep simulation performed with PSIM are compared. The results of PSIM simulations and

SmartCtrl calculations match well in this case.

Figure 20 Comparison of AC Sweep results simulated with PSIM (red) and SmartCtrl data (blue) for the open loop transfer

function.

Digital Control Loop Design

- 16 - Powersimtech Inc.

www.powersimtech.com

SmartCtrl includes also the capability to

import data from text files and compare

them with the transfer functions calculated

in SmarCtrl. In File menu, option Import

(Figure 21), a new dialog box Functions to

be merged appears (Figure 22). In this

dialog box, the user should select Add,

and then the Add transfer function dialog

box appears. Selecting T(f) button and

clicking on Text file, will result in a new

dialog box, Load file containing transfer

function to be compared, where the user

will select the .fra file from the simulation

with PSIM.

Finally, analog calculated, digital calculated

and digital simulated transfer functions can

be compared in the same Bode plot (Figure

23), where a good agreement between

simulated and calculated digital open loop

transfer functions can be observed.

Figure 21 Import men in SmartCtrl

Figure 22 Dialog boxes appearing when importing a transfer function to be compared in SmartCtrl

Digital Control Loop Design

- 17 - Powersimtech Inc.

www.powersimtech.com

Figure 23 Comparison between analog calculated, digital calculated and digital simulated open loop transfer functions.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Ethernet IP Texas InstrumentsDocument6 pagesEthernet IP Texas InstrumentsFranzKafkaNo ratings yet

- Control Intelligence Improves Renewable Energy EfficiencyDocument7 pagesControl Intelligence Improves Renewable Energy EfficiencyPhạm Văn TưởngNo ratings yet

- Uhc AwatersDocument60 pagesUhc Awaterskammu9713No ratings yet

- Ect129 Uninterruptible Static Power Supplies and The Protection of PersonsDocument44 pagesEct129 Uninterruptible Static Power Supplies and The Protection of PersonsMarko VujicaNo ratings yet

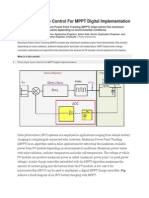

- Direct Duty Cycle Control For MPPT Digital ImplementationDocument5 pagesDirect Duty Cycle Control For MPPT Digital ImplementationPhạm Văn TưởngNo ratings yet

- All About HarmonicsDocument240 pagesAll About HarmonicsKhushal KharadeNo ratings yet

- Calculation of Short-Circuit CurrentsDocument35 pagesCalculation of Short-Circuit CurrentsdaodoquangNo ratings yet

- 309 An 09 Solar Panel PowerDocument3 pages309 An 09 Solar Panel PowerJoel Medina GuttiNo ratings yet

- The Adventures of Huckleberry Finn by Mark TwainDocument289 pagesThe Adventures of Huckleberry Finn by Mark TwainBooks100% (5)

- AN296110 Current Sensing For Renewable EnergyDocument4 pagesAN296110 Current Sensing For Renewable EnergyPhạm Văn TưởngNo ratings yet

- C Programming For Embedded System Applications PDFDocument54 pagesC Programming For Embedded System Applications PDFWendo David PesaNo ratings yet

- Evaluation and DSP Based Implementation of PWM Approaches For SinDocument90 pagesEvaluation and DSP Based Implementation of PWM Approaches For SinPhạm Văn TưởngNo ratings yet

- Slaa 075Document19 pagesSlaa 075Manidhar ParvatamNo ratings yet

- Disturbance Observers For Rigid Mechanical Systems - Equivalence, Stability, and DesignDocument10 pagesDisturbance Observers For Rigid Mechanical Systems - Equivalence, Stability, and DesignPhạm Văn TưởngNo ratings yet

- An Improved PV Battery Charger For Low Cost Low PowerDocument4 pagesAn Improved PV Battery Charger For Low Cost Low PowerPhạm Văn TưởngNo ratings yet

- A Novel Dynamic Var CompensatorDocument4 pagesA Novel Dynamic Var CompensatorPhạm Văn TưởngNo ratings yet

- IEEE Transactions On Power Systems Volume 10 Issue 2 1995 (Doi 10.1109/59.387938) Larsen, E.V. Sanchez-Gasca, J.J. Chow, J.H. - Concepts For Design of FACTS Controllers To Damp Power SwingsDocument9 pagesIEEE Transactions On Power Systems Volume 10 Issue 2 1995 (Doi 10.1109/59.387938) Larsen, E.V. Sanchez-Gasca, J.J. Chow, J.H. - Concepts For Design of FACTS Controllers To Damp Power SwingsPhạm Văn TưởngNo ratings yet

- Current-Transformer Phase-Shift Compensation and CalibrationDocument7 pagesCurrent-Transformer Phase-Shift Compensation and CalibrationrsrtnjNo ratings yet

- IEEE Transactions On Reliability Volume 43 Issue 1 1994 (Doi 10.1109/24.285133) Sallam, A.A. Desouky, M. Desouky, H. - Shunt Capacitor Effect On Electrical Distribution System ReliabilityDocument7 pagesIEEE Transactions On Reliability Volume 43 Issue 1 1994 (Doi 10.1109/24.285133) Sallam, A.A. Desouky, M. Desouky, H. - Shunt Capacitor Effect On Electrical Distribution System ReliabilityPhạm Văn TưởngNo ratings yet

- 1.A New Battery Model For Use With Battery Energy Storage Systems and Electric Vehicles Power SystemsDocument6 pages1.A New Battery Model For Use With Battery Energy Storage Systems and Electric Vehicles Power SystemschethanNo ratings yet

- Informatics in Control Automation and RoboticsDocument5 pagesInformatics in Control Automation and RoboticsPhạm Văn TưởngNo ratings yet

- Uninterruptible Power Supply Multiloop Control Employing Digital Predictive Voltage and Current RegulatorsDocument9 pagesUninterruptible Power Supply Multiloop Control Employing Digital Predictive Voltage and Current RegulatorsPhạm Văn TưởngNo ratings yet

- (Matsui) Sensorless PM Brushless DC Motor DrivesDocument9 pages(Matsui) Sensorless PM Brushless DC Motor DrivesPhạm Văn TưởngNo ratings yet

- Inverters For Single-Phase Grid Connected Photovoltaic Systems - An OverviewDocument6 pagesInverters For Single-Phase Grid Connected Photovoltaic Systems - An OverviewPhạm Văn TưởngNo ratings yet

- NHSPE ReadingDocument5 pagesNHSPE ReadingMohamed HanafiNo ratings yet

- Study of A Non-Isolated Bidirectional DC - DC Converter: C.-C. Lin, L.-S. Yang, G.W. WuDocument8 pagesStudy of A Non-Isolated Bidirectional DC - DC Converter: C.-C. Lin, L.-S. Yang, G.W. WuPhạm Văn Tưởng100% (1)

- TW Exams Ielts How To Prepare Ielts TipsDocument2 pagesTW Exams Ielts How To Prepare Ielts TipsHoda ElhadaryNo ratings yet

- Phan Tich 1 Bai Task 2 by Ngoc BachDocument4 pagesPhan Tich 1 Bai Task 2 by Ngoc BachPhạm Văn Tưởng100% (1)

- Space Vector Modulation An IntroductionDocument10 pagesSpace Vector Modulation An IntroductionJohan LinderNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Thank You For Your DownloadDocument8 pagesThank You For Your DownloadbadrasiriNo ratings yet

- OPAMPDocument24 pagesOPAMPEr Akhilesh SinghNo ratings yet

- Elektrozawory Pneumatyczne 4k ckd-2 PDFDocument70 pagesElektrozawory Pneumatyczne 4k ckd-2 PDFChongwoot SoyjampaNo ratings yet

- QUIZ With Solutions C ProgrammingDocument4 pagesQUIZ With Solutions C ProgrammingMouad KacemiNo ratings yet

- AN7395K PanasonicSemiconductorDocument3 pagesAN7395K PanasonicSemiconductorTaspen uddinNo ratings yet

- Shivani Sharma CV Data AnalystDocument3 pagesShivani Sharma CV Data Analystshivani sharmaNo ratings yet

- SKEMA - Daonm3mb6eo MBDocument32 pagesSKEMA - Daonm3mb6eo MBglepunkNo ratings yet

- Embedded System Laboratory Instruction Sheet Experiment No. 06 Experiment NameDocument5 pagesEmbedded System Laboratory Instruction Sheet Experiment No. 06 Experiment NameShiwangi KumariNo ratings yet

- Keyboard/Display Controller - Intel 8279Document16 pagesKeyboard/Display Controller - Intel 8279Anamika singhNo ratings yet

- Switches PDFDocument144 pagesSwitches PDFtomy_223825000No ratings yet

- GEH-6721 Vol III BJ PDFDocument738 pagesGEH-6721 Vol III BJ PDFbmw316No ratings yet

- DMC M3 AssignmentDocument14 pagesDMC M3 AssignmentHannanNo ratings yet

- IoT Based Circuit Breaker ARDUINO BasedDocument18 pagesIoT Based Circuit Breaker ARDUINO BasedShubnaya MS100% (2)

- President Lincoln BibleDocument31 pagesPresident Lincoln BibleGeorge Andreas Manthopoulos100% (1)

- Lenovo c325 c225 Daoqudmb6do Quanta QudDocument37 pagesLenovo c325 c225 Daoqudmb6do Quanta Qudfrom2No ratings yet

- Aruba Support Services For Distis - PPTX - Volume SLADocument20 pagesAruba Support Services For Distis - PPTX - Volume SLAsudha kNo ratings yet

- JOB Portal Project ReportDocument97 pagesJOB Portal Project ReportRamesh Chandra Mishra90% (69)

- BYW77P/PI-200: High Efficiency Fast Recovery Rectifier DiodesDocument6 pagesBYW77P/PI-200: High Efficiency Fast Recovery Rectifier DiodesGianmarco CastilloNo ratings yet

- ClickShare - Onepager - How To Share - ENDocument2 pagesClickShare - Onepager - How To Share - ENG & M Soft Technologies Pvt LtdNo ratings yet

- Ds Avr Project Board User GuideDocument3 pagesDs Avr Project Board User Guideamkhan1971No ratings yet

- SET 9 Soal Latihan MTCREDocument4 pagesSET 9 Soal Latihan MTCREErik Martin S., S.Kom. SMKS YADIKA 11 JatiranggaNo ratings yet

- 6410 6415 Stepper Drive Brochure En-Us RevADocument21 pages6410 6415 Stepper Drive Brochure En-Us RevARobney Souza da SilvaNo ratings yet

- Infineon-Design Guide LLC Converter ICE2HS01G-An-V01 00-EnDocument26 pagesInfineon-Design Guide LLC Converter ICE2HS01G-An-V01 00-EnAhmed AlagmyNo ratings yet

- Alvaristar: Network Management System For Broadband Wireless AccessDocument25 pagesAlvaristar: Network Management System For Broadband Wireless Accesslucorchea1No ratings yet

- MTP3055E: N-CHANNEL 60V - 0.1 - 12A TO-220 Stripfet™ Power MosfetDocument9 pagesMTP3055E: N-CHANNEL 60V - 0.1 - 12A TO-220 Stripfet™ Power MosfetTomass123No ratings yet

- IJRPR5085Document4 pagesIJRPR5085srinivasNo ratings yet

- Cic-500 DSP Development and Experiment SystemDocument2 pagesCic-500 DSP Development and Experiment SystemQuang ThắngNo ratings yet

- Physics II Chapter 6 PDFDocument10 pagesPhysics II Chapter 6 PDFrenNo ratings yet

- Chapter 4 I/O and Driver: Operating SystemsDocument45 pagesChapter 4 I/O and Driver: Operating SystemsChiếc Lá Nho NhỏNo ratings yet

- Oop Midterm - AnswersDocument4 pagesOop Midterm - AnswersNur KalkanNo ratings yet