Professional Documents

Culture Documents

Analog Electronic Circuits (ELE 209) RCS (Makeup)

Uploaded by

phdpushOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analog Electronic Circuits (ELE 209) RCS (Makeup)

Uploaded by

phdpushCopyright:

Available Formats

Department of Electrical and Electronics Engineering

Reg. No. :

MANIPAL INSTITUTE OF TECHNOLOGY, MANIPAL

(A Constituent Institute of Manipal University, Manipal)

THIRD SEMESTER B.E. DEGREE MAKEUP EXAMINATION

(REVISED CREDIT SYSTEM)

08 January 2011

ANALOG ELECTRONIC CIRCUITS (ELE 209)

Time: 3 hours

Note

Max. Marks: 50

: Answer any FIVE full questions. Refer Table-1 for h-parameters.

1A

1B

1C

Write a note on construction and applications of schottky diode.

(02)

Plot the Vi, V0 with respect to time and transfer characteristics, for the circuit shown in Fig 1(B).

(03)

For the zener diode voltage regulator shown in fig 1(C) determine VL, VR, IZ ,PZ, power dissipation

in R=1K series resistance and the safe maximum input voltage that can be applied.

(05)

2A

Determine the current source current I to obtain an output voltage V0=2V in the circuit shown in

Fig 2A. Assume all the diodes are identical and =1,VT=26mV and Is=

A

(02)

Determine IBQ, ICQ, VCEQ, VCQ for the amplifier shown in fig 2(B) .Assume VBE=0.7V.

(04)

Plot the output voltage in the circuit shown in the Fig 2C for vi=10sin . Assume all diodes are

ideal diodes.

(04)

2B

2C

3A

3B

3C

4A

4B

4C

Calculate the DC component and ripple in the output signal across RL in the circuit shown in

Fig 3A. Assume V1dc=150V, V1RMS=15V and f=50HZ.

(03)

With the help of neat sketch explain the different current components of a BJT.

(03)

Using approximate h parameter circuit determine the current gain AI, Voltage gain AV and input

resistance Ri of voltage follower circuit shown in Fig 3C.

(04)

Determine VGS1, V1 and V

identical with Vt=1V,

for the MOSFET amplifier shown in Fig 4A. Both the MOSFET are

=2mA/V2. Neglect the channel length modulation effect.

(03)

With the help of neat circuit diagram explain the working of MOSFET based current mirror circuit. (03)

Draw the equivalent small signal circuit of the MOSFET amplifier shown in Fig 4C. Hence

determine the input resistance, output resistance and voltage gain. Assume

=0.25mA/V2,

Vt=1.5V and neglect channel length modulation effect.

5A

5B

5C

6A

6B

6C

(04)

With the help of neat circuit diagram explain the CMOS inverter

(02)

With the help of neat sketch derive an expression for conversion efficiency and maximum

efficiency of Class B Push pull amplifier.

(03)

A power amplifier of class A type with transformer coupling delivers a maximum of 20W to 4 ohm

load resistance. The Q point is adjusted for symmetrical clipping assuming fixed bias and VCC=20V.

Find i.) Turns ratio of transformer ii.) Slopes of AC and DC load line

iii.) Quiescent points

iv.) efficiency

(05)

Determine the VCE, output voltage output power and Zener Diode current for the circuit shown in

Fig 6A given = 100,VBE=0.7V.

(03)

From the fundamental derive an expression for the lower cut-off frequency of the amplifier due to

coupling capacitors.

(04)

Design a adujstable voltage regulato using LM317 regulator to get output voltage between 10 and

18V. Assume R1=1K,Vref=1.25V and Iadj=100 . Hence draw the circuit diagram.

(03)

Page 1 of 2

Department of Electrical and Electronics Engineering

V= 8 V

Vi

R=1K

C=1 0 F

I

10V

D1

10m s

V0

1K

D2

20m s

20V

R L= 3K

VZ = 10V

D1

2K

P ZM = 80mW

-10V

V0

D2

F ig 1 (C )

F ig 1 ( B)

D3

F ig Q 2 A

15V

4.5K

V1

120K

VL

R 1=5 0 0

Vi

500

B r idge

R e c t if ie r

50 F

R L=5K

=72

C 2= 1 5

10 F

F ull wa v e

A C in p u t

V0

10 F

10 F

C 1= 1 5

85K

F ig 3 A

F ig 2 ( B)

I= 1m A

12V

+ 15V

56K

1G

VGS 1

5K

c=

V1

ID = 2 m A

R L= 10K

c=

v0

36K

V2

1K

+

5V

_

1mA

vi

6.6K

V0

vi

F ig 4 C

5V

+

F ig . 3 C

F ig . 4 A .

Vi = 1 5 V

2 k

2 k

8V

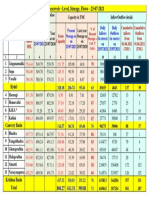

h- parameters

hi

hr

hf

h0

CE

1.1K

2.510-4

50

24mho

CB

1.1K

1

-51

25mho

CC

21.6 ohms

2.910-4

-0.98

0.49mho

Fig 6A

Page 2 of 2

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Topaz User Manual (Eng)Document418 pagesTopaz User Manual (Eng)mohanraj100% (5)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- PANCARATRA PradipaDocument262 pagesPANCARATRA PradipaHari Sukrawan100% (7)

- Narayana Upanishad PDFDocument9 pagesNarayana Upanishad PDFJeans Circuits80% (5)

- Mahanarayana Upanishad - With Translation PDFDocument382 pagesMahanarayana Upanishad - With Translation PDFphdpush100% (4)

- Narayana Upanishad PDFDocument9 pagesNarayana Upanishad PDFJeans Circuits80% (5)

- Implementation Checklist For ISO 9001 2015 Transition enDocument10 pagesImplementation Checklist For ISO 9001 2015 Transition enSagar Panda100% (1)

- Manual MitutoyoSJ 400 E4185 178Document14 pagesManual MitutoyoSJ 400 E4185 178Dana MadalinaNo ratings yet

- PWM Generation Using 8051 MicrocontrollerDocument3 pagesPWM Generation Using 8051 Microcontrollerveeramaniks40867% (6)

- Iso 14064 3 2019 en PDFDocument11 pagesIso 14064 3 2019 en PDFTatel River0% (1)

- Shneiderman's 8 Golden Rules of Interface Design: The Principles Questions To Consider Mark CompleteDocument1 pageShneiderman's 8 Golden Rules of Interface Design: The Principles Questions To Consider Mark CompletellNo ratings yet

- Udupi Bengaluru: 9:35 PM 5:55 AMDocument2 pagesUdupi Bengaluru: 9:35 PM 5:55 AMphdpushNo ratings yet

- 8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarDocument7 pages8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarPraveenMukatiNo ratings yet

- Fact Sheet For Vaccine Recipients & Caregivers: Restricted Use in Emergency Situation of Covid-19Document1 pageFact Sheet For Vaccine Recipients & Caregivers: Restricted Use in Emergency Situation of Covid-19nehaalluriNo ratings yet

- 8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarDocument7 pages8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarPraveenMukatiNo ratings yet

- Major Reservoir - Level, Storage, Flows - 25-07-2021Document1 pageMajor Reservoir - Level, Storage, Flows - 25-07-2021phdpushNo ratings yet

- Essence of Brahma Sutras PDFDocument335 pagesEssence of Brahma Sutras PDF23bhagaNo ratings yet

- 8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarDocument7 pages8.corruption Prevention Measures Recommended by Kautilya: Dr. Priti PohekarPraveenMukatiNo ratings yet

- Sage VikhanasacharyaDocument2 pagesSage VikhanasacharyaphdpushNo ratings yet

- Ambhrini Sukta Part2Document2 pagesAmbhrini Sukta Part2phdpushNo ratings yet

- Vimanas - King Ravana Ancient Flying Matchiens (V)Document6 pagesVimanas - King Ravana Ancient Flying Matchiens (V)Mohan Perera90% (10)

- Udaka Shanti - SanskritDocument111 pagesUdaka Shanti - SanskritsubrajuNo ratings yet

- Shrimadhawacharya: SRI C. KESAVA RAO, Bangalore Courtesy:Parimala Cultural MagazineDocument3 pagesShrimadhawacharya: SRI C. KESAVA RAO, Bangalore Courtesy:Parimala Cultural MagazinephdpushNo ratings yet

- Angirasa SmritiDocument6 pagesAngirasa SmritiKarthikeyan RamaswamyNo ratings yet

- Shanti Japam KannadaDocument168 pagesShanti Japam KannadaphdpushNo ratings yet

- Shanti Japam KannadaDocument168 pagesShanti Japam KannadaphdpushNo ratings yet

- Mahanarayana Upanishad - Swami Vimalananda (Sanskrit-English) C PDFDocument382 pagesMahanarayana Upanishad - Swami Vimalananda (Sanskrit-English) C PDFphdpush100% (1)

- BE AssignmentDocument15 pagesBE AssignmentphdpushNo ratings yet

- ASEE 13 Full Paper Final Submission PDFDocument7 pagesASEE 13 Full Paper Final Submission PDFphdpushNo ratings yet

- Tangents & Normal RDSADocument22 pagesTangents & Normal RDSAphdpushNo ratings yet

- Hydroform: Manual and Semi-Automated Corrosion MappingDocument2 pagesHydroform: Manual and Semi-Automated Corrosion MappingLEONARDOUS7No ratings yet

- 7528Document3 pages7528Oscar PereiraNo ratings yet

- Detroit Diesel 50 Engine Tech ManualDocument2 pagesDetroit Diesel 50 Engine Tech Manualayman akrabNo ratings yet

- W25P80 / W25P16 / W25P32: Formally Nexflash Nx25P80, Nx25P16 and Nx25P32Document43 pagesW25P80 / W25P16 / W25P32: Formally Nexflash Nx25P80, Nx25P16 and Nx25P32Dblogic GatesNo ratings yet

- ISO IEC 17025 2017 Transition TemplateDocument8 pagesISO IEC 17025 2017 Transition TemplateaasNo ratings yet

- Digital Logic Design Final ExamDocument12 pagesDigital Logic Design Final Examamanuel abrehaNo ratings yet

- Dr. M.Ashari/ ITS-Power Electronics 1Document6 pagesDr. M.Ashari/ ITS-Power Electronics 1Yuni TikaNo ratings yet

- Land Rover Workshop Manuals L322 Range Rover System Description and Operation AUTOMATIC TRANSMISDocument1 pageLand Rover Workshop Manuals L322 Range Rover System Description and Operation AUTOMATIC TRANSMISMark ErskineNo ratings yet

- Creating and Implementing User ControlsDocument15 pagesCreating and Implementing User ControlsGuillermo Pardos VázquezNo ratings yet

- Service FacilityDocument7 pagesService FacilityLouise ArlosNo ratings yet

- 1574158341-Resume AjayLanjewar QA 8YrsExp1Document7 pages1574158341-Resume AjayLanjewar QA 8YrsExp1ragunath90No ratings yet

- Digital Tool Evaluation FormDocument2 pagesDigital Tool Evaluation Formapi-627500441No ratings yet

- Iso 19114Document70 pagesIso 19114Ximena Garcia ReyesNo ratings yet

- Hybrid Power Generation SlideDocument23 pagesHybrid Power Generation SlideCnp1 Cnp1No ratings yet

- Action Technological PlanDocument22 pagesAction Technological PlanMarvin AbaoNo ratings yet

- Optical Fiber Dployment About PTCLDocument5 pagesOptical Fiber Dployment About PTCLamin ul haqNo ratings yet

- Admaterials Technologies Pte-Civil Operations ManagerDocument1 pageAdmaterials Technologies Pte-Civil Operations ManagerAkmalNo ratings yet

- Power Query Recipes May 2019Document60 pagesPower Query Recipes May 2019Vineeth BabuNo ratings yet

- Résumé: 120 "Shri Ram Kutir", Udhna, Pandesara, Surat-394210Document4 pagesRésumé: 120 "Shri Ram Kutir", Udhna, Pandesara, Surat-394210Raj AryanNo ratings yet

- Form-093-Dump Truck Safety ChecklistDocument2 pagesForm-093-Dump Truck Safety Checklistshamroz khan100% (2)

- IHub Services GuideDocument486 pagesIHub Services GuideHa HoangNo ratings yet

- схема и сервис мануал на английском Toshiba 46UL863R Ver 1.00Document138 pagesсхема и сервис мануал на английском Toshiba 46UL863R Ver 1.00Andrey ChersonNo ratings yet

- Artikel DiseminasiDocument3 pagesArtikel DiseminasiDinda Adila RamadantiNo ratings yet

- OOP VIMP Question - Super 25 - V2VDocument2 pagesOOP VIMP Question - Super 25 - V2VVIKASNo ratings yet