Professional Documents

Culture Documents

Como Programar y Cargar Un Programa en Una Nexys 2 (FPGA)

Uploaded by

Josue BustamanteOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Como Programar y Cargar Un Programa en Una Nexys 2 (FPGA)

Uploaded by

Josue BustamanteCopyright:

Available Formats

Dispositivos Lgicos Programables.

UNIVERSIDAD TECNOLOGICA DE

SALAMANCA

CARRERA:

Ingeniera en Mecatrnica

MATERIA:

Dispositivos Digitales Programables

GRUPO:

IMET 10 B

PROFESORA:

Ing. Margarita del Crystal Martnez C

INTEGRANTES:

Lpez Pia Nstor.

Manrquez Bustamante Mario Josu.

Ramrez Aguado Omar.

Salamanca, Gto., Octubre 30 de 2015

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

1 Introduccin

En este documento se presentan de manera detallada los pasos a seguir para

implementar un sistema digital en la tarjeta de desarrollo Nexys 2 de Digilent, desde el

planteamiento del problema hasta su puesta en marcha y verificacin en la tarjeta, la cual

contiene un FPGA Spartan- 3E XC3S500E de Xilinx. El ejemplo que se desarrolla es

bastante simple, porque el objetivo del tutorial no es resolver un problema complejo, sino

ilustrar el proceso de desarrollo.

Para el desarrollo del tutorial se requiere de las siguientes herramientas de Software:

Active-HDL versin 8.1: Herramienta desarrollada por Aldec, es empleada para la

captura y simulacin de las descripciones en VHDL.

ISE 14.7i de Xilinx: Es un ambiente integrado de desarrollo desde el que se invocan

diferentes herramientas, conforme se van requiriendo. Se utiliza para la sntesis,

implementacin y creacin del archivo de descarga. Tambin puede utilizarse para

programar al FPGA si se emplea una interfaz conocida como JTAG.

Adept de Digilent: Es una utilera que permite programar a los FPGAs en algunas

tarjetas desarrolladas por Digilent, a travs del puerto USB.

Para el Active-HDL y el ISE actualmente existen versiones ms recientes, se ocuparn

las que se han citado porque emplean menos recursos en su instalacin y son suficientes

para las aplicaciones a desarrollar.

2. Planteamiento del problema

Se desea disear e implementar un exhibidor de 7 segmentos esto se muestra en la figura

1.

Figura 1.

implementar.

3.

Diseo

Para

el

simulacin se

herramienta

versin 6.2,

por

Aldec,

acceso

muestra en la figura 2.

Manual de programacin para Nexys 2.

Circuito a

con VHDL

diseo

y

utilizar

la

Active-HDL

desarrollada

cuyo Icono de

directo

se

Dispositivos Lgicos Programables.

Figura 2. Programa active HDL 8.1

Este programa organiza los diseos en espacios de trabajo (workspace) si es la primera

vez que se ejecuta, deber crearse un nuevo espacio de trabajo, en caso contrario podr

usarse un espacio de trabajo existente.

En la figura 3 se observa cmo, aunque existan algunos espacios de trabajo, siempre es

posible iniciar con uno nuevo.

Figura 3. Iniciando con el programa Active-HDL

Un espacio de trabajo puede contener diversos diseos independientes. Si es la primera

vez que trabaja con esta herramienta, es conveniente iniciar con un nuevo espacio de

trabajo propio. Al cual deber asignrsele un nombre, en este caso se le puso tutorial

figura 4.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 4. Iniciando con un nuevo espacio de trabajo

Si se abre un espacio de trabajo existente, automticamente se abre el ltimo diseo

elaborado. Para los espacios de trabajo nuevos, se presenta el asistente para iniciar con

nuevos diseos, el asistente inicia con la ventana mostrada en la figura 5.

Figura 5. Creando un diseo en el espacio de trabajo.

La primera opcin se usa cuando ya se cuenta con mdulos que se agregarn al diseo.

La segunda es para importar un diseo completo.

La ltima opcin es necesaria para nuevos diseos, sta es la opcin que debe

seleccionarse y despus continuar con el paso siguiente.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Posteriormente se deben definir algunas caractersticas del diseo relacionadas con las

herramientas que se cuenten para sntesis e implementacin, y al tipo de FPGA sobre el

cual se realizar la descarga. Pero como esta versin de Active-HDL es muy previa a las

nuevas herramientas de Xilinx, no es posible relacionarlas, por ello, el Active-HDL slo

ser utilizado para describir y simular al circuito, no se seleccionan herramientas como se

muestra en la figura 6.

Figura 6. Diseo sin herramientas de sntesis.

A continuacin se tiene disponible al ambiente de trabajo completo de la herramienta, el

cual tiene un aspecto como el que se muestra en la figura 7.

3

1

2

Figura 7. Entorno de trabajo en la herramienta Active-HDL 6.2.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

En (1) se tiene un navegador en el que se puede seleccionar una de las 3 opciones

siguientes (con sus cejas inferiores):

Archivos (Files) Se muestran los archivos del diseo, organizados bajo un

esquema: Espacio de Trabajo (Workspace)-> Diseos -> Archivo. Un espacio de

trabajo puede contener varios diseos y un diseo a la vez puede contener varios

archivos (mdulos descritos en VHDL).

Estructura (Structure) Tiene sentido una vez que los mdulos han sido

compilados, muestra la organizacin del diseo, as como las seales internas,

externas y variables de cada uno de sus mdulos, esta opcin es til para

simulacin.

Recursos (Recursos) Muestra la organizacin en directorios de todos los

elementos que se agreguen al diseo activo.

En (2) se tiene una consola en la que aparecern mensajes de acuerdo con las

actividades realizadas por el usuario. Es solo con carcter informativo, no es posible

introducir informacin a travs de esta consola.

El espacio en (3) es el rea de trabajo, aqu se va a mostrar el contenido de cada uno de

los mdulos que integren a un diseo. Archivos con cdigo VHDL, ventanas de

simulacin, diagramas de bloques, etc. Basta dar doble clic dentro del navegador para

observar el contenido de un archivo y poder modificarlo.

Para agregar un nuevo archivo al diseo activo, en el navegador se debe dar doble clic en

la opcin Add New File (), se abre la ventana de la figura 8, para permitir insertar archivos

vacos, archivos existentes o usar uno de los asistentes (Wizards) para crear uno nuevo.

Figura 8. Ventana para insertar un nuevo archivo.

Lo ms simple es emplear uno de los asistentes, especficamente se debe seleccionar al

que apoya para crear un nuevo archivo empleando cdigo VHDL, como se muestra en la

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

figura 9. Los otros asistentes son para crear diagramas a Bloques (para mdulos con

mayor jerarqua), diagramas de estado o archivos en Verilog.

Figura 9. Agregando un nuevo archivo VHDL con ayuda del asistente.

Despus de aceptar, se va a iniciar con el nuevo mdulo, se deja activa la opcin de que

el cdigo generado se integre al proyecto y se avanza figura 10.

Figura 10. Creacin de un nuevo archivo VHDL con ayuda del asistente.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

A continuacin se debe escribir el nombre del archivo a crear y de manera opcional el

nombre de la entidad y de la arquitectura, si estos se omiten, todos los campos tomarn el

mismo nombre, que se decidi fuera comp4b figura 11.

Figura 11. Personalizando al nuevo archivo VHDL.

Luego se deben insertar una a una las seales que formarn parte de la entidad (interfaz),

la insercin de una seal comienza con un clic en el botn new, luego se le pone un

nombre, si es un vector su tamao se determina con los ndices y debe definirse su modo

(entrada o salida).

El proceso debe repetirse con cada una de las seales, de acuerdo a las especificaciones

del diseo. En la figura 12 se muestra el entorno mediante el cual se definen los puertos

que forman parte de la entidad, desde que se inserta la primera, hasta que todas han sido

incluidas.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 12. Ventana para definir los puertos que forman parte de la entidad.

Al concluir con la insercin de seales se presiona el botn finalizar, con lo que se crear

la plantilla del mdulo en el archivo Expo_7_segmentos, el cual es automticamente

abierto en el rea de trabajo, como se puede ver en la figura 13.

Figura 13. Plantilla creada a partir del asistente.

Los comentarios de la plantilla pueden completarse para una adecuada documentacin.

En este momento ya se tiene descrita la entidad (la interfaz del mdulo) y falta por

describir su arquitectura para determinar su comportamiento.

El tipo de dato generado por default es STD_LOGIC, el cual es una ampliacin del tipo Bit

con la caracterstica de que maneja otros niveles lgicos, adems de falso y verdadero,

como desconocido, alta impedancia, no importa, etc.

Nota: Si se quiere modificar la entidad, para agregar una nueva seal, eliminar una

existente o modificar algn parmetro, debe hacerse manualmente, respetando la sintaxis

de VHDL, no es posible regresar al asistente anterior.

El mdulo a desarrollar es una combinacin binaria, de manera que su comportamiento

puede determinarse por el proceso siguiente:

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 14. Insercin de un proceso en la arquitectura.

Una vez insertado el cdigo, se verifica su sintaxis realizando su compilacin. Para ello se

selecciona al archivo y se presiona al botn compilar. Otra alternativa consiste en obtener

un men contextual dando un clic derecho en el archivo y seleccionar la opcin de

compilacin (compile).

Si no hay errores de sintaxis, el archivo tendr otro marcador indicando su estado y la

consola reflejar el xito de la compilacin.

En caso de que hubiera errores, el archivo en el navegador quedar marcado de manera

diferente y los errores se mostrarn en la consola:

Los errores deben resolverse considerando la sintaxis del lenguaje.

4. Sntesis

La sntesis se va a realizar con las herramientas de Xilinx desde un Ambiente Integrado

de Software (Integrated Software Environment ISE) el cual se inicia con un doble clic en

el cono mostrado en la figura 15.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 15. Acceso directo para el Ambiente Integrado de Software (ISE) de Xilinx.

Al iniciar este programa se mostrar el Tip del Da y luego se abrir el ltimo proyecto en

el que se ha trabajado (excepto cuando es la primera vez que se ejecuta al software).

Para este tutorial se iniciar con un nuevo proyecto, dando un clic al botn New Project,

en los comandos para proyectos ubicados a la izquierda de la ventana,. Con ello se

obtendr el cuadro de dilogo mostrado en la figura 16.

Figura 16. Cuadro de dilogo para crear un nuevo proyecto.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Primero se debe seleccionar la ubicacin y el directorio de trabajo del nuevo proyecto y

luego se le debe asignar un nombre. El proyecto queda ubicado en una carpeta con el

mismo nombre.

En este caso, los proyectos se ubican en la carpeta C:\Practicas y el nuevo proyecto

llevar por nombre Expo_7_Segmentos. Para el tipo de mdulo superior (Top-level source

type) se mantiene HDL porque el comparador ya fue descrito en VHDL. En la figura 17 se

ha personalizado el cuadro de dilogo de la figura 31.

Figura 17. Definicin del nombre y ubicacin del nuevo proyecto.

Una vez que se introduzcan estos datos se debe proceder con el paso siguiente. En el

cual se definen las propiedades del proyecto relacionadas con el FPGA en el que se va a

realizar la descarga, por lo que es necesario seleccionar los valores correctos, incluyendo

el lenguaje preferido. En la figura 18 se muestran los valores que corresponden con el

FPGA que est integrado en las tarjetas de desarrollo Nexys 2.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 18. Informacin relacionada con el FPGA a utilizar.

Con un clic en Next se obtiene el resumen del proyecto mostrado en la figura 19, si los

datos con correctos, con el botn Finish se finaliza con la creacin del proyecto.

Figura 19. Resumen del proyecto.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Una vez que se cierra el cuadro de dilogo inicial se podr ver el entorno de desarrollo de

Xilinx, el cual se muestra en la figura 20.

2

3

Figura 21. Entorno de desarrollo de Xilinx.

En la figura 21 se distinguen cuatro reas principales:

1. rea de archivos. Se muestran los diferentes archivos fuente que integran al proyecto,

a manera de un rbol. Si un proyecto est formado por varios mdulos, en este rbol los

mdulos se ubicarn de acuerdo con sus niveles jerrquicos.

2. Espacio de trabajo. Ac sern abiertos los diferentes archivos fuente, reportes o

informacin de internet, inicialmente se muestra un resumen de la versin 14.7 del ISE

con ligas para mostrar sus diferentes caractersticas. Para abrir un archivo en el espacio

de trabajo, basta con dar doble clic a su nombre en el rea de archivos.

3. rea de procesos. Los procesos que se pueden aplicar a un archivo dependen de su

tipo. Una vez que se selecciona un archivo en el rea 1, en esta rea se mostrar una

lista con los procesos aplicables, por ello, la lista puede cambiar en funcin del tipo de

archivo.

4. rea de mensajes. Muestra una consola con mensajes indicando las diferentes

actividades que se estn realizando. Adems, existen otras cejas para mostrar errores o

precauciones.

Hasta el momento se tiene un diseo vaco, para agregar un archivo nuevo o copiar uno

existente se debe dar un clic derecho en el rea de archivos para obtener el men

contextual que permitir hacerlo, en la figura 22 se muestra el citado men.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 22. Men contextual para agregar archivos nuevos o existentes.

Puesto que el archivo en VHDL del comparador ya fue realizado, se debe seleccionar la

opcin Add Copy of Source, para copiar el archivo en la carpeta del proyecto. Con un clic

en esta opcin se abre una ventana de navegacin en la que se debe buscar al archivo

Expo_7_segementos.vhd, el cual se encuentra en la ruta: my_designs -> tutorial ->

comparador -> src, esto porque el Active-HDL trabaja en la carpeta denominada

my_designs, el espacio de trabajo se denomin tutorial, en el cual se inici con un diseo

denominado comparador, y todos los diseos dejan los archivos del cdigo fuente en una

carpeta denominada src.

En la figura 23 se muestra el cuadro de dilogo resultante de agregar al archivo, en la

columna Association se debe dejar la opcin All, lo que significa que el archivo podr ser

empleado para sntesis y simulacin.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 23. Archivo agregado al proyecto.

Al presionar OK en la figura 23 se tendr al archivo Expo_7_segementos.vhd en el rea

de archivos y en el espacio de trabajo se mostrar un resumen del proyecto. Puesto que

el archivo Expo_7_segementos.vhd est seleccionado, en el rea de procesos se

muestran los procesos que son aplicables a un archivo de este tipo, esto se observa en la

figura 24.

Figura 24. Archivo Expo_7_segementos.vhd agregado al proyecto.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Con el archivo Expo_7_segementos.vhd seleccionado se realiza su sntesis. Para ello, en

el rea de procesos se da un doble clic al proceso de sntesis, si no hay errores de

sintaxis, en el proceso de sntesis aparecer la indicacin de que se realiz con xito y la

consola reflejar el mismo hecho. Ambas indicaciones se pueden ver en la figura 29.

Figura 29. Proceso de sntesis realizado con xito.

En caso de que hubiera errores, el proceso de sntesis no sera superado y el error se

mostrara en el espacio de la consola, en la ceja de errores tambin se mostrara la

posicin del error.

Se esperara que no ocurrieran errores, dado que el mdulo Expo_7_segementos.vhd ya

fue evaluado con el Active-HDL, sin embargo, si se realiza algn ajuste en el cdigo VHDL

que genere algn error, ste debe resolverse considerando la sintaxis del lenguaje, en la

figura 30 se muestra un error al quitar un ; en el archivo Expo_7_segementos.vhd.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 30. Proceso de sntesis realizado con xito.

5. Acondicionamiento para la implementacin.

Como pudo observarse en las figuras siguientes, el cdigo VHDL ha sido sintetizado

satisfactoriamente en hardware, ahora se deben tomar en cuenta algunas

consideraciones para poder llevar a cabo su implementacin en el dispositivo.

El comparador ser descargado en un FPGA XC3S500 de Xilinx, el cual est en una

tarjeta Nexys 2 de Digilent, cuya imagen se muestra a continuacion. Digilent es la

empresa que manufactura estas tarjetas de desarrollo y su manual de referencia puede

obtenerse de su sitio web: www.digilentinc.com. Se observa que la tarjeta tiene diferentes

elementos para entrada/salida o almacenamiento de datos.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 31. Tarjeta Nexys 2, incluye un FPGA Spartan-3E de Xilinx.

Para la implementacin del comparador, es de esperarse que las entradas A y B se

obtengan de los interruptores, y las salidas: Mayor, Menor e Igual, se muestren en los

LEDs. Por lo tanto, se requiere conocer a que terminales del FPGA estn conectados

estos elementos.

En la figura 32 se muestra la organizacin de las terminales en el FPGA, se observa una

disposicin matricial organizada en 4 bancos. Para referirse a una terminal, debe

indicarse el rengln (A-V) y la columna (1-18).

Figura 32. Terminales del FPGA Spartan-3E de Xilinx incluido en la tarjeta Nexys 2.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

En la figura 33 se muestra a que terminales del FPGA estn conectados los dispositivos

bsicos de entrada/salida. Sera necesario revisar el manual de la tarjeta si se va a

emplear alguna interfaz especializada, como RS-232, PS/2 o VGA; o bien, si se va a

manejar alguna de las memorias incluidas en la misma Nexys 2.

Figura 33. Conexin del FPGA con los dispositivos bsicos de entrada/salida, en la tarjeta

Nexys 2.

Con la aplicacin PlanAhead es posible revisar la correcta ubicacin de los pines en un

entorno grfico. En la figura 34 se muestra la ejecucin de esta aplicacin, con la salida

igual seleccionada en la ventana I/O Ports, poniendo en color blanco a la terminal, tanto

en el empaque (Package) como en el dispositivo (Device).

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 34. Muestra grfica de la ubicacin de las terminales con la aplicacin PlanAhead.

La aplicacin PlanAhead se invoca seleccionando al archivo VHDL del comparador en el

rea de archivos y expandiendo la opcin User Constrains en el rea de procesos, para

posteriormente ejecutar al proceso I/O Planning (PlanAhead), como se muestra en la

figura 59.

Figura 34. Proceso para invocar a la aplicacin PlanAhead.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Existen otros tipos de restricciones, de rea o temporizacin, pero stas requieren

definiciones que son mucho ms complejas.

6. Implementacin.

La implementacin es un proceso que involucra varios pasos: Trasladar el diseo

(Traslate), mapearlo (Map) y realizar su colocacin y ruteo (Place & Route). Sin embargo,

estos procesos los realiza la herramienta de manera automtica. Para ello, es necesario

seleccionar el archivo Expo_7_segementos en el rea de archivos, con lo que se abrirn

los procesos aplicables al archivo, entre los cuales se debe buscar la lista de procesos

Implement Design y darle un doble clic para ejecutarlos, en la figura 35 se muestra la

realizacin con xito de la Implementacin, con todas sus etapas.

Figura 35. Implementacin del diseo.

En el resumen del proyecto (que se muestra en el rea de trabajo) se pueden ver los

recursos que est usando el diseo dentro del FPGA, estos se observan en la figura 36.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 36. Resumen de recursos utilizados en el diseo.

Una vez hecho esto es posible ejecutar al proceso Generate Programming File

aplicndole un doble clic. Si el proceso se realiza con xito, se obtendr un estado de

xito, como se muestra en la figura 37.

Figura 37. La generacin del archivo de programacin se realiz con xito.

En este momento ha sido creado al archivo con extensin BIT que ser descargado en el

FPGA, por lo tanto, para descargas en la tarjeta Nexys 2 empleando la interfaz USB ya es

posible cerrar al ISE de Xilinx.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

7. Programacin del dispositivo

La tarjeta puede programarse desde dos diferentes puertos, el puerto JTAG o un puerto

mini-USB, el programa puede enviarse directamente al FPGA o a una FLASH, para que el

FPGA cargue el programa automticamente, despus de que es alimentada la tarjeta.

Figura 38.

programar al

Interfaz para

FPGA.

En este caso

cable

USB,

utilizar

un

denominado

proporcionado

por Digilent, el

del programa

muestra en la

se utilizar un

para ello se

programa

Adept,

gratuitamente

acceso directo

Adept

se

figura 39.

Figura 39. Acceso directo del programa Adept.

En la tarjeta Nexys 2 es conveniente colocar el conector de Modo en la posicin de JTAG,

en lugar de ROM, para que no afectar el contenido de la memoria, en la figura 40 puede

verse el selector de modo, por debajo de la interfaz JTAG. La memoria ROM est

configurada con un programa de prueba utilizado para verificar la funcionalidad de la

tarjeta y no debe ser modificado.

Figura 40.

tarjeta.

Conectores de la

Antes de ejecutar al

programa

Adept

debe conectarse la

tarjeta Nexys a la PC

y energizarse, sino

se

manejan

elementos

de

hardware adicionales

en los conectores

de la tarjeta, como

ocurre

en

este

ejemplo,

la

alimentacin de la

tarjeta

puede

tomarse del puerto

USB de la PC.

La

ventana

del

programa Adept se

muestra en la figura

41. Si la tarjeta no

est conectada o est apagada, slo se mostrar un mensaje pidiendo que se verifiquen

las conexiones. Arregladas las conexiones ser suficiente con presionar al botn Initialize

Chain para que el programa reconozca a la tarjeta y se obtenga la ventana de la figura 41.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

Figura 41. Interfaz del programa Adept, una vez que la tarjeta Nexys 2 ha sido

reconocida.

Con el botn Browse relacionado con el FPGA, se busca al archivo con extensin BIT en

la carpeta del proyecto y se programa al FPGA presionando al botn Program. No se

utilizan los botones relacionados con la PROM, para no alterar su contenido. En la parte

inferior de la ventana se observar el progreso de la programacin, como se muestra en

la figura 42.

Figura 42. Progreso en la programacin del FPGA.

El programa ADEPT, adems de emplearse para descargar el programa en el FPGA o en

la PROM, puede emplearse para verificar la integridad de la tarjeta, por medio de

diferentes pruebas en sus recursos.

Despus de la programacin, el programa ADEPT ya puede cerrarse. Si la tarjeta est

alimentada con un eliminador, el cable USB puede retirarse.

El diseo puede evaluarse modificando las entradas desde los interruptores para observar

las salidas en los dispays.

Cabe aclarar que los recursos programables en el FPGA estn basados en tecnologa

RAM, por lo que si se retira la alimentacin, el programa se perder. Para evitar esto, el

programa podra almacenarse en la memoria FLASH, lo cual se evitar para mantener el

programa de demostracin. Sin embargo, es conveniente aclarar que en la PROM no se

puede programar un archivo con extensin BIT, primero debera generarse el archivo para

la PROM desde el ISE de Xilinx.

Manual de programacin para Nexys 2.

Dispositivos Lgicos Programables.

8. Conclusin

Se ha revisado de manera detallada el proceso a seguir para implementar sistemas

digitales en FPGAs con ayuda de VHDL, para otro tipo de tarjetas u otro tipo de FPGAs

slo debe hacerse la seleccin adecuada del dispositivo y la ubicacin correcta de las

terminales de entrada y salida.

Se utilizaron 2 herramientas principales durante el proceso, y se pudo observar que la

simulacin de un diseo con el Active-HDL es mucho ms simple e ilustrativa que la

simulacin en el mismo entorno de Xilinx, dado que en el ISE se requiere la creacin de

otro archivo VHDL como banco de pruebas.

Si no se tiene xito en la programacin, las causas pueden ser diversas:

La tarjeta puede estar desconectada.

Se seleccion un FPGA que no corresponde con el de la tarjeta.

El empaque seleccionado no es el empaque del FPGA.

El puerto o el cable USB no funcionan correctamente.

El FPGA no funciona correctamente.

Manual de programacin para Nexys 2.

You might also like

- Practica No.2 - VHDLDocument5 pagesPractica No.2 - VHDLDavid Sandoval FriasNo ratings yet

- PRACTICA No.3Document7 pagesPRACTICA No.3David Sandoval FriasNo ratings yet

- VHDLDocument24 pagesVHDLErik RomeroNo ratings yet

- Practica No.4 - Sandoval Frias DavidDocument10 pagesPractica No.4 - Sandoval Frias DavidDavid Sandoval FriasNo ratings yet

- Curso Pic c18Document39 pagesCurso Pic c18manuel_gutarraNo ratings yet

- VHDL ContadorDocument3 pagesVHDL Contadorgaby_lizzylr929154No ratings yet

- Programación en VHDLDocument17 pagesProgramación en VHDLsinchyNo ratings yet

- 06 - Diseño MSI Con VHDL - 1Document15 pages06 - Diseño MSI Con VHDL - 1Levis BrisaNo ratings yet

- Curso Pic c18Document39 pagesCurso Pic c18GermanEG1989No ratings yet

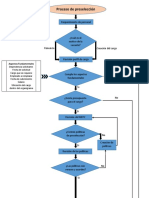

- Proceso de Preselección: Aspectos FundamentalesDocument4 pagesProceso de Preselección: Aspectos FundamentalesSILVIA ERMENCY ERASO HANRRYRNo ratings yet

- Practica 2 PicoBlazeDocument24 pagesPractica 2 PicoBlazeAntonio David EscobarNo ratings yet

- Proceso de VentasDocument1 pageProceso de VentasLorena JimenezNo ratings yet

- Manual XilinxDocument15 pagesManual XilinxPakitoCachorrosNo ratings yet

- Thymeleaf ControladoresDocument8 pagesThymeleaf ControladoresMikiNo ratings yet

- Introduccion Al VHDLDocument145 pagesIntroduccion Al VHDLJuan Sebastián PatarroyoNo ratings yet

- Plantillas HTML5 en Java Con ThymeleafDocument13 pagesPlantillas HTML5 en Java Con ThymeleafPedroManuelCubaNo ratings yet

- Curso en C para Pic CcsDocument91 pagesCurso en C para Pic CcsLeonardo CorredorNo ratings yet

- Informe Del Primer LaboratorioDocument10 pagesInforme Del Primer LaboratorioEdward Condor LopezNo ratings yet

- Programación de Circuitos Lógicos en VHDLDocument26 pagesProgramación de Circuitos Lógicos en VHDLCheynNo ratings yet

- Vectores y ApliacionesDocument50 pagesVectores y Apliacioneseliza humpiriNo ratings yet

- Proyecto Controlador VGADocument21 pagesProyecto Controlador VGALuis Miguel Villacorta BecerraNo ratings yet

- Máquinas de Estado MooreDocument10 pagesMáquinas de Estado MooreJoselyne NievesNo ratings yet

- Apuntes VHDLDocument54 pagesApuntes VHDLGabo HernandezNo ratings yet

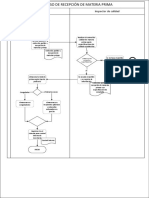

- Recepción de Insumos y Mat PrimaDocument1 pageRecepción de Insumos y Mat PrimaLeonardo Stiven Borja ParedesNo ratings yet

- Creacion de Un Analizador Lexico en JavaDocument7 pagesCreacion de Un Analizador Lexico en JavaJairo Calle100% (1)

- Programas en JavaDocument26 pagesProgramas en JavarosveronNo ratings yet

- Ejercicios de Arduino ResueltosDocument31 pagesEjercicios de Arduino ResueltoscoraztoNo ratings yet

- LaTeX Otras HerramientasDocument14 pagesLaTeX Otras HerramientasAndrésFelipeGutiérrezRiveraNo ratings yet

- Diseño de Circuitos Digitales Con VHDL Serv SocialDocument149 pagesDiseño de Circuitos Digitales Con VHDL Serv SocialLuis Antonio Leal LópezNo ratings yet

- Diseño de Una PCBDocument10 pagesDiseño de Una PCBUrieta Vázquez CarlosNo ratings yet

- 2 React Native - Snack y Primeras AppDocument36 pages2 React Native - Snack y Primeras AppCOn EtLyNo ratings yet

- Introduccion A JavascriptDocument123 pagesIntroduccion A JavascriptYoryi AbreuNo ratings yet

- Programacion de Sistemas Digitales Con VHDLDocument35 pagesProgramacion de Sistemas Digitales Con VHDLNicolas CastilloNo ratings yet

- Tutorial BluetoothDocument24 pagesTutorial BluetoothWilliam Garcia BedoyaNo ratings yet

- 9 - Programación WebDocument42 pages9 - Programación WebPicassoNo ratings yet

- Arquitecturas EscuelaDocument4 pagesArquitecturas EscuelaCarlos Eduardo GarciaNo ratings yet

- Funciones IntellijDocument4 pagesFunciones IntellijAlxndr ColumbaNo ratings yet

- ProcessingDocument94 pagesProcessingkassan4791No ratings yet

- Dibujos KawaiDocument25 pagesDibujos KawaiSara CruzNo ratings yet

- Práctica 1 Diseño LógicoDocument7 pagesPráctica 1 Diseño LógicoGael SierraNo ratings yet

- Thymeleaf Upload FilesDocument2 pagesThymeleaf Upload FilesSandro AnayaNo ratings yet

- Semana6 Arduino PLCDocument56 pagesSemana6 Arduino PLCManuel Sanchez CheroNo ratings yet

- Introducción A La Programación en PHPDocument25 pagesIntroducción A La Programación en PHPRicardo Quijije SantosNo ratings yet

- Scratch Secundaria TrabajoDocument5 pagesScratch Secundaria Trabajocarolina ramirezNo ratings yet

- Validaciones VB NetDocument27 pagesValidaciones VB NetcarfergomNo ratings yet

- JDBC OracleDocument118 pagesJDBC OracleJesus Alberto OspinaNo ratings yet

- Introducción A API de Google MapsDocument12 pagesIntroducción A API de Google MapsGuillermo CastilloNo ratings yet

- Rubrica II Unidad Programacion Visual I 2da VersionDocument2 pagesRubrica II Unidad Programacion Visual I 2da VersionoscarfernandosbNo ratings yet

- Introducción A La Programación 3456 230304 PDFDocument113 pagesIntroducción A La Programación 3456 230304 PDFJuan Francisco Pulido CarrilloNo ratings yet

- Programación VisualDocument8 pagesProgramación VisualMayra PuentesNo ratings yet

- Calculadora en Python (Tkinter)Document16 pagesCalculadora en Python (Tkinter)Miguel GaitanNo ratings yet

- Estrutucturas Algoritmicas RepetitivasDocument5 pagesEstrutucturas Algoritmicas Repetitivasingmarco72No ratings yet

- Temario Desarrollo Aplicaciones WebDocument12 pagesTemario Desarrollo Aplicaciones WebGpe NayeliNo ratings yet

- Taller Programación de Arduino IIDocument4 pagesTaller Programación de Arduino IIolmar24100% (1)

- ME Lab02 - Introducción Al Entorno de XilinxDocument20 pagesME Lab02 - Introducción Al Entorno de XilinxDIONEL ROPERO TORRESNo ratings yet

- ISE XilinxDocument4 pagesISE XilinxWilliam Chávez0% (1)

- Quartus Compuerta XnorDocument24 pagesQuartus Compuerta XnorDavid Gamboa GuzmánNo ratings yet

- Tutorial XilinxDocument40 pagesTutorial XilinxJavier EspinozaNo ratings yet

- Sistemas Digitales Con FPGA - Labotec PerúDocument14 pagesSistemas Digitales Con FPGA - Labotec PerúJhonatan Juño GarciaNo ratings yet

- Mux2a1 TutorialDocument30 pagesMux2a1 TutorialelkillyNo ratings yet

- Como Programar y Cargar Un Programa en Una Nexys 2 (FPGA)Document26 pagesComo Programar y Cargar Un Programa en Una Nexys 2 (FPGA)Josue BustamanteNo ratings yet

- Tipos de Distribucion de Planta NormatividadDocument10 pagesTipos de Distribucion de Planta NormatividadJosue BustamanteNo ratings yet

- Sistemas de ManufacturaDocument6 pagesSistemas de ManufacturaJosue BustamanteNo ratings yet

- Reporte de BlankitoDocument14 pagesReporte de BlankitoJosue BustamanteNo ratings yet

- PsicoanalisisyescrituraDocument10 pagesPsicoanalisisyescrituraRodrigoFaríasVelosoNo ratings yet

- Apuntes de SaeDocument20 pagesApuntes de SaeYuli MontoyaNo ratings yet

- 3 Diseño de Circuitos Combinatorios y Secuenciales NeumáticosDocument166 pages3 Diseño de Circuitos Combinatorios y Secuenciales NeumáticosJuan C Cruz l100% (1)

- 20190819093914horario 2019 IiDocument81 pages20190819093914horario 2019 Iimsoto20052576No ratings yet

- Herramientas Google DriveDocument6 pagesHerramientas Google DriveJordan Vasquez50% (2)

- Carrasola González Marcello PDFDocument92 pagesCarrasola González Marcello PDFAnghel CarreroNo ratings yet

- Solución Álgebra Lineal ESPOL 2016 2TDocument5 pagesSolución Álgebra Lineal ESPOL 2016 2TÁngel Guale100% (4)

- Pruebas de Caja Negra y deDocument3 pagesPruebas de Caja Negra y dedhamaryz50% (2)

- Venta de Zapatillas AdidasDocument3 pagesVenta de Zapatillas Adidasmarlon salvaNo ratings yet

- CEP1 Ejercicios SDocument15 pagesCEP1 Ejercicios SNayla Estefania100% (1)

- Calidad en Gestion de Servicios de TIDocument20 pagesCalidad en Gestion de Servicios de TIJuan TzununNo ratings yet

- Tain - B02T03 - Estructuras Datos PDFDocument17 pagesTain - B02T03 - Estructuras Datos PDFkumoNo ratings yet

- Examen de PrimariaDocument5 pagesExamen de PrimariaBruce GuzmanNo ratings yet

- Tarea ED06Document5 pagesTarea ED06Raul Puro0% (1)

- P025a Tahoe 2008Document2 pagesP025a Tahoe 2008cittadino1No ratings yet

- HORARIOS PNF INFORMÁTICA Nuevo 2022-1 Malla B - CDocument7 pagesHORARIOS PNF INFORMÁTICA Nuevo 2022-1 Malla B - CMelvin José Romero GonzalezNo ratings yet

- Inka KolaDocument4 pagesInka KolapapoNo ratings yet

- ODBCDocument36 pagesODBCWolfernand VelaNo ratings yet

- Limites 2013Document27 pagesLimites 2013jimena96cmNo ratings yet

- Teoria de ConjuntosDocument16 pagesTeoria de Conjuntoschepeto316No ratings yet

- Nivelacion 2 PDFDocument16 pagesNivelacion 2 PDFjersonNo ratings yet

- Agile Data MiningDocument8 pagesAgile Data MiningAlex ArmendàrizNo ratings yet

- Proyecto CriptogramasDocument1 pageProyecto CriptogramasLuis Eduardo EstradaNo ratings yet

- BRUNERDocument23 pagesBRUNERMónicaRiccaNo ratings yet

- Gramaticas de Libre Contexto Heder Julio SalgadoDocument4 pagesGramaticas de Libre Contexto Heder Julio SalgadohederjuliosalgadoNo ratings yet

- Inteligencia Artificial Un Enfoque Moderno Stuart J RussellDocument7 pagesInteligencia Artificial Un Enfoque Moderno Stuart J Russelljose coelloNo ratings yet

- Ifcd0111 FicDocument42 pagesIfcd0111 FicAna MorazaNo ratings yet

- Java en NetBeans - Ejercicios Guiados PDFDocument607 pagesJava en NetBeans - Ejercicios Guiados PDFJoe Luis Calderón ChávezNo ratings yet

- Cadena CustodiaDocument7 pagesCadena CustodiaInformatica MusacNo ratings yet

- Manual Operacion HRP NominaDocument225 pagesManual Operacion HRP NominaIvan CandelasNo ratings yet