Professional Documents

Culture Documents

Iman Pid Control

Iman Pid Control

Uploaded by

Iman PeykarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Iman Pid Control

Iman Pid Control

Uploaded by

Iman PeykarCopyright:

Available Formats

dsPIC30F Motor Control PWM Module

DS

Digital Signal Controller

dsPIC30F Motor Control PWM

Module

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

Welcome to the dsPIC30F Motor Control PWM Module web seminar.

Microchip Technology Inc.

Page 1

dsPIC30F Motor Control PWM Module

Session Agenda

O

O

O

O

O

O

O

O

MC Peripheral Overview

PWM Time Base and Period Setting

Duty Cycle Programming

Dead Band Generators

Output Override

Fault pins

A/D Converter Syncronization

MC PWM in Power Safe Modes

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

Here is the agenda for todays seminar.

We will talk about the general structure of the peripheral and then we will have

some details on the period generator and the duty cycle generators. The

different drive capabilities of the output pins will be targeted and we will see

how dead bands help in preventing damages or even the destruction of the

external power stages. The fault pins can help us in this as well.

The A/D syncronization capability permits us to select the exact timing for

starting the conversion.

At the end we will see how the peripheral behaves in the idle and sleep modes,

that is in the power save modes.

Microchip Technology Inc.

Page 2

dsPIC30F Motor Control PWM Module

MCPWM Features

O

Dedicated time base with TCY/2 edge resolution

Complementary or independent outputs

Hardware dead time generators

Output pin polarity set with configuration bits

Multiple output modes

Manual override

Fault pins

Special event trigger for A/D conversion

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

The peripheral uses a dedicated timer for the generation of the PWM

frequency. Its maximum input frequency is the instruction cycle frequency Fcy,

but the duty cycle edge resolution can be enhanced half an instruction cycle for

improved performances.

The peripheral pins can be coupled to give complementary outputs or used as

single ended pins. In both cases the polarity (active high or active low) can be

set as part of the configuration bits.

The implementation of external bridge power circuits requires that the

peripheral should be capable of adding dead times between the commutations

of the two complementary outputs in order to avoid short circuits through the

power transistors. An added safety feature are the fault pins that are capable of

disabling in a very short time the PWM outputs so that fault conditions in the

power section of the board are not destructive to the circuitry.

In many motor control applications, like BLDC motors, it is required that the

firmware be able to replace the PWM output with a constant low or high output

signal: the manual override function is what helps in these situations.

For sensorless control of BLDC motors, the necessity of synchronizing the

PWM output to the A/D converter arises. This allows the designer to select the

correct timing for sampling the back emf to determine the run-time position of

the rotor.

Microchip Technology Inc.

Page 3

dsPIC30F Motor Control PWM Module

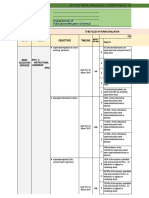

MC PWM Block Diagram

16-bit Time-base

PWM4H

Duty Cycle

Generator #4

Dead Time Unit

PWM4L

Duty Cycle

Generator #3

PWM3H

Dead Time Unit

PWM Override

Logic

Duty Cycle

Generator #2

Four PWM output

pairs with output

polarity control

PWM2H

Dead Time Unit

PWM2L

PWM1H

Duty Cycle

Generator #1

PWM3L

Dead Time Unit

A/D Conversion

Trigger

2005 Microchip Technology Incorporated. All Rights Reserved.

PWM1L

Fault A

Fault B

Two fault pins w/

programmable fault

states

dsPIC30F Motor Control PWM Module

The high level block diagram of the Motor Control PWM module is shown.

We can see the PWM period generator at the top left, the 16-bit Time Base.

The dsPIC is capable of generating up to four output PWM signals, with the

same period but different duty cycles. There are four such units in devices with

64 or more pins.

The Duty cycle generators are followed by the dead time units. The outputs

from these units go through the PWM Override Logic and finally to the output

pins. The output pins are grouped in pairs, to facilitate driving the low side and

high side of a power half-bridge.

The safety fault feature is directly connected to the output stages of the

peripheral in order to have the smallest possible response time.

At the bottom left we can also find the A/D Conversion trigger block.

Microchip Technology Inc.

Page 4

dsPIC30F Motor Control PWM Module

MC-PWM Timebase

O

Dedicated 15-bit time-base, period register

O Up count (edge align), up/down count (center align)

PWM resolution : Tcy/2

For Example:

O At 20 MIPS: 19.5 KHz @ 11 bit

i.e. 11 bit resolution above audible frequencies

O PWM interrupt every 1-16 periods

1:1, 1:4, 1:16, or 1:64 prescaler options

PTCON Register

PTEN

bit15

14

PTSIDL

13

12

11

10

bit8

PTMOD1

PTMOD0

bit0

PTOPS3

PTOPS2

PTOPS1

PTOPS0

bit7

2005 Microchip Technology Incorporated. All Rights Reserved.

PTCKPS1 PTCKPS0

3

dsPIC30F Motor Control PWM Module

The time base is generated by a 15 bit timer called PTMR with a prescaler

which divides the timebase frequency by 1, 4, 16 or 64. Bit 15 of the PTMR

register indicates the count direction: 0 indicates an upward count and 1

indicates a downward count. This feature allows the unit to generate edge

aligned and center aligned PWM waveforms, as we will see shortly.

The timer content is continuosly compared with the value of the preset period

register. When a period match occurs, an interrupt to the CPU is generated.

The module can be configured to generate an interrupt after up to 16 period

match events. This feature reduces the CPU overhead, since in many

applications the duty cyle value need not be changed one every PWM cycle.

Though the clock to the time base timer is Tcy, the duty cycle resolution is

Tcy/2; this feature can be utlized to obtain finer PWM resolution at lower device

operating speeds, e.g., 11 bits of resolution at 19.5 Khz using a 20 MHz clock.

The PTCON register is used to switch the timer on and off, to halt it in IDLE

mode, to set the prescaler and postscaler value and to select one of the four

operating modes of the peripheral: free running mode, single event mode,

continuos up/down mode, countinuos up/down with double PWM update. We

will discuss these modes in the following foils.

Microchip Technology Inc.

Page 5

dsPIC30F Motor Control PWM Module

Edge Aligned PWM

DUTY CYCLE

UPDATE

PTPER

PDC1

PTMR COUNT

PDC2

Time

PWM1H

PWM2H

INTERRUPTS

PERIOD REGISTER

RELOAD

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

The edge aligned PWM is generated when the time base is operating in Free

Running mode

At the beginning of each period the outputs are driven active (high in this

example). As soon as the timer value, while counting up, matches the value in

any duty cycle register (PDC1, PDC2, and so on), the output is driven inactive

(low here).

The duty cycle registers are updated when the timer register is reset to zero

and start counting up again. The application software can update the duty cycle

value at any time during the period.

Duty cycles from 0% to 100% are allowed.

An interrupt is generated, if enabled, when the timer resets, due to a match with

the PTPER register.

In order to avoid glitches the duty cycle registers are double buffered.

In the figure only two out of four duty cycle registers and outputs are shown.

Microchip Technology Inc.

Page 6

dsPIC30F Motor Control PWM Module

Single Event PWM

PTPER

PDC1

PDC2

Time

PWM1H

PWM2H

INTERRUPT

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

The Single Event feature alllows to generate a single output pulse. Setting the

PTEN enable bit in the PTCON register the timer starts counting up; the bit will

be automatically reset when the timer resets and stops counting.

An interrupt is generated, if enabled, when the timers resets.

When the PTEN bit is set, the I/O pins are driven to their active state: they will

be driven to the inactive state again when a match with a duty cycle register

occurs.

Microchip Technology Inc.

Page 7

dsPIC30F Motor Control PWM Module

Center Aligned PWM

DUTY CYCLE UPDATE

PTPER

PDC1

PDC2

Time

PWM1H

PWM2H

INTERRUPTS

PERIOD

REGISTER

RELOAD

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

In the center aligned mode, the time base is an up-down counter: it starts from

zero, counts up to the value in the period register and then counts down to zero

and so on. Bit 15 in the timer register indicates the counting direction. In this

mode, the PWM period is twice the time base period.

The duty cycle buffers are updated when the timer is reset to zero; the interrupt

flag is set at the same time.

As you can see from the figure, the PWM waveform is centered around the

instant in time when the timer reaches its maximum value and start counting

back: from this the name center aligned.

Although the PWM frequency is half the edge aligned PWM, this mode is very

useful because it avoids the simultaneous switching of all the PWM outputs at

the same time. This is not a problem for the device itself, but since power

switches are connected to these outputs, the switching current can be quite

high and may require an oversized power supply.

Microchip Technology Inc.

Page 8

dsPIC30F Motor Control PWM Module

Center Aligned PWM with

Double Update

DUTY CYCLE

UPDATE

PTPER

PDC1

PDC2

Time

PWM1H

PWM2H

INTERRUPTS

PERIOD

REGISTER

RELOAD

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

This mode is quite similar to the previous one. The time base operates in a

continuous up/down count mode.The main difference is that the duty cycle

buffer update is done twice per period: when the timer reaches zero and when it

counts to the upper limit.

The advantage is that the output PWM waveform is no more symmetrical.

Again the interrupt flags are set when the timer reaches zero.

Microchip Technology Inc.

Page 9

dsPIC30F Motor Control PWM Module

Dead Time Control

O

O

O

O

O

Applies only to pin pairs in complementary mode

Two programmable dead times

One dead time per pair for multiple inverters OR

Two dead times per pair for distortion optimization

Tcy minimum resolution with four pre-scale options

Dead Time A

Dead Time B

PWM1H

PWM1H

PWM1L

PWM1L

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

10

The dead time unit immediately follows the duty cycle generators and applies

only in complementary mode. Since power switches in the high and low sides

usually have different on and off times, if both were operated at the same time it

is possible that the two transistors in a complementary pin-pair are switched on

simultaneously for a short duration: this causes a short circuit betweeen the

supply rails and a huge amount of current flows through the devices, potentially

causing damage to the system.

The solution is to delay the switching of the two transistors by adding a small

amount of time between the falling edge of one pin and the rising edge of the

other.

You can select one or two different dead times; the devices with 6 output pins

provide one dead time whereas those with 8 outputs have two. Having 2 dead

time units is useful in 2 ways. First, to compensate for the difference in the

switching times of the 2 transistors in the same complementary pair. Second, to

enable control of different motor drive circuits using different complementary

pin-pairs.

Microchip Technology Inc.

Page 10

dsPIC30F Motor Control PWM Module

Dead Time Registers

O

DTCON1 selects dead time value for A and B

DTBPS1

DTBPS0

DTB<5:0>

14

bit15

DTAPS1

DTAPS0

bit7

13

12

11

10

bit8

bit0

DTA<5:0>

5

DTCON2 selects which dead time value is assigned

to the active(A) or inactive(I) edge of each generator

-

bit15

14

13

12

11

10

bit8

DTS4A

DTS4I

DTS3A

DTS3I

DTS2A

DTS2I

DTS1A

DTS1I

bit7

bit0

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

11

Two registers are used to enable and program the dead band generator. It is

based on a 6 bit down counter with a maximum clock frequency of Fcy

optionally divided by a 1:2, 1:4 or 1:8 prescaler.

Register DTCON1 selects the period match value and the prescaler for both

dead time generators, called A and B.

Register DTCON2 allows selection of the dead time unit (A or B) for each

output pin (low and high) and for each edge (rising an falling). Thus, the

designer has full control over dead time insertion.

Microchip Technology Inc.

Page 11

dsPIC30F Motor Control PWM Module

Complementary Outputs

+V

1H

2H

3H

1L

2L

3L

2005 Microchip Technology Incorporated. All Rights Reserved.

3 Phase

BLDC or

ACIM

dsPIC30F Motor Control PWM Module

12

Each output pin pair can be programmed in the independent mode or in the

complementary mode.

In the independent mode the dead time generators are disabled and there is no

restriction in the state of the pins for any output pin pair.

The complementary mode is very useful in driving loads such as the inverter in

this figure, that could be used for any three phase load, for example: Brushless

DC Motors and Induction Motors. As we have seen, dead time insertion helps

preventing short circuits between the two rails through each couple of

transistors.

Through device configuration bits, the reset-state polarity of the output pins can

be selected.

The HPOL bits in the BOR/POR configuration register determines whether the

high-side output pins must have an active high or low output polarity. The LPOL

bits in the same register set the low-side active high or low polarity.

Moreover, at reset the peripheral output pins can be controlled by PORT

registers, that is, they are normal input-output pins initilized as inputs, or they

can be directly controlled by the Motor Control PWM module as output pins.

Microchip Technology Inc.

Page 12

dsPIC30F Motor Control PWM Module

Independent Outputs

O

O

O

Independent mode is used for switched reluctance

motors

Special inverter circuit to control current in SR motors

Independent mode enables both devices to turn on

+V

PWM1H

PWM2H

PWM1L

PWM3H

PWM2L

2005 Microchip Technology Incorporated. All Rights Reserved.

PWM4H

PWM3L

PWM4L

dsPIC30F Motor Control PWM Module

13

This is an example where all the four PWM outputs are used in independent

mode to drive a Switched Reluctance motor, where each pair of outputs drives

one phase of the stator.

Microchip Technology Inc.

Page 13

dsPIC30F Motor Control PWM Module

Output Override

O

O

O

O

O

Used for motor commutation

Drive PWM or Drive active or inactive

POVD bits decide if I/O pin is controlled manually

POUT bits set state of I/O pin under manual control

Dead time requirements are always satisfied in

complementary mode

OVDCON Register

POVD4H

bit15

POVD4L

14

POVD3H

POVD3L

13

12

POVD2H

11

POVD2L

POVD1H

POVD1L

10

bit8

POUT4H

POUT4L

POUT3H

POUT3L

POUT2H

POUT2L

POUT1H

POUT1L

bit7

bit0

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

14

The manual override control bits allow the user to implement motor

commutation. Through the control bits, a particular output pin may be

programmed to receive the PWM signal from the duty cycle generator, driven

active, or driven inactive. There is a POVD control bit for each PWM output

pin. If this bit is cleared, the pin will output a PWM signal. If the POVD bit is

set, the pin will be controlled manually. There is a POUT bit for each PWM pin

that sets the state of the pin when the output is manually controlled.

Restrictions for complementary outputs cannot be violated through manual

PWM control. When the module is operating in the complementary mode, the

signals on each high-side ouput pin will take priority and the proper dead time

will always be inserted.

Microchip Technology Inc.

Page 14

dsPIC30F Motor Control PWM Module

Output Override

O

Using PWM for 6-step modulation

O Energize BLDC motor coils based on

measured rotor position

O PWM override register used to control active

transistors -- duty cycle sets current

1

PWM1H

+V

1H

2H

3H

3 Phase

BLDC

PWM1L

PWM2H

PWM2L

1L

2L

3L

PWM3H

PWM3L

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

15

This is a typical application of the override capability. In order to be able to

control the rotor speed, the PWM is output on the high side transistors: its duty

cycle will determine the medium voltage applied to the motor and hence its

speed. The required software overhead is really minimum.

Microchip Technology Inc.

Page 15

dsPIC30F Motor Control PWM Module

Fault Pins

O

O

O

O

O

O

Two programmable fault pins: Fault A, Fault B

Fault pins can be assigned to each output pair

Fault pin asynchronously over-rides PWM output

Fault state for each output is programmable

Automatic or latched fault protection

Interrupt vector for each fault input

FLTACON Register

FAOV4H

FAOV4L

bit15

14

FLTAM

bit7

FAOV3H

FAOV3L

13

12

2005 Microchip Technology Incorporated. All Rights Reserved.

FAOV2H

FAOV1H

FAOV1L

10

bit8

FAEN4

FAEN3

FAEN2

FAEN1

bit0

11

FAOV2L

dsPIC30F Motor Control PWM Module

16

The fault pins are safety features: if asserted, they will drive the PWM I/O pins

to a defined state. The action takes place without software intervention, thus

allowing fast and safe response to system failures.

In the smallest devices you can find one fault pin (FLTA), the bigger ones have

them all (FLTA and FLTB). They are active low inputs so that you can easily

wire-OR many different sources.

The FAEN bits allows you to select if any output pin-pair will be controlled by

the fault pins when a fault occurs.

If the functionality is enabled, as soon any fault pin is asserted, the PWM output

pins will go active or inactive according to the content of the upper part of the

FLTACON (or FLTBCON) register.

Each fault pin has its own interrupt vector, flag and interrupt priority register.

There are two different operating modes. In the latched mode as soon as the

fault pin is asserted, the PWM output will get the value defined in the FLTxCON

register. The outputs will remain in this state until the fault pin is deasserted and

the corresponding interrupt flag is cleared.

In the automatic mode, the outputs will keep the fault value as long as the fault

pin is asserted. When released, at the beginning of the following PWM period,

the output will return to normal PWM operation.

Microchip Technology Inc.

Page 16

dsPIC30F Motor Control PWM Module

A/D Synchonization

O

SEVTCMP register sets A/D

conversion start time

SEVTDIR bit sets direction of

PTMR

Ensure A/D properly captures

shunt current

Minimize control loop update

delay

2005 Microchip Technology Incorporated. All Rights Reserved.

To A/D

dsPIC30F Motor Control PWM Module

17

The PWM module has a special trigger that allows the A/D converter to be

synchronized to the PWM time base. This trigger will start the conversion phase

of the A/D block, in order to minimize the delay between getting the A/D

conversion result and updating the duty cycle value.

The Special Event Compare Register is loaded with a number which is

compared to the content of the time base timer, while this one is counting up or

down. The counting direction is set by the Special Event Direction bit. As soon

as there is a match between the two registers, the trigger is generated and the

A/D conversion is started.

This feature is very useful for synchronizing with the phase drive signals the

reading of the shunt currents or the reading of the back emf in a sensorless

BLDC motor control.

Microchip Technology Inc.

Page 17

dsPIC30F Motor Control PWM Module

MC PWM in Power Save Modes

O

In SLEEP mode all PWM output pins are frozen to

the value prior to entering sleep

Fault pins are active

Fault event wakes the device from sleep

In IDLE mode the PWM can optionally continue to

operate

Time base interupt wakes the devise from IDLE

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

18

Finally, let us study the oepration of the peripheral in device power save modes.

In sleep mode the PWM output pins will retain the value that they had when entering sleep. It is

your responsability to put the output pins in a known state before entering power save: this can

be very important for some kind of loads.

During sleep the fault pins, if enabled, will continue to control the outputs, so that if any fault

input is asserted the output PWM pins will be driven to the state programmed into the Fault

Control register. If the fault interrupt enable pin is set, the device will be waken up from sleep

when the fault pin is asserted. If the interrupt priority is higher than the current CPU priority the

ISR will be served, otherwise the code execution will continue from the next instruction following

the PWRSAV instruction.

In IDLE mode the PWM peripheral can be completely functional, according to the value of the

PWM Time Base Stop in IDLE Mode Bit. If reset, the unit will operate normally. The time base

interrupt, if enabled, will wake the unit. Code execution will continue with the ISR if the priority is

higher than the CPU priority or with the next instruction after the PWRSAV instruction.

A last feature is worth mentioning, which is extremely useful during code debugging. The PWM

pins can be optionally tri-stated when the emulator or the debugger is halted. You should install

pull-up or pull-down resistor in order to ensure that the PWM outputs are diven to the correct

state so that external hardware is not damaged.

Microchip Technology Inc.

Page 18

dsPIC30F Motor Control PWM Module

Key Support Documents

Device Selection Reference

Document #

General Purpose and Sensor Family Data Sheet

DS70083

Motor Control and Power Conv. Data Sheet

DS70082

dsPIC30F Family Overview

DS70043

Base Design Reference

Document #

dsPIC30F Family Reference Manual

DS70046

dsPIC30F Programmers Reference Manual

DS70030

MPLAB MPLAB C30 C Compiler User Users Guide

DS51284

MPLAB ASM30, LINK30 & Utilities User

DS51317

dsPIC Language Tools Libraries

DS51456

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

19

For more information, here are references to some important documents that

contain a lot of information about the dsPIC30F family of devices.

The Family Reference Manual contains detailed information about the

architecture and peripherals, whereas the Programmers Reference Manual

contains a thorough description of the instruction set.

Microchip Technology Inc.

Page 19

dsPIC30F Motor Control PWM Module

Key Support Documents

Device Specific Reference

Document #

dsPIC30F2010 Data Sheet

DS70118

dsPIC30F3010/3011 Data Sheet

DS70141

dsPIC30F4011/4012 Data Sheet

DS70135

dsPIC30F6010 Data Sheet

DS70119

Microchip Web Site: www.microchip.com

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

20

For device-specific information such as pinout diagrams, packaging and

electrical characteristics, the device datasheets listed here are the best

source of information.

Microchip Technology Inc.

Page 20

dsPIC30F Motor Control PWM Module

Related Material

O

Apps Notes on Motor Control

AN901 Using the dsPIC30F for Sensorless BLDC Control

AN908 Using the dsPIC30F for Vector Control of an ACIM

AN957 Sensored BLDC Motor Control Using dsPIC30F2010

2005 Microchip Technology Incorporated. All Rights Reserved.

dsPIC30F Motor Control PWM Module

21

We also have some application notes on motor control, in which the peripheral

is extensively used.

All these documents can be obtained from the Microchip web site, by clicking

on the dsPIC Digital Signal Controllers or Technical Documentation link.

This wraps up the seminar on dsPIC30F Motor Control Peripheral. Thank you

for your interest in the dsPIC30F Family of Digital Signal Controllers.

Microchip Technology Inc.

Page 21

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5819)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- When She Unravels A Dark Mafia - Gabrielle SandsDocument416 pagesWhen She Unravels A Dark Mafia - Gabrielle Sandsgraciepizarroyahoo.com.mx87% (30)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Women and Gender in Islam AHMED PDFDocument296 pagesWomen and Gender in Islam AHMED PDFBere Beres100% (1)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Directions:: Nnotated Reference ListDocument3 pagesDirections:: Nnotated Reference ListBlake ChambersNo ratings yet

- 2010-01 Intravenous Therapy Learning Module PDFDocument41 pages2010-01 Intravenous Therapy Learning Module PDFEvan GunawanNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- US Occup of Gy Educ Reform45 49 CIS1991Document254 pagesUS Occup of Gy Educ Reform45 49 CIS1991Rosa Luxemburg100% (1)

- Ars Magica 5thed ErrataDocument3 pagesArs Magica 5thed ErrataDenis Colli MenezesNo ratings yet

- Unit 3Document14 pagesUnit 3ssdeepkaur883No ratings yet

- Name of Employee: Position: Review Period: Bureau/Center/Service/DivisionDocument25 pagesName of Employee: Position: Review Period: Bureau/Center/Service/DivisionPAUL GONZALES90% (10)

- 17-9 eJDD FinalDocument100 pages17-9 eJDD FinalMohamed GamalNo ratings yet

- Real NumbersDocument20 pagesReal NumbersAndi Yudi WigunaNo ratings yet

- Lira Selfish GiantDocument11 pagesLira Selfish GiantyiemanNo ratings yet

- Final Memo RespondentDocument26 pagesFinal Memo RespondentaakankshaNo ratings yet

- BbbbbeeeennnnccchhhDocument18 pagesBbbbbeeeennnnccchhhRohith Venkatesh Rohith VenkateshNo ratings yet

- Formation or Incorporation of A Company - For TheDocument2 pagesFormation or Incorporation of A Company - For TheCAclubindiaNo ratings yet

- The Type-Variety Smith, Willey y GiffordDocument12 pagesThe Type-Variety Smith, Willey y GiffordMiguel Roberto Guevara ChumaceroNo ratings yet

- Briefmac Chap01-2Document13 pagesBriefmac Chap01-2Bekki VanderlendeNo ratings yet

- IELTS Academic Writing Task 1 How To Structure Your AnswerDocument6 pagesIELTS Academic Writing Task 1 How To Structure Your AnswerDung LeNo ratings yet

- Maternal and Child HealthDocument62 pagesMaternal and Child HealthAsfand KhanNo ratings yet

- Miller & Cohen 2001 An Integrative Theory of Prefrontal Cortex FunctionDocument39 pagesMiller & Cohen 2001 An Integrative Theory of Prefrontal Cortex FunctionhoorieNo ratings yet

- Reading 2 Taco Day A2Document3 pagesReading 2 Taco Day A2Víctor Barbosa LosadaNo ratings yet

- DU MPhil PHD in 1historyDocument5 pagesDU MPhil PHD in 1historyDhavanLalNo ratings yet

- Daftar Buku Teologi Sistematika 4Document1 pageDaftar Buku Teologi Sistematika 4Setiadi MichaelNo ratings yet

- IX. Tariff and Customs Code of The Philippines (P.D. No. 1464), As Amended by The Customs Modernization and Tariff Act (Republic Act No. 10863)Document4 pagesIX. Tariff and Customs Code of The Philippines (P.D. No. 1464), As Amended by The Customs Modernization and Tariff Act (Republic Act No. 10863)RnemcdgNo ratings yet

- Analisis Sisa Makanan Dan Biaya Sisa Makanan Lunak Makan Malam Pasien Kelas Iii Di Rsupn Dr. Cipto MangunkusumoDocument17 pagesAnalisis Sisa Makanan Dan Biaya Sisa Makanan Lunak Makan Malam Pasien Kelas Iii Di Rsupn Dr. Cipto MangunkusumoDeanita AmpulembangNo ratings yet

- Om Prasad Nayak: Professional ExperienceDocument2 pagesOm Prasad Nayak: Professional ExperienceOm Prasad NayakNo ratings yet

- Listening Activity (Digital Detox Podcast) PDFDocument6 pagesListening Activity (Digital Detox Podcast) PDFNur SyafiqahNo ratings yet

- Office of The Mission Director: Rashtriya Madhyamik Siksha Abhijan, AssamDocument4 pagesOffice of The Mission Director: Rashtriya Madhyamik Siksha Abhijan, AssamJeshiNo ratings yet

- San Unit-Wise QuestionsDocument6 pagesSan Unit-Wise QuestionsSushmitha KodupakaNo ratings yet

- Sonatest SitescanDocument105 pagesSonatest SitescanAsish desai100% (1)

- Engine, Lubrication: CautionDocument26 pagesEngine, Lubrication: CautionBenNo ratings yet