Professional Documents

Culture Documents

r059210203 Switching Theory Logic Design

Uploaded by

andhracollegesCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

r059210203 Switching Theory Logic Design

Uploaded by

andhracollegesCopyright:

Available Formats

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 1

II B.Tech I Semester Regular Examinations, November 2006

SWITCHING THEORY & LOGIC DESIGN

( Common to Electrical & Electronic Engineering, Electronics &

Instrumentation Engineering, Bio-Medical Engineering, Electronics &

Control Engineering, Electronics & Computer Engineering and

Instrumentation & Control Engineering)

Time: 3 hours Max Marks: 80

www.andhracolleges.com

Answer any FIVE Questions

All Questions carry equal marks

⋆⋆⋆⋆⋆

1. (a) Generate Hamming code for the given 11 bit message 10001110101 and rewrite

the entire message with Hamming code. [8]

(b) The binary numbers listed have a sign bit in the left most position and, if neg-

ative numbers are in 2’s complement form. Perform the arithmetic operations

indicated and verify the answers. [4 × 2 = 8]

i. 101011 + 111000

ii. 001110 + 110010

iii. 111001 - 001010

iv. 101011 - 100110

2. (a) Reduce the following Boolean Expressions [8]

i. AB + A(B + C) + B’(B + D)

ii. A +B + A’B’C

www.andhracolleges.com

iii. A’B + A’BC’ + A’BCD + A’BC’D’E

iv. ABEF + AB(EF)’ + (AB)’EF

(b) Obtain the Dual of the following Boolean expressions. [8]

i. x’yz + x’yz’ + xy’z’ + xy’z

ii. x’yz + xy’z’ + xyz + xyz’

iii. x’z + x’y + xy’z + yz

iv. x’y’z’ + x’yz’ + xy’z’ + xy’z + xyz’

3. (a) Simplify the Boolean expression using K-map F= (ABC D̄) + (A) + (AB D̄) +

(D̄)(ĀB̄ C̄). [8]

(b) Reduce the following function P

using K- map and identify the prime implicant

and non prime implicant .F= m(2, 3, 6, 7, 10, 11, 12). [8]

4. (a) Design a Excess-3 adder using 4-bit parallel binary adder and logic gates.

(b) Draw the logic diagram of a single bit comparator. [12+6]

5. (a) Derive the PLA programming table for the combinational circuit that squares

a 3 bit number.

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 1

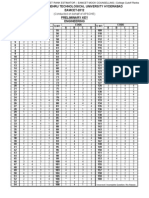

(b) For the given 3-input, 4-output truth table of a combinations circuit,tabulate

the PAL programming table for the circuit. [8+8]

Inputs Output

x y z A B C D

0 0 0 0 1 0 0

0 0 1 1 1 1 1

0 1 0 1 0 1 1

www.andhracolleges.com

0 1 1 0 1 0 1

1 0 0 1 0 1 0

1 0 1 0 0 0 1

1 1 0 1 1 1 0

1 1 1 0 1 1 1

6. (a) Find a modulo-6 gray code using k-Map & design the corresponding counter.

(b) Compare synchronous & Asynchronous. [8+8]

7. A clocked sequential circuit is provided with a single input x and single output Z.

Whenever the input produce a string of pulses 1 1 1 or 0 0 0 and at the end of the

sequence it produce an output Z = 1 and overlapping is also allowed.

(a) Obtain State - Diagram.

(b) Also obtain state - Table.

(c) Find equivalence classes using partition method & design the circuit using D

- flip-flops. [4+4+8]

8. (a) Draw the ASM chart for the following state transistion, start from the initial

www.andhracolleges.com

state T1 , then if xy=00 go to T2 , if xy=01 go to T3 , if xy=10 go to T1 , other

wise go to T3 .

(b) Show the exit paths in an ASM block for all binary combinations of control

variables x, y and z, starting from an initial state. [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 2

II B.Tech I Semester Regular Examinations, November 2006

SWITCHING THEORY & LOGIC DESIGN

( Common to Electrical & Electronic Engineering, Electronics &

Instrumentation Engineering, Bio-Medical Engineering, Electronics &

Control Engineering, Electronics & Computer Engineering and

Instrumentation & Control Engineering)

Time: 3 hours Max Marks: 80

www.andhracolleges.com

Answer any FIVE Questions

All Questions carry equal marks

⋆⋆⋆⋆⋆

1. (a) Perform the following using BCD arithmetic. [2 × 4 = 8]

i. 712910 + 771110

ii. 812410 + 812710

(b) Convert the following. [4 × 2 = 8]

i. AB16 = ( )10

ii. 12348 = ( )10

iii. 101100112 = ( )10

iv. 77210 = ( )16

2. (a) Simplify the following Boolean expressions to minimum no. of literals. [8]

i. x’y’ + xy + x’y

ii. xy’ + y’z’ + x’z’

iii. x’ ? + xy + xz’ + xy’z’

www.andhracolleges.com

iv. (x + y)(x + y’)

(b) Obtain the complement of the following Boolean expressions. [8]

i. AB + A(B + C) + B‘(B + D)

ii. A + B + A‘B’C

iii. A’B + A‘BC’ + A’BCD + A‘BC‘D’E

iv. ABEF + ABE‘F’ + A‘B’EF

3. Apply BranchingQmethod to simplify the following function

F (A, B, C, D) = M (0, 1, 4, 5, 9, 11, 13, 15, 16, 17, 25, 27, 28, 29, 31)d(20, 21, 22, 30).

[16]

4. (a) Design a Excess-3 adder using 4-bit parallel binary adder and logic gates.

(b) Draw the logic diagram of a single bit comparator. [12+6]

5. (a) Find the function f(x1 , x2 , x3 , x4 ) realized by each of the threshold networks

shown in the figure 5(a)i, 5(a)ii, 5b. [8+8]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

3 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 2

i.

www.andhracolleges.com

ii.

Figure 5(a)i

Figure 5(a)ii

(b)

www.andhracolleges.com Figure 5b

6. (a) Give the design of 4 bit Ring counter and explain a with the waveforms. Also

give the application of this ring counter.

(b) Design a modulo-9 counter T flipflops with preset and clear inputs.

7. A clocked sequential circuit is provided with a single input x and single output Z.

Whenever the input produce a string of pulses 1 1 1 or 0 0 0 and at the end of the

sequence it produce an output Z = 1 and overlapping is also allowed.

[8+8]

(a) Obtain State - Diagram.

(b) Also obtain state - Table.

(c) Find equivalence classes using partition method & design the circuit using D

- flip-flops. [4+4+8]

8. For the ASM chart given 8:

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

3 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 2

www.andhracolleges.com

Figure 8

(a) Draw the state diagram.

www.andhracolleges.com

(b) Design the control unit using D flip-flops and a decoder. [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

3 ofUSA-UK-Australia-Germany-France-NewZealand

3 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 3

II B.Tech I Semester Regular Examinations, November 2006

SWITCHING THEORY & LOGIC DESIGN

( Common to Electrical & Electronic Engineering, Electronics &

Instrumentation Engineering, Bio-Medical Engineering, Electronics &

Control Engineering, Electronics & Computer Engineering and

Instrumentation & Control Engineering)

Time: 3 hours Max Marks: 80

www.andhracolleges.com

Answer any FIVE Questions

All Questions carry equal marks

⋆⋆⋆⋆⋆

1. Convert the following to Decimal and then to Octal.

(a) 423416

(b) 125F16

(c) 100100112

(d) 101111112

(e) 39210

(f) 77910 [3+3+3+3+2+2]

2. (a) Simplify the following expressions and implement them with NAND gate cir-

cuits. [8]

i. AB’ + ABD + ABD’ + A’C’D’ + A’BC’

ii. BD + BCD’ + AB’C’D’

www.andhracolleges.com

(b) Obtain the Dual of the following Boolean expressions.

i. AB + A(B + C) + B’(B + D)

ii. A + B + A’B’C [4]

(c) Obtain the complement of the following Boolean expressions.

i. A’B + A’BC’ + A’BCD + A’BC’D’E

ii. ABEF + ABE’F’ + A’B’EF [4]

3. Minimise

P on the map the five variable function.

F= m(0, 1, 4, 5, 6, 13, 14, 15, 22, 24, 25, 28, 29, 30, 31). [16]

4. (a) Design a 32:1 Multiplexer using two 16:1 and 2:1Multiplexers.

(b) Design a circuit to convert Excess-3 code to BCD code Using a 4-bit Full

adder. [8+8]

5. (a) Given a 32 x 8 Rom clip with an enable input, show the external connection

necessary to construct a 128 x 8 Rom with four chips and a decoder.

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 3

(b) Tabulate the PLA programming table for the four Boolean functions listed

below

A(x,y,z) = ε(1, 2, 4, 6)

B(x,y,z) = ε(0, 1, 6, 7)

C(x,y,z) = ε(2,6)

D(x,y,z) = ε(1, 2, 3, 5, 7). [8+8]

6. (a) Compare synchronous & Asynchronous circuits

www.andhracolleges.com

(b) Design a Mod-6 synchronous counter using J-K flip flops. [6+10]

7. A clocked sequential circuit is provided with a single input x and single output Z.

Whenever the input produce a string of pulses 1 1 1 or 0 0 0 and at the end of the

sequence it produce an output Z = 1 and overlapping is also allowed.

(a) Obtain State - Diagram.

(b) Also obtain state - Table.

(c) Find equivalence classes using partition method & design the circuit using D

- flip-flops. [4+4+8]

8. (a) Draw the ASM chart for the following state transistion, start from the initial

state T1 , then if xy=00 go to T2 , if xy=01 go to T3 , if xy=10 go to T1 , other

wise go to T3 .

(b) Show the exit paths in an ASM block for all binary combinations of control

variables x, y and z, starting from an initial state. [8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 4

II B.Tech I Semester Regular Examinations, November 2006

SWITCHING THEORY & LOGIC DESIGN

( Common to Electrical & Electronic Engineering, Electronics &

Instrumentation Engineering, Bio-Medical Engineering, Electronics &

Control Engineering, Electronics & Computer Engineering and

Instrumentation & Control Engineering)

Time: 3 hours Max Marks: 80

www.andhracolleges.com

Answer any FIVE Questions

All Questions carry equal marks

⋆⋆⋆⋆⋆

1. (a) Generate Hamming code for the given 11 bit message 10010110101 and rewrite

the entire message with Hamming code. [8]

(b) The binary numbers listed have a sign bit in the left most position and,if neg-

ative numbers are in 2’s complement form. Perform the arithmetic operations

indicated and verify the answers. [4×2=8]

i. 101011 + 111001

ii. 001111 + 110010

iii. 111001 - 011010

iv. 101111 - 100110

2. (a) Draw the logic diagram using only two input NAND gates to implement the

following expression. [8]

(AB + A’B’)(CD’ ? + C’D)

(b) Obtain the complement of the following Boolean expressions.

www.andhracolleges.com

i. B’C’D + (B + C + D)’ + B’C’D’E

ii. AB + (AC)’ + (AB + C) [4]

(c) Obtain the dual of the following Boolean expressions.

i. A’B’C’ + A’BC’ + AB’C’ + ABC’

ii. AB + (AC)’ + AB’C [4]

3. (a) Differentiate prime implicant and non prime implicant, essential prime impli-

cant and non essential prime implicant. [8]

(b) Reduce the following function using

P K- map and identify prime implicants and

essential prime implicants F= m(0, 1, 2, 3, 6, 7, 13, 15) [8]

4. (a) Design a 32:1 Multiplexer using two 16:1 and 2:1Multiplexers.

(b) Design a circuit to convert Excess-3 code to BCD code Using a 4-bit Full

adder. [8+8]

5. Write a brief note on:

(a) Architecture of PLDS

(b) Capabilities and the limitations of thusold gates. [8+8]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210203 Set No. 4

6. (a) Compare synchronous & Asynchronous circuits

(b) Design a Mod-6 synchronous counter using J-K flip flops. [6+10]

7. A clocked sequential circuit with simple input x and single output Z produce an

output Z = 1 whenever the input x completes the sequence 1 0 1 1 and overlapping

is allowed.

www.andhracolleges.com

(a) Obtain its state - diagram.

(b) Obtain its minimal state - table and design the circuit with D - Flip-Flops.

[8+8]

8. (a) For the given state-diagram of a control circuit 8 obtain ASM chart.

(b) Design the circuit using multiplexers. [8+8]

www.andhracolleges.com ⋆⋆⋆⋆⋆

Figure 8

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

You might also like

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDocument3 pagesEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Polycet 2014 Question PaperDocument24 pagesPolycet 2014 Question PaperandhracollegesNo ratings yet

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDocument1 pageEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggNo ratings yet

- Eamcet 2014 Engineering Key Solutions AndhracollegesDocument42 pagesEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDocument62 pagesEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Eamcet 2010 Medical PaperDocument63 pagesEamcet 2010 Medical PaperandhracollegesNo ratings yet

- Eamcet 2012 Engineering Paper KeyDocument1 pageEamcet 2012 Engineering Paper KeyandhracollegesNo ratings yet

- Eamcet 2014 Engineering Key SolutionsDocument42 pagesEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDocument62 pagesAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Eamcet 2007 Engineering PaperDocument13 pagesEamcet 2007 Engineering Paperandhracolleges100% (1)

- Icet-2014-Important Instructions BookletDocument3 pagesIcet-2014-Important Instructions BookletandhracollegesNo ratings yet

- Eamcet 2001 Engineering PaperDocument14 pagesEamcet 2001 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2006 Engineering PaperDocument14 pagesEamcet 2006 Engineering PaperandhracollegesNo ratings yet

- Eamcet 2004 Engineering PaperDocument12 pagesEamcet 2004 Engineering PaperandhracollegesNo ratings yet

- EAMCET Engineering Entrance Solved Paper 2000Document13 pagesEAMCET Engineering Entrance Solved Paper 2000Giri NathNo ratings yet

- Eamcet 2002 Engineering PaperDocument14 pagesEamcet 2002 Engineering Paperandhracolleges0% (1)

- Eamcet 2003 Engineering PaperDocument12 pagesEamcet 2003 Engineering Paperandhracolleges100% (1)

- Eamcet 2009 Engineering Physics PaperDocument19 pagesEamcet 2009 Engineering Physics PaperandhracollegesNo ratings yet

- EAMCET NotificationDocument3 pagesEAMCET NotificationKeerthiPratheek ReddyNo ratings yet

- TS ICET Syllabus and Exam PatternDocument5 pagesTS ICET Syllabus and Exam PatterngayathriNo ratings yet

- Eamcet Pharmacy College Fee DetailsDocument14 pagesEamcet Pharmacy College Fee DetailsandhracollegesNo ratings yet

- FeeDocument34 pagesFeeThanniru VenkateshNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)