Professional Documents

Culture Documents

Appendix A PDF

Appendix A PDF

Uploaded by

Axe Axe0 ratings0% found this document useful (0 votes)

14 views5 pagesOriginal Title

Appendix-A.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

14 views5 pagesAppendix A PDF

Appendix A PDF

Uploaded by

Axe AxeCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 5

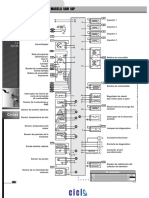

Appendix A

SIC/XE Instruction

Set and Addressing

Modes

Instruction Set

In the following descriptions, uppercase letters refer to specific registers. The

notation m indicates a memory address, n indicates an integer between 1 and

16, and rl and r2 represent register identifiers. Parentheses are used to denote

the contents of a register or memory location, Thus A ¢ (m..2m+2) specifies that

the contents of the memory locations mt through m+2 are loaded into register

A; m..m+2 < (A) specifies that the contents of register A are stored in the word

that begins at address m.

The letters in the Notes column have the following meanings:

P Privileged instruction

X Instruction available only on XB version

F Floating-point instruction

« C Condition code CC set to indicate result of operation (<, =, ot >)

‘The Format column indicates which SIC/XE instruction format is to be iised in

assembling each instruction; 3/4 means that either Format 3 or Format 4 can

‘be used. All instructions for the standard version of SIC are assembled using

the format described in Section 1.3.1 (which is compatible with Format 3).

Instruction subfields that are not required, such as the address field for an.

RSUB instruction, are set to zero.

495

Appendix A” SIC Instruction Set and Addressing Modes

Mnemonic

ADD m

ADDF m

ADDR 11,2

AND m

CLEAR ri

COMP m

COMPF m

COMER 11,12

DIV m

DIVE m

DIVR rix2

FIX

FLOAT

HIO

Im

JEQ m

JGT m

JET m

JSUB m

LDA m

LDB m

LDCH m

LDF m

LDL m

LDS m

LDT m

LDX m

LPS m

MUL m

Format

3/4

3/4

2

3/4

2

3/4

3/4

2

3/4

Opeode

BENS ARSSSSSSESRLSRFSSRRERERREESAB

Effect

At (A) + (mand) |

Fe (f+ (mms) XE

2 (2)+ (71) x

A& (A) & (m.m42)

rleO x |

(A): @m.m+2) c |

): (nms5) XFC i

(1): 2) xc

Ac (A) / (m.ms2)

Fe @)/ (mms) XF

12+ (2) / (1) x

Ae @®) [convert tointeger] XF

Fe(A) [converttofioating} XF

Halt1/O channel number (A) PX

PCem

PC emi CC set to=

PCe mif CC set to>

PC emif CCéetto<

Le PO; PCem

Ae (mami2)

Be (m.m+2) x

A rightmost byte] <— (m)

Fe (mms) XF

Le (mmi2)

Se (m.mi2) x

T<(m.mi2) x

X<(m.ms2)

Load processor status from PX

information beginning at

address m (see Section 6.2.1)

Ae (A)* (n.me2)

Instruction Set

Ninemonic Format Opcode _Effect Notes

MULF m 3/4 0 Fe @)* (m.ms5) XE

MULR r1x2 2 98 12. (12) * (r1) x

NORM 1 8 F< (F) [normalized] a

OR m 3/4 “ Ae (A) | (mm42)

RDm 3/4 D8 Alrightmost byte] «data P

from device specified by (m)

RMO 1x22 AC Rec)

RSUB 3/4 ac Pce (Ll)

SHIFTL rn. 2 AS t1¢ (rl); left circular shift X

nbits. {In assembled

instruction, 12=n-1}

SHIFIR rin 2 AS 11 (¢l);right shiftnbits, =X

with vacated bit positions set

equal to leftmost bit of (r1).

{in assembled instruction,

r2=n-l}

so 1 FO Start I/O channel number (A); PX

address of channel program

is given by (6)

SSK m 3/4 BC Protection key for addressm PX

+ (A) (see Section 6.2.4)

STA m 3/4 oc m.mi2<-(A)

STB m 3/4 6 m.m+2.< (B) x

STCH m 3/4 54 m€ (A) [rightmost byte]

STF m 3/4 80 mumt5 € (F) F XF

STI m 3/4 Dt Interval timer value PX

(m..m#2) (see Section 6.2.1)

STL m 3/4 4 mumt2 (1)

STS m 3/4 7 m.mi2& (8) x

STSW m 3/4 ES m.mt2 — (SW) P

SIT m 3/4 84 muni2¢ (1) x

SIX m 3/4 10 mame

SUB m 3/4 1c Ae (A)=(m.m+2)

SUBF m 3/4 5c Fe ()—(m.mt5) XF

Appendix A SIC Instruction Set and Addressing Modes

Mnemonic Format Opcode _Effect Notes

SUBR riz2 2 94 2e(2)-(e) x

SVC n 2 BO Generate SVCinterrupt. fn X

assembled instruction, rl =n}

Mm 3/4 EO ‘Test device specified by(m) P ci

TIO 1 FS ‘Test I/O channel number (A) PX C

™m 3/4 2c X ©0041; 00: (m.n42) c

TDR rl 2 BB Xe) +1; 0: @1) xc

WD m 3/4 pe Device specified by (an) (A) P

[rightmost byte]

Instruction Formats

Format 1 (1 byte):

.

Format 2 (2 bytes):

8 4 4 *

[acinomae |

Format 3 (8 bytes):

6 4444 20

Addressing Modes

The following addressing modes apply to Format 3.and 4 instructions.

Combinations of addressing bits not included in this table are treated as errors

by the machine. In the description of assembler language notation, ¢ indicates

a constant between 0 and 4095 (or a memory address known to be in this

range); m indicates a memory address or a constant value larger than 4095.

Further information can be found in Section 1.3.2.

Addressing Modes 499 |

The letters in the Notes column have the following meanings:

4 Format4 instruction

D __Ditect-addressing instruction

‘A Assembler selects either program-counter relative or base-relative

mode

S Compatible with instruction format for standard SIC machine.

Operand value can be between 0 and 32,767 (see Section 1.3.2 for

details).

Assembler Calculation

Addressing Flagbits language _of target

type nixbpe notation address TA Operand Notes

Simple 110000 ope _— disp (tay D \

110001 +opm addr (TA) 4D

110010 opm. PC) +disp may A

110100 opm —(B) + disp (tA) A

111000 © opcX — disp +00 (TA) D

111001 +op mX addr +(X) (TA) 4D

111010 = opmxX_ (PC) +disp +(X) (TA) A

111100 opmX (B)+disp+(%)_ (TA) A

000--- - opm _b/p/e/disp (TA) Ds

001--- op mX b/p/e/disp + (X) (TA) Ds

Indirect 100000 op @c — disp (mA) oD

100001 +op @m addr (ma) 4D

100010 op@m (PC) +disp «qma)) A |

100100 op @m (8) +disp (ma) A |

Immediate 010000 op fe disp TA D \

010001 +op#m addr TA 4D i

010010 op#m (PC) +disp TA A

010100 op #m B) +disp TA A

eee

You might also like

- 101 Problems in AlgebraDocument160 pages101 Problems in AlgebraTrishaii Cuaresma96% (28)

- Flow Design Formulas For Calculation - Exported From (HTM - 02 - 01 - Part - A)Document8 pagesFlow Design Formulas For Calculation - Exported From (HTM - 02 - 01 - Part - A)wesam allabadi50% (2)

- Business Startup Guides-Preparing Yourself Ver 2Document4 pagesBusiness Startup Guides-Preparing Yourself Ver 2Minh Huỳnh100% (1)

- ElvisDocument1 pageElvismaui3No ratings yet

- Calculus Cheat Sheet DerivativesDocument4 pagesCalculus Cheat Sheet DerivativesRajatNo ratings yet

- All The Things You AreDocument1 pageAll The Things You ArePeppe LiottaNo ratings yet

- Aural RitmoDocument1 pageAural RitmofabioNo ratings yet

- 388 1006 1 PBDocument20 pages388 1006 1 PBGabriel Evangelista dos SantosNo ratings yet

- Excercise in FDocument2 pagesExcercise in FPaz Villahoz100% (2)

- GM Relés y Fusibles Corsa PDFDocument1 pageGM Relés y Fusibles Corsa PDFcorylinNo ratings yet

- Taita Salasaca - Conga Drums 2Document2 pagesTaita Salasaca - Conga Drums 2Carlos XavierNo ratings yet

- Music To Watch Girls by MJDocument3 pagesMusic To Watch Girls by MJMarvin JongNo ratings yet

- Mix Serpiente - BandaDocument53 pagesMix Serpiente - BandaJohn Carlos Vilca VelizNo ratings yet

- All Art Is Propaganda PDFDocument2,708 pagesAll Art Is Propaganda PDFPau_Brand_255033% (3)

- Como Quien Pierde Una Estrella VozDocument2 pagesComo Quien Pierde Una Estrella VozGerardo100% (2)

- Renault Inyección Electrónica Kangoo RL-RN 1.6 1999 Siemens Sirius 32b PDFDocument2 pagesRenault Inyección Electrónica Kangoo RL-RN 1.6 1999 Siemens Sirius 32b PDFOsvaldo LópezNo ratings yet

- Unit 4 Uncertain Knowledge CompleteDocument14 pagesUnit 4 Uncertain Knowledge Completesssttt1993No ratings yet

- Renault Inyección Electrónica Clio 1.4 Ac Delco Monopoint P PDFDocument2 pagesRenault Inyección Electrónica Clio 1.4 Ac Delco Monopoint P PDFGood CarNo ratings yet

- 5Document2 pages5Abel Salazar PianoNo ratings yet

- 01 - Lista de Parametros SimplificadaDocument8 pages01 - Lista de Parametros SimplificadaLuis Felipe VidigalNo ratings yet

- Enfermeiro Ebsrh 2015Document10 pagesEnfermeiro Ebsrh 2015Neila Reis da SilvaNo ratings yet

- Mix Trompeta ChilombianoDocument1 pageMix Trompeta ChilombianoDenise AlvaradoNo ratings yet

- Extracto Destinos-Elementos-para-la-gestión-de-destinos-turisticosDocument76 pagesExtracto Destinos-Elementos-para-la-gestión-de-destinos-turisticosEnzo Navarrete UlloaNo ratings yet

- Tema 6. CULTURADocument7 pagesTema 6. CULTURAMarinaNo ratings yet

- Detail (1-1) To R.C. Strip Footing (Sf1) : A B E F H J KDocument1 pageDetail (1-1) To R.C. Strip Footing (Sf1) : A B E F H J KThomas Garcia0% (1)

- Hecho Del PíncipeDocument11 pagesHecho Del PíncipeEdisson MoralesNo ratings yet

- Charles D Ghilani - Paul R Wolf - Elementary Surveying - An Introduction To Geomatics-Pearson Prentice Hall (2012) - ExtractoDocument19 pagesCharles D Ghilani - Paul R Wolf - Elementary Surveying - An Introduction To Geomatics-Pearson Prentice Hall (2012) - ExtractoRodrigo DelBarrioNo ratings yet

- PDF Parts Catalog Tvs Rockz - CompressDocument104 pagesPDF Parts Catalog Tvs Rockz - CompressaspareteNo ratings yet

- Xsara 18 - Berlingo 18 - 18 Xu7jb PDFDocument2 pagesXsara 18 - Berlingo 18 - 18 Xu7jb PDFJorge Daniel DiazNo ratings yet

- UTS ELT MDE S1 Coursebook Evaluation ChecklistDocument3 pagesUTS ELT MDE S1 Coursebook Evaluation ChecklistHanin Khalishah WaqqasNo ratings yet

- 09 - Chapter 1Document20 pages09 - Chapter 1Dr. POONAM KAUSHALNo ratings yet

- GM Inyección Electrónica S10 Blazer 2.2 Efi Delphi Multec emDocument2 pagesGM Inyección Electrónica S10 Blazer 2.2 Efi Delphi Multec emyayixdfuego131No ratings yet

- 2020Document14 pages2020mintrikpalougoudjoNo ratings yet

- Strong Enough - DrumsDocument2 pagesStrong Enough - DrumsКолянсур ИвановNo ratings yet

- Fiat CoupeDocument1 pageFiat CoupeJulio FaninNo ratings yet

- Elec 4 BlackDocument1 pageElec 4 Blackyudo08No ratings yet

- Escort 18 16 ZetecDocument2 pagesEscort 18 16 ZetecOsvaldo LópezNo ratings yet

- Greenwashing Nas EmpresasDocument37 pagesGreenwashing Nas EmpresasLara GagoNo ratings yet

- Paradise Violín IIDocument2 pagesParadise Violín IIJavier Rubio PérezNo ratings yet

- What A Wonderful World Eb - Bass Trombone PDFDocument1 pageWhat A Wonderful World Eb - Bass Trombone PDFJose HerreroNo ratings yet

- Indian Express 19 AugustDocument20 pagesIndian Express 19 AugustTension Dene kaNo ratings yet

- Tu Me Gustas Trompeta 1Document2 pagesTu Me Gustas Trompeta 1JonathanNo ratings yet

- Planes APIDocument10 pagesPlanes APIManuel FigueroaNo ratings yet

- Building ActDocument136 pagesBuilding ActVeronika RaušováNo ratings yet

- El Pastor - VihuelaDocument1 pageEl Pastor - VihuelaDamian Guardia SalazarNo ratings yet

- 6periostitisDocument10 pages6periostitisAntonioNo ratings yet

- Ibfc 142 Engenheiro MecanicoDocument16 pagesIbfc 142 Engenheiro MecanicoJosé Maria junior100% (2)

- Cicuta Tibia - TubaDocument2 pagesCicuta Tibia - TubaYohan Octavio Vera DelgadoNo ratings yet

- 5756867Document1,027 pages5756867Sách Việt Nam50% (2)

- Trompeta 1Document2 pagesTrompeta 1Mauricio TorresNo ratings yet

- Ampacidad AlimentacionDocument1 pageAmpacidad Alimentacionluis miguel sanchez estrellaNo ratings yet

- Los Mareados Arreglo Hernan PossettiDocument2 pagesLos Mareados Arreglo Hernan PossettiteomondejarmusicaNo ratings yet

- Lagenda Violin PDFDocument2 pagesLagenda Violin PDFMarvin Jong0% (1)

- Trompeta 2Document2 pagesTrompeta 2Mauricio TorresNo ratings yet

- Passport SystemDocument42 pagesPassport Systemsssttt19930% (1)

- 1.vliw & EpicDocument5 pages1.vliw & Epicsssttt1993No ratings yet

- Jalab RecordDocument50 pagesJalab Recordsssttt1993No ratings yet

- Cs2301 Software Engineering QuestionbankDocument43 pagesCs2301 Software Engineering Questionbanksssttt1993100% (1)

- Principles of Object Technology: Module 5: Interaction DiagramsDocument22 pagesPrinciples of Object Technology: Module 5: Interaction Diagramssssttt1993No ratings yet