Professional Documents

Culture Documents

21-FSM Examples PDF

21-FSM Examples PDF

Uploaded by

Veeranjaneyulu DhikondaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

21-FSM Examples PDF

21-FSM Examples PDF

Uploaded by

Veeranjaneyulu DhikondaCopyright:

Available Formats

)

!

" # $%#

!

!

!

&

* #

'

!

" # $% (

" # $%

*

)

+ *

)

)

#

#

*0

"

,

4

2,

*

%

%

%

1,

" #$ (

3

*

current

next

reset state

input state

#

#

A/0

reset

0

1

D/1

1

0

0

0

0

0

0

0

0

B/0

C/0

A

A

B

B

C

C

D

D

0

1

0

1

0

1

0

1

current

output

A

A

B

A

C

A

D

A

D

0

0

0

0

0

0

0

1

1

.

*

'! -

reset

D/1

1

1,

78

current

next

reset state

input state

B/0

1

0

1

C/0

"

0

A/0

5 ,

1

0

0

0

0

0

0

0

0

00

00

01

01

10

10

11

11

0

1

0

1

0

1

0

1

00

00

01

00

10

00

11

00

11

current

output

0

0

0

0

0

0

0

1

1

9'8

78

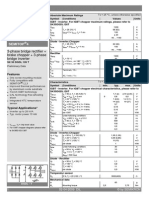

MSB+ = LIn + MIn

LSB+ = L'In + MIn

Out+ = ML

Notation

M := MSB

L := LSB

In := Input

2

2, #

* " # $%

;

MSB+ = LIn + MIn

AND2

PRN

MSB

CLRN

OR2

Out+ = ML

DFF

PRN

AND2

51

<

LSB

44

In

Out

53

AND2

In

MSB 52

AND2

Reset

45

!#

47

48

41

LSB

&

#

DFF

OR2

AND2

NOT

*2

*

In

MSB 43

In

LSB

CLRN

LSB+ = L'In + MIn

Clock

42

Reset

&

:

*

#

-, ! -

present

state

0

Reset

&

&

&

inputs

D N

0 0

0 1

1 0

1 1

0 0

0 1

1 0

1 1

0 0

0 1

1 0

1 1

S0

&

%

# $< 3

# $#

S7

[open]

S2

S1

S5

S4

S3

N

[open]

[open]

S6

10

[open]

D

S8

[open]

15

next

state

0

5

10

5

10

15

10

15

15

15

present

output

0

0

0

0

0

0

0

0

0

#

<

( !

1

1-

#

>

&

<

3

>

< 83

2>

?# @

"

&

<

2>

#

*

3

present state inputs

Q0 Q1

D N

0 0

0 0

0 1

1 0

1 1

0 1

0 0

0 1

1 0

1 1

1 0

0 0

0 1

1 0

1 1

1 1

next state present

P1 P0

output

0 0

0

0 1

0

1 0

0

0 1

0

1 0

0

1 1

0

1 0

0

1 1

0

1 1

0

1 1

1

1,

K-map for P1

K-map for P0

Q1Q0

Q1

DN 00 01 11 10

00 0 0 1 1

01 0 1

1 1

11 X X

X X

10 1 1

1 1

2, #

K-map for Open

Q1Q0

Q1

DN 00 01 11 10

00 0 1 1 0

N

D

01 1 0

1 1

11 X X

X X

10 0 1

1 1

Q0

Q1Q0

Q1

DN 00 01 11 10

00 0 0 1 0

N

D

01 0 0

1 0

11 X X

X X

10 0 0

1 0

Q0

P1 = Q1 + D + Q0N

Q0

if FFs do not have a reset pin then

A BC 83 8C <

P0 = Q0'N + Q0N' + Q1N + Q1D

P1 = reset'(Q1 + D + Q0N)

OPEN = Q1Q0

P0 = reset'(Q0'N + Q0N' + Q1N + Q1D)

A BC D

< 8 C <D8 C < 8 C 3

A < BC C

1

*

A <

! -!%<3 *

!-!

#

* /

%<3 * 0

Reset

Reset

A < BC C B/

C 838C <0

/

C D

<8C <D

8C <8C 30

*

*

D

0

[0]

N

N'D'

5

[0]

N

N'D'

10

[0]

N+D

N'D'

N'D'/0

N/0

5

D/0

N'D'/0

N/0

10

D/1

N'D'/0

N+D/1

15

[1]

/1

15

3

(

* *

" #$

)#

#

#

!

;

&

*-!

!

,!

!

)

-

#

#

/

)) #

/!

B

08 *

G*

*

*0

F

.

?@

.

?@

/,

*,% 9

G

?@

?@

?@

*)

" #

*)

40

always @(in or state)

`define zero 0

`define one1 1

`define two1s 2

case (state)

`zero:

// last input was a zero

begin

if (in) next_state = `one1;

else

next_state = `zero;

end

`one1:

// we've seen one 1

begin

if (in) next_state = `two1s;

else

next_state = `zero;

end

`two1s:

// we've seen at least 2 ones

begin

if (in) next_state = `two1s;

else

next_state = `zero;

end

endcase

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg [2:1] state;

// state variables

reg [2:1] next_state;

always @(posedge clk)

if (reset) state = `zero;

else

state = next_state;

.

?@

?@

?@

*

#

always @(state)

case (state)

`zero: out = 0;

`one1: out = 0;

`two1s: out = 1;

endcase

endmodule

!+

*)

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg state;

// state variables

reg next_state;

always @(posedge clk)

if (reset) state = `zero;

else

state = next_state;

always @(in or state)

case (state)

`zero:

// last input was a zero

begin

out = 0;

if (in) next_state = `one;

else

next_state = `zero;

end

`one:

// we've seen one 1

if (in) begin

next_state = `one; out = 1;

end else begin

next_state = `zero; out = 0;

end

endcase

endmodule

module reduce (clk, reset, in, out);

input clk, reset, in;

output out;

reg out;

reg state; // state variables

always @(posedge clk)

if (reset) state = `zero;

else

case (state)

`zero:

// last input was a zero

begin

out = 0;

if (in) state = `one;

else

state = `zero;

end

`one:

// we've seen one 1

if (in) begin

state = `one; out = 1;

end else begin

state = `zero; out = 0;

end

endcase

endmodule

#

!

You might also like

- Home at Last - New Originals ArrangementDocument2 pagesHome at Last - New Originals Arrangementedskeyboard100% (1)

- Modern Digital Electronics - R. P. JainDocument92 pagesModern Digital Electronics - R. P. JainJames Thee33% (3)

- LBO ModelDocument13 pagesLBO ModelSonali Dash100% (1)

- Serial KeysDocument9 pagesSerial KeysRiicardo RosaNo ratings yet

- Bates V Post Office: Paula Vennells Email ChainDocument5 pagesBates V Post Office: Paula Vennells Email ChainNick WallisNo ratings yet

- Samuel Sagan Awakening The Third Eye PDFDocument279 pagesSamuel Sagan Awakening The Third Eye PDFSónia RibeiroNo ratings yet

- English Prepositions TableDocument4 pagesEnglish Prepositions TableAndreea PaulaNo ratings yet

- Workflow Performance Tuning 2013Document22 pagesWorkflow Performance Tuning 2013Bogdan StatescuNo ratings yet

- Act 1 Scene 7Document7 pagesAct 1 Scene 7alannachetsNo ratings yet

- Mindset SB L2Document12 pagesMindset SB L2VY BÙI NHẬT100% (1)

- Doreyeh 4 Erfaneh Halgheh Keyhani Faradarmani Psymentology Dr. Mohammad Ali TaheriDocument22 pagesDoreyeh 4 Erfaneh Halgheh Keyhani Faradarmani Psymentology Dr. Mohammad Ali TaheriMohammad Ali Taheri100% (1)

- Invensys Foxboro IA Series Software ManualDocument18 pagesInvensys Foxboro IA Series Software ManualTeddy PahlewiNo ratings yet

- CharFlo-Memory Compiler Tech Rev10.3-2010JuneDocument33 pagesCharFlo-Memory Compiler Tech Rev10.3-2010Junevikramkolanu100% (1)

- Lightning Platform Fundamentals - Creating On-Demand AppsDocument404 pagesLightning Platform Fundamentals - Creating On-Demand Appspuuzi75% (4)

- Geanta Manoliu - Manual de VioaraDocument22 pagesGeanta Manoliu - Manual de VioaraMatei B78% (37)

- Welcome AddreesDocument6 pagesWelcome AddreesBenj BinoyaNo ratings yet

- Social Theory of DiscourseDocument20 pagesSocial Theory of DiscourseNNMNo ratings yet

- Honda Prezintă Noua CMX 1100 Rebel DCT - Motobikes 2Document1 pageHonda Prezintă Noua CMX 1100 Rebel DCT - Motobikes 2Suciu BiancaNo ratings yet

- Raport KTSPDocument4 pagesRaport KTSPdjumiranNo ratings yet

- C ProgramsDocument9 pagesC ProgramsGopi ChanduNo ratings yet

- RS 70 - Conexel - Relé de InterposiçãoDocument1 pageRS 70 - Conexel - Relé de InterposiçãoKim Nicolas SaikiNo ratings yet

- Arabic Ccna VoiceDocument42 pagesArabic Ccna VoiceMorad AlabsyNo ratings yet

- Surat Ijin Meninggalkan DinasDocument2 pagesSurat Ijin Meninggalkan DinasJoko LelonoNo ratings yet

- NL9 7 TakahashiDocument20 pagesNL9 7 TakahashiAnand KrishnaNo ratings yet

- B0a, 740D 'E) ?$%e, 30F?#) - ) G0 (#-,: !C! !C! !C! !C!Document2 pagesB0a, 740D 'E) ?$%e, 30F?#) - ) G0 (#-,: !C! !C! !C! !C!Natasha MyersNo ratings yet

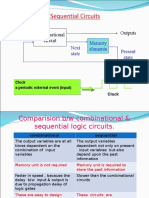

- Block Diagram of A Sequential Logic Circuit: Combinational Circuit Memory Elements Inputs OutputsDocument51 pagesBlock Diagram of A Sequential Logic Circuit: Combinational Circuit Memory Elements Inputs OutputsJagan RajendiranNo ratings yet

- Venus 2Document33 pagesVenus 2mahsam58No ratings yet

- All 200 Series CPU's Wiring DrawingDocument15 pagesAll 200 Series CPU's Wiring DrawingpandubhargaviNo ratings yet

- Concentrado FinancieroDocument10 pagesConcentrado FinancieroDrNetasNo ratings yet

- Exp No: Usage of Cursor Date:: Branch Name, House No (PK), AmountDocument6 pagesExp No: Usage of Cursor Date:: Branch Name, House No (PK), AmountaaanathanNo ratings yet

- Credit Risk ManagementDocument6 pagesCredit Risk ManagementAshadur Rahman JahedNo ratings yet

- BI I I I A A A A: Beyond Innovation Technology Co., LTDDocument10 pagesBI I I I A A A A: Beyond Innovation Technology Co., LTDVirginiaJ92No ratings yet

- 2005-04-11 Mobile Content. Let Everyone Be Happy - Vittorio Maffei - La Netro ZEDDocument11 pages2005-04-11 Mobile Content. Let Everyone Be Happy - Vittorio Maffei - La Netro ZEDMobile Monday ItalyNo ratings yet

- FeaturesDocument75 pagesFeaturesindustronicaNo ratings yet

- Phatty CCsDocument4 pagesPhatty CCssvitilla0% (1)

- Chronicles v3Document407 pagesChronicles v3Transação autorizadaNo ratings yet

- Meridiano de Greenwich - Toda MatériaDocument1 pageMeridiano de Greenwich - Toda MatériaIzabella SantosNo ratings yet

- Drug Price Control Order 2013Document73 pagesDrug Price Control Order 2013Latest Laws TeamNo ratings yet

- Flexi EDGE BTS Troubleshooting: C C C C !""#Document104 pagesFlexi EDGE BTS Troubleshooting: C C C C !""#Alexander TyshchenkoNo ratings yet

- R5Sr&Ttug Gu% Vur Uw: Cap. 5,51,21 DRF 19,35,04 WMS 3,43,77Document2 pagesR5Sr&Ttug Gu% Vur Uw: Cap. 5,51,21 DRF 19,35,04 WMS 3,43,77Ashish Kumar PandeyNo ratings yet

- Chuong 2 Tin Hoc Can BanDocument36 pagesChuong 2 Tin Hoc Can BanTrang LeNo ratings yet

- Ofertório em Procissão Vão o Pão e o Vinho - PáscoaDocument2 pagesOfertório em Procissão Vão o Pão e o Vinho - PáscoaDamilson SantosNo ratings yet

- Digital and Logic Devices No 5 DLD Basic DevicesBasic Flip-Flop Sequential CircuitDocument51 pagesDigital and Logic Devices No 5 DLD Basic DevicesBasic Flip-Flop Sequential CircuitSanthi SriNo ratings yet

- By James Demeo and The Orgone Biophysical Research Laboratory, IncDocument24 pagesBy James Demeo and The Orgone Biophysical Research Laboratory, IncchrifotiNo ratings yet

- Order Form SilverDocument4 pagesOrder Form SilverekaaprilNo ratings yet

- Executive Summary - 25580828Document2 pagesExecutive Summary - 25580828Ken Worawuth SathianhiranNo ratings yet

- 08 Poredos Lavor JerkovicDocument7 pages08 Poredos Lavor JerkovicDragana MuticNo ratings yet

- Verificacion POESDocument7 pagesVerificacion POESinsegalconsultoresNo ratings yet

- Key Sponsors Held inDocument2 pagesKey Sponsors Held injuliafriedman69No ratings yet

- SK 50 DGDL 126 T: Converter, Inverter, BrakeDocument4 pagesSK 50 DGDL 126 T: Converter, Inverter, Brakemurugan_parvathyNo ratings yet

- ' (C) C' C+,C - (C: CC C CC CCC C CDocument91 pages' (C) C' C+,C - (C: CC C CC CCC C CnuckcheddyNo ratings yet

- SmeaDocument3 pagesSmeaBoiwtosNo ratings yet

- Jar of Hearts (Accompaniment) : Christina PerriDocument5 pagesJar of Hearts (Accompaniment) : Christina Perricar0lynNo ratings yet

- SR22 Insurance FAQs Answers To Common SR22 QuestionsDocument1 pageSR22 Insurance FAQs Answers To Common SR22 QuestionsbroteliliNo ratings yet

- RPS Ners Jiwa 2021 2022-DikonversiDocument13 pagesRPS Ners Jiwa 2021 2022-DikonversiResa ErlinaNo ratings yet

- Lab 1 PDFDocument45 pagesLab 1 PDFBrian PahapayNo ratings yet

- Comentario Al Nuevo Testamento - Tomo 2 - Evangelio Según San Mateo (II)Document21 pagesComentario Al Nuevo Testamento - Tomo 2 - Evangelio Según San Mateo (II)ArninRamirezNo ratings yet

- Tower Crane Footing Structural Design ReDocument14 pagesTower Crane Footing Structural Design ReNeil WayneNo ratings yet

- Tower Crane Footing Structural Design ReDocument14 pagesTower Crane Footing Structural Design ReVirah Sammy ChandraNo ratings yet

- A Capitalist Road To Communism 20 Years AfterDocument23 pagesA Capitalist Road To Communism 20 Years AfterTopeteNo ratings yet

- Buy Bitcoin Instantly PaxfulDocument1 pageBuy Bitcoin Instantly PaxfulHudson HarmonNo ratings yet

- Dorotea Fotivec Prijevodi Tekstova Na Muzejskoj IzložbiDocument32 pagesDorotea Fotivec Prijevodi Tekstova Na Muzejskoj IzložbiDženan DautovićNo ratings yet

- Philippine Banking System: K, I2E.023G?3B.L3?I7Document15 pagesPhilippine Banking System: K, I2E.023G?3B.L3?I7Delica JaneyNo ratings yet

- Divided States: Strategic Divisions in EU-Russia RelationsFrom EverandDivided States: Strategic Divisions in EU-Russia RelationsNo ratings yet

- GATE 2016 How To Prepare For Electronics and Communication Engineering (ECE)Document14 pagesGATE 2016 How To Prepare For Electronics and Communication Engineering (ECE)vikramkolanuNo ratings yet

- RTL Vs Technology SchematicDocument1 pageRTL Vs Technology SchematicvikramkolanuNo ratings yet

- FlipflopsDocument80 pagesFlipflopsvikramkolanuNo ratings yet

- State: Zero 1s Detected State: One 1 Detected State: Two 1s Detected State: Three 1s DetectedDocument8 pagesState: Zero 1s Detected State: One 1 Detected State: Two 1s Detected State: Three 1s DetectedvikramkolanuNo ratings yet

- April 2004Document15 pagesApril 2004vikramkolanuNo ratings yet

- Career Objective:: M Agastya Srivatsav Mobile: +91-9491647647 E-MailDocument2 pagesCareer Objective:: M Agastya Srivatsav Mobile: +91-9491647647 E-MailvikramkolanuNo ratings yet

- Gen Math Summative 2 Set ADocument2 pagesGen Math Summative 2 Set AShehonny VillanuevaNo ratings yet

- New Headway Plus 102 PDFDocument7 pagesNew Headway Plus 102 PDFShathaNo ratings yet

- BALUMA, Kyla Lorenz E. 1st WeekDocument1 pageBALUMA, Kyla Lorenz E. 1st WeekKyla Lorenz BalumaNo ratings yet

- Past Perfect Simple and ContinuousDocument1 pagePast Perfect Simple and ContinuousHoussin ZahroNo ratings yet

- Chapter 4Document19 pagesChapter 4Leonna Dail SintiaNo ratings yet

- The Unit of TranslationDocument7 pagesThe Unit of TranslationalmaNo ratings yet

- Moszkowski - Op. 91 No 2 (Arr.)Document3 pagesMoszkowski - Op. 91 No 2 (Arr.)Panu RauhalaNo ratings yet

- BooK ReviewDocument10 pagesBooK ReviewOjal Sagvekar (OS)No ratings yet

- GIS 821 AssignmentDocument3 pagesGIS 821 AssignmentAqeel TariqNo ratings yet

- Trần Bình Thiện - Ngữ ÂmDocument9 pagesTrần Bình Thiện - Ngữ Âmthien tran100% (1)

- Python Lab 2Document3 pagesPython Lab 2Fiza AmjadNo ratings yet

- The Brave Little Parrot: Literal ComprehensionDocument2 pagesThe Brave Little Parrot: Literal ComprehensionBigyan BasaulaNo ratings yet

- PHILOSOPHY WEEK 1-10 Introduction To The Philosophy of The Human PersonPambungad Sa Pilosopiya NG TaoDocument25 pagesPHILOSOPHY WEEK 1-10 Introduction To The Philosophy of The Human PersonPambungad Sa Pilosopiya NG TaoKen Russel VillamorNo ratings yet

- Insulin Pump System DesignDocument10 pagesInsulin Pump System DesignmikeNo ratings yet

- Ica 16dio G60Document29 pagesIca 16dio G60Diana Amaya NatividadNo ratings yet

- Lesson 4 Worksheet - Using Pythagoras To Solve ProblemsDocument10 pagesLesson 4 Worksheet - Using Pythagoras To Solve ProblemsAye Pyae Pyae HtunNo ratings yet

- KnowledgebaseDocument283 pagesKnowledgebaseعثمان الاغبزيNo ratings yet

- 03 Activity 3 - ARGDocument4 pages03 Activity 3 - ARGstapaNo ratings yet

- Reflection 3.2 Letter WWDocument2 pagesReflection 3.2 Letter WWMaitha ANo ratings yet

- Traverse SurveyingDocument7 pagesTraverse Surveyingmuhammathusinfar01No ratings yet

- Verbos en InglesDocument10 pagesVerbos en InglesMartha SanchezNo ratings yet

- Unprotect WorkbookDocument4 pagesUnprotect WorkbookHeru Susilo NugrohoNo ratings yet