Professional Documents

Culture Documents

HT12D (F Penerima PDF

HT12D (F Penerima PDF

Uploaded by

tis_prasetyoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HT12D (F Penerima PDF

HT12D (F Penerima PDF

Uploaded by

tis_prasetyoCopyright:

Available Formats

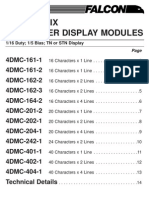

212 Series of Decoders

Features

Operating voltage: 2.4V~12V Address/Data number combination

Low power and high noise immunity CMOS - HT12D: 8 address bits and 4 data bits

technology - HT12F: 12 address bits only

Low standby current Built-in oscillator needs only 5% resistor

Capable of decoding 12 bits of information Valid transmission indicator

12

Pair with Holteks 2 series of encoders Easy interface with an RF or an infrared

Binary address setting transmission medium

Received codes are checked 3 times Minimal external components

Applications

Burglar alarm system Car alarm system

Smoke and fire alarm system Security system

Garage door controllers Cordless telephones

Car door controllers Other remote control systems

General Description

12

The 2 decoders are a series of CMOS LSIs for their local addresses. If no error or unmatched

remote control system applications. They are codes are found, the input data codes are de-

12

paired with Holteks 2 series of encoders (re- coded and then transferred to the output pins.

fer to the encoder/decoder cross reference ta- The VT pin also goes high to indicate a valid

b l e ) . F or p r op er op er a t i on, a p a i r o f transmission.

encoder/decoder with the same number of ad- 12

The 2 series of decoders are capable of decod-

dresses and data format should be chosen. ing informations that consist of N bits of ad-

The decoders receive serial addresses and data dress and 12-N bits of data. Of this series, the

12

from a programmed 2 series of encoders that HT12D is arranged to provide 8 address bits

are transmitted by a carrier using an RF or an and 4 data bits, and HT12F is used to decode 12

IR transmission medium. They compare the se- bits of address information.

rial input data three times continuously with

Selection Table

Function Address Data

VT Oscillator Trigger Package

Part No. No. No. Type

HT12D 8 4 L RC oscillator DIN active Hi 18 DIP/20 SOP

HT12F 12 0 RC oscillator DIN active Hi 18 DIP/20 SOP

Notes: Data type: L stands for latch type data output.

VT can be used as a momentary data output.

1 July 12, 1999

212 Series of Decoders

Block Diagram

O S C 2 O S C 1

O s c illa to r D iv id e r

D a ta S h ift D a ta

L a tc h C ir c u it

R e g is te r

D IN B u ffe r D a ta D e te c to r

S y n c . D e te c to r C o m p a ra to r C o m p a ra to r C o n tr o l L o g ic

T r a n s m is s io n G a te C ir c u it B u ffe r V T

A d d re s s V D D V S S

Note: The address/data pins are available in various combinations (see the address/data table).

Pin Assignment

8 -A d d re s s 8 -A d d re s s 1 2 -A d d re s s 1 2 -A d d re s s

4 -D a ta 4 -D a ta 0 -D a ta 0 -D a ta

N C 1 2 0 N C N C 1 2 0 N C

A 0 1 1 8 V D D A 0 2 1 9 V D D A 0 1 1 8 V D D A 0 2 1 9 V D D

A 1 2 1 7 V T A 1 3 1 8 V T A 1 2 1 7 V T A 1 3 1 8 V T

A 2 3 1 6 O S C 1 A 2 4 1 7 O S C 1 A 2 3 1 6 O S C 1 A 2 4 1 7 O S C 1

A 3 4 1 5 O S C 2 A 3 5 1 6 O S C 2 A 3 4 1 5 O S C 2 A 3 5 1 6 O S C 2

A 4 5 1 4 D IN A 4 6 1 5 D IN A 4 5 1 4 D IN A 4 6 1 5 D IN

A 5 6 1 3 D 1 1 A 5 7 1 4 D 1 1 A 5 6 1 3 A 1 1 A 5 7 1 4 A 1 1

A 6 7 1 2 D 1 0 A 6 8 1 3 D 1 0 A 6 7 1 2 A 1 0 A 6 8 1 3 A 1 0

A 7 8 1 1 D 9 A 7 9 1 2 D 9 A 7 8 1 1 A 9 A 7 9 1 2 A 9

V S S 9 1 0 D 8 V S S 1 0 1 1 D 8 V S S 9 1 0 A 8 V S S 1 0 1 1 A 8

H T 1 2 D H T 1 2 D H T 1 2 F H T 1 2 F

1 8 D IP 2 0 S O P 1 8 D IP 2 0 S O P

2 July 12, 1999

212 Series of Decoders

Pin Description

Internal

Pin Name I/O Description

Connection

NMOS

Input pins for address A0~A11 setting

A0~A11 I TRANSMISSION

They can be externally set to VDD or VSS.

GATE

D8~D11 O CMOS OUT Output data pins

DIN I CMOS IN Serial data input pin

VT O CMOS OUT Valid transmission, active high

OSC1 I OSCILLATOR Oscillator input pin

OSC2 O OSCILLATOR Oscillator output pin

VSS I Negative power supply (GND)

VDD I Positive power supply

Approximate internal connection circuits

N M O S

T R A N S M IS S IO N C M O S O U T C M O S IN O S C IL L A T O R

G A T E

E N O S C 2

O S C 1

Absolute Maximum Ratings

Supply Voltage...............................-0.3V to 13V Storage Temperature.................-50C to 125C

Input Voltage....................VSS-0.3 to VDD+0.3V Operating Temperature ..............-20C to 75C

Note: These are stress ratings only. Stresses exceeding the range specified under Absolute Maxi-

mum Ratings may cause substantial damage to the device. Functional operation of this de-

vice at other conditions beyond those listed in the specification is not implied and prolonged

exposure to extreme conditions may affect device reliability.

3 July 12, 1999

212 Series of Decoders

Electrical Characteristics Ta=25C

Test Conditions

Symbol Parameter Min. Typ. Max. Unit

VDD Conditions

VDD Operating Voltage 2.4 5 12 V

5V 0.1 1 mA

ISTB Standby Current Oscillator stops

12V 2 4 mA

IDD No load

Operating Current 5V 200 400 mA

fOSC=150kHz

Data Output Source VOH=4.5V

5V -1 -1.6 mA

Current (D8~D11)

IO

Data Output Sink VOL=0.5V

5V 1 1.6 mA

Current (D8~D11)

VT Output Source Current VOH=4.5V -1 -1.6 mA

IVT 5V

VT Output Sink Current VOL=0.5V 1 1.6 mA

VIH H Input Voltage 5V 3.5 5 V

VIL L Input Voltage 5V 0 1 V

fOSC Oscillator Frequency 5V ROSC=51kW 150 kHz

4 July 12, 1999

212 Series of Decoders

Functional Description

Operation Flowchart

12

The 2 series of decoders provides various com- The oscillator is disabled in the standby state

binations of addresses and data pins in differ- and activated when a logic high signal applies

12

ent packages so as to pair with the 2 series of to the DIN pin. That is to say, the DIN should be

encoders. kept low if there is no signal input.

The decoders receive data that are transmitted

by an encoder and interpret the first N bits of P o w e r o n

code period as addresses and the last 12-N bits

as data, where N is the address code number. A

signal on the DIN pin activates the oscillator S ta n d b y m o d e

which in turn decodes the incoming address

and data. The decoders will then check the re- N o D is a b le V T &

ceived address three times continuously. If the C o d e in ? ig n o r e th e r e s t o f

th is w o r d

received address codes all match the contents of

Y e s

the decoders local address, the 12-N bits of

data are decoded to activate the output pins

A d d r e s s b its N o

and the VT pin is set high to indicate a valid m a tc h e d ?

transmission. This will last unless the address

code is incorrect or no signal is received. Y e s

The output of the VT pin is high only when the S to re d a ta

transmission is valid. Otherwise it is always

low.

M a tc h N o

p r e v io u s s to r e d

Output type d a ta ?

12

Of the 2 series of decoders, the HT12F has no Y e s

data output pin but its VT pin can be used as a

momentary data output. The HT12D, on the N o 3 tim e s

o f c h e c k in g

other hand, provides 4 latch type data pins c o m p le te d ?

whose data remain unchanged until new data

are received. Y e s

L a tc h d a ta

Part Data Address Output Operating to o u tp u t &

No. Pins Pins Type Voltage a c tiv a te V T

HT12D 4 8 Latch 2.4V~12V

N o A d d re s s o r

d a ta e rro r ?

HT12F 0 12 2.4V~12V

Y e s

5 July 12, 1999

212 Series of Decoders

Decoder timing

E n c o d e r

T r a n s m is s io n

E n a b le

< 1 w o rd

E n c o d e r

D O U T

4 w o rd s T r a n s m itte d 4 w o rd s

1 4

C o n tin u o u s ly 1 4

2 c lo c k s 2 c lo c k s

D e c o d e r V T

c h e c k c h e c k

L a tc h e d

D a ta O u t

Encoder/Decoder cross reference table

Package

Decoders

Data Pins Address Pins VT Pair Encoder Encoder Decoder

Part No.

DIP SOP DIP SOP

HT12A 18 20

HT12D 4 8 18 20

HT12E 18 20

HT12A 18 20

HT12F 0 12 18 20

HT12E 18 20

Address/Data sequence

12

The following table provides address/data sequence for various models of the 2 series of decoders. A

correct device should be chosen according to the requirements of the individual addresses and data.

Address/Data Bits

Part No.

0 1 2 3 4 5 6 7 8 9 10 11

HT12D A0 A1 A2 A3 A4 A5 A6 A7 D8 D9 D10 D11

HT12F A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11

6 July 12, 1999

212 Series of Decoders

Oscillator frequency vs supply voltage

fo s c

(S c a le )

R o s c (9 )

4 .0 0

2 7 k

3 .5 0

3 0 k

3 3 k

3 .0 0

3 6 k

3 9 k

4 3 k

2 .5 0

4 7 k

5 1 k

2 .0 0 5 6 k

6 2 k

6 8 k

7 5 k

1 .5 0 8 2 k

1 0 0 k

1 2 0 k

(1 0 0 k H z )1 .0 0

1 5 0 k

1 8 0 k

2 2 0 k

0 .5 0

0 .2 5

2 3 4 5 6 7 8 9 1 0 1 1 1 2 1 3 V D D (V D C )

The recommended oscillator frequency is fOSCD (decoder) @ 50 fOSCE (HT12E encoder)

1

@ fOSCE (HT12A encoder).

3

7 July 12, 1999

212 Series of Decoders

Application Circuits

R e c e iv e r C ir c u it R e c e iv e r C ir c u it

V D D V D D

1 1 8 1 1 8

A 0 V D D A 0 V D D

2 1 7 2 1 7

A 1 V T A 1 V T

3 1 6 3 1 6

A 2 O S C 1 A 2 O S C 1

4 1 5 R O S C 4 1 5 R O S C

A 3 O S C 2 A 3 O S C 2

5 1 4 5 1 4

A 4 D IN A 4 D IN

6 1 3 6 1 3

A 5 D 1 1 A 5 A 1 1

7 1 2 7 1 2

A 6 D 1 0 A 6 A 1 0

8 1 1 8 1 1

A 7 D 9 A 7 A 9

9 1 0 9 1 0

V S S D 8 V S S A 8

H T 1 2 D H T 1 2 F

Notes: Typical infrared receiver: PIC-12043T/PIC-12043S (KODESHI CORP.)

or LTM9052 (LITEON CORP.)

Typical RF receiver: JR-200 (JUWA CORP.)

RE-99 (MING MICROSYSTEM, U.S.A.)

8 July 12, 1999

212 Series of Decoders

Holtek Semiconductor Inc. (Headquarters)

No.3 Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan, R.O.C.

Tel: 886-3-563-1999

Fax: 886-3-563-1189

Holtek Semiconductor Inc. (Taipei Office)

5F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan, R.O.C.

Tel: 886-2-2782-9635

Fax: 886-2-2782-9636

Fax: 886-2-2782-7128 (International sales hotline)

Holtek Microelectronics Enterprises Ltd.

RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong

Tel: 852-2-745-8288

Fax: 852-2-742-8657

Copyright 1999 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek

assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are

used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications

will be suitable without further modification, nor recommends the use of its products for application that may pres-

ent a risk to human life due to malfunction or otherwise. Holtek reserves the right to alter its products without prior

notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

9 July 12, 1999

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Assignment 4 Electoral Politics PDFDocument4 pagesAssignment 4 Electoral Politics PDFMohamed Tarek Kamar33% (3)

- Windchill PDM Essentials-eBookDocument12 pagesWindchill PDM Essentials-eBookMiguel Farah100% (1)

- 4 DMCDocument20 pages4 DMCapi-3700809100% (1)

- Bob B. Barchi: B.S. Computer ScienceDocument1 pageBob B. Barchi: B.S. Computer ScienceAnonymous 9MXNxiNo ratings yet

- 4GLM 12232-2Document6 pages4GLM 12232-2api-3700809No ratings yet

- 4GLM 12232-5lde-5vDocument6 pages4GLM 12232-5lde-5vapi-3700809No ratings yet

- 4GLM 12232-5issue2Document6 pages4GLM 12232-5issue2api-3700809No ratings yet

- Max 232 PDFDocument36 pagesMax 232 PDFAndré Leonardo SilvaNo ratings yet

- H21A1 - Sensor Optico BarreiraDocument6 pagesH21A1 - Sensor Optico BarreiraAlexitho MadrigalNo ratings yet

- L293DDocument7 pagesL293Dapi-370080950% (2)

- GLM240128Document35 pagesGLM240128api-3700809No ratings yet

- Datasheet 7805Document34 pagesDatasheet 7805Mohsin AhmadNo ratings yet

- HT12EDocument13 pagesHT12Eapi-3700809100% (2)

- Datasheet l298bDocument14 pagesDatasheet l298bgioganNo ratings yet

- 4GLM 12232-2Document6 pages4GLM 12232-2api-3700809No ratings yet

- 4 GLM 24064Document19 pages4 GLM 24064api-3700809No ratings yet

- Walden by Thoreau, Henry David, 1817-1862Document180 pagesWalden by Thoreau, Henry David, 1817-1862Gutenberg.org100% (1)

- CEH Lesson 5 - Web Server HackingDocument25 pagesCEH Lesson 5 - Web Server HackingLouise RealNo ratings yet

- QTP Advanced A Programmatic ApproachDocument17 pagesQTP Advanced A Programmatic ApproachAishaNo ratings yet

- Extract Cad Data PDFDocument2 pagesExtract Cad Data PDFDemarcusNo ratings yet

- AP-74260 SM Blizzard Rev1.0Document244 pagesAP-74260 SM Blizzard Rev1.0Depapel Suministros de RotulaciónNo ratings yet

- RAC DOC - NewDocument64 pagesRAC DOC - Newsushma bugudalaNo ratings yet

- Autoflame PC Software GuideDocument102 pagesAutoflame PC Software GuideSebastianCastilloNo ratings yet

- Design and Development of Diu Hostel Management SystemDocument14 pagesDesign and Development of Diu Hostel Management Systemtoushif ahmedNo ratings yet

- Pixhawk Quick StartDocument159 pagesPixhawk Quick StartTULUSHADI50% (2)

- Kamran HashmiDocument2 pagesKamran HashmihasanNo ratings yet

- EGX - DatasheetDocument5 pagesEGX - DatasheetvolgaxNo ratings yet

- CV 6-UslettreDocument1 pageCV 6-UslettreTomás EdmilsonNo ratings yet

- Tle Tech Drafting 10-q1-m5Document14 pagesTle Tech Drafting 10-q1-m5JUNARY DUMALAURONNo ratings yet

- 1901 State of Mobile Main en App AnnieDocument155 pages1901 State of Mobile Main en App AnnieKarthikNo ratings yet

- Developing A Rapid Prototyping Method Using A Matlab/Simulink/Fpga Development Environment To Enable Importing Legacy CodeDocument7 pagesDeveloping A Rapid Prototyping Method Using A Matlab/Simulink/Fpga Development Environment To Enable Importing Legacy Codebeddar antarNo ratings yet

- CancerDataCollect LinksPaperDocument5 pagesCancerDataCollect LinksPapersanNo ratings yet

- Gaurav Dalvi Atlassian55Document5 pagesGaurav Dalvi Atlassian55Himalayan MerchantsNo ratings yet

- Project PPT 1Document13 pagesProject PPT 1Shubham Jadhav100% (2)

- VehicleDocument13 pagesVehicleshobhit100% (1)

- A TCP TutorialDocument11 pagesA TCP Tutorialpfck4589No ratings yet

- DAY 5 - EGI - ITSM - 72SP05CustomerDocument100 pagesDAY 5 - EGI - ITSM - 72SP05CustomeramolNo ratings yet

- HP Pavilion Zx5000 Zv5000 Compaq Presario r3000 Compaq Business Nx9100Document272 pagesHP Pavilion Zx5000 Zv5000 Compaq Presario r3000 Compaq Business Nx9100Micu Adrian DanutNo ratings yet

- ZCC PickAndPlace Interface Option - EN UsDocument2 pagesZCC PickAndPlace Interface Option - EN UsRadoNo ratings yet

- Oracle R12 BOM-WIP - SyllabusDocument5 pagesOracle R12 BOM-WIP - SyllabusNidhi SaxenaNo ratings yet

- SM190003EN - 022011 - LR - Infusion Systems Product CatalogDocument44 pagesSM190003EN - 022011 - LR - Infusion Systems Product CatalogmochkurniawanNo ratings yet

- Buk 9222Document13 pagesBuk 9222Olga PlohotnichenkoNo ratings yet

- Completion Certificate Nadia DRRPDocument1 pageCompletion Certificate Nadia DRRPaniket geetashreeNo ratings yet