Professional Documents

Culture Documents

ReSpeaker 4-Mic Array For Raspberry Pi v1.0

Uploaded by

Shiva SiddharthOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

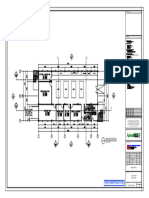

ReSpeaker 4-Mic Array For Raspberry Pi v1.0

Uploaded by

Shiva SiddharthCopyright:

Available Formats

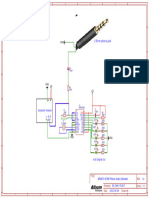

1 2 3 4 5 6

A A

REV Descripton DATE designer

V1.0 INITIAL RELEASE 2017/07/10 Qxn

B B

C C

D

Seeed Studio D

TITLE:

CC-BY-SA Design: Check:

Date: 2017/7/11 11:38 Vision:

1 2 3 4 5 6

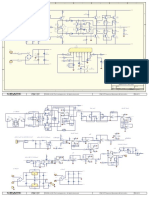

1 2 3 4 5 6

A A

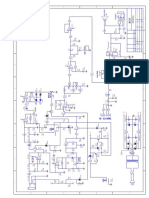

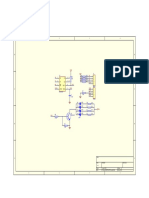

CJ2305

VDD_5V/3.3B 500mA R1

R33

B B

Q1

10k

Q2

GPIO5/3.1C R34 10R

2N7002

10k R35

1 D1 APA102-2020

8 1 D2 APA102-2020

8 1 D3 APA102-2020

8 1 D4 APA102-2020

8 1 D5 APA102-2020

8 1 D6 APA102-2020

8

10R VDD VDD1 VDD VDD1 VDD VDD1 VDD VDD1 VDD VDD1 VDD VDD1

4 3 4 3 4 3 4 3 4 3 4 3

SPI_MOSI/3.1B 10R SDI SDO SDI SDO SDI SDO SDI SDO SDI SDO SDI SDO

R3 5 2 5 2 5 2 5 2 5 2 5 2

SPI_SCLK/3.1B CKI CKO CKI CKO CKI CKO CKI CKO CKI CKO CKI CKO

R4 6 7 6 7 6 7 6 7 6 7 6 7

GND GND1 GND GND1 GND GND1 GND GND1 GND GND1 GND GND1

C1

C2

10uF

10uF

7 6 7 6 7 6 7 6 7 6 7 6

GND1 GND GND1 GND GND1 GND GND1 GND GND1 GND GND1 GND

C 2

3

CKO CKI

5

4

2

3

CKO CKI

5

4

2

3

CKO CKI

5

4

2

3

CKO CKI

5

4

2

3

CKO CKI

5

4

2

3

CKO CKI

5

4

C

SDO SDI SDO SDI SDO SDI SDO SDI SDO SDI SDO SDI

8 1 8 1 8 1 8 1 8 1 8 1

VDD1 VDD VDD1 VDD VDD1 VDD VDD1 VDD VDD1 VDD VDD1 VDD

APA102-2020 D12 APA102-2020 D11 APA102-2020 D10 APA102-2020 D9 APA102-2020 D8 APA102-2020 D7

D

Seeed Studio D

TITLE:

CC-BY-SA Design: Check:

Date: 2017/7/11 11:38 Vision:

1 2 3 4 5 6

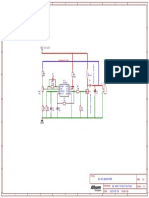

1 2 3 4 5 6

A A

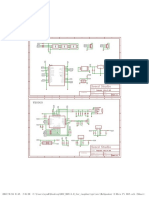

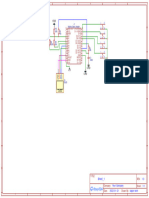

VDD_3V3/4.1B

VDD_5V/2.1B

VDD_3V3/4.1B

1 2

3V3 5V0

3 4

I2C_SDA/4.1B GPIO2/SDA1 5V0

5 6

I2C_SCL/4.1B GPIO3/SCL1 GND

7 8

GPIO4/GCKL TXD0/GPIO14

9 10 R29 10k

GND RXD0/GPIO15 I2C_SDA/4.1B

B GPIO17

11

GPIO17/GEN0 GPIO18

12 I2S_CLK/4.1B I2C_SCL/4.1B R30 10k B

13 14

GPIO27/GEN2 GND

15 16

GPIO22/GEN3 GEN4/GPIO23

17 18

3V3 GEN5/GPIO24

19 20

SPI_MOSI/2.1C GPIO10/MOSI GND

21 22

GPIO9/MISO GEN/6GPIO25

23 24

SPI_SCLK/2.1C GPIO11/SCLK CE0/GPIO8

25 26

GND CE/GPIO7

27 28

ID_SD ID_SC

29 30

GPIO5/2.1B GPIO5 GND

31 32

GPIO6 GPIO12 GPIO12 J1 Grove J2 Grove

33 34

GPIO13 GPIO13 GND 1 1

35 36 I2C_SCL/4.1B GPIO12

I2S_LRCLK/4.1B GPIO19 GPIO16 2 2

37 38 I2C_SDA/4.1B GPIO13

GPIO26 GPIO20 I2S_ADC/4.1B 3 3

39 40 VDD_3V3/4.1B VDD_3V3/4.1B

GND GPIO21 I2S_DAC 4 4

C C

D

Seeed Studio D

TITLE:

CC-BY-SA Design: Check:

Date: 2017/7/11 11:38 Vision:

1 2 3 4 5 6

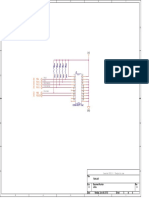

1 2 3 4 5 6

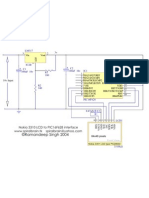

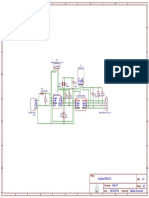

AVCC_3V3

MIC1

C3 100nF 1

VDD

A 2 A

1uF

1uF

GND

C4 100nF R6 0R 3

GAIN

C7 10nF R7 51R 1% 4

MIC1P OUT

TP1

TP2

TP3

C5

C6

R32 0R AVCC_3V3 C8 SPU0414HR5H-SB 312030079

U1 AC108

45 46 C9 1uF 33pF

VDD_5V/3.3B DLDOIN DLDOOUT

27 C10 10nF R8 51R 1%

VDD_5V/3.3B ALDOIN 30 C11 1uF MIC1N

R9 10k 44 VREF

CP_EN 28 C12 1uF

C13 1uF 43 ALDOOUT

CP_VPP 29 C14 1uF AVCC_3V3

42 RVCC

CP_VPN 20 C15 1uF MIC2

AVCC_ANA1

C16 1uF 7 40 C17 1uF C18 100nF 1

VCC_DIO AVCC_ANA2 VDD

C19 1uF 11 31 C20 1uF 2

VCC_I2S VRP GND

32 C21 100nF R10 0R 3

R11 10k 19 VRN GAIN

VDD_3V3/3.5B RSTN C22 10nF R12 51R 1% 4

10 41 MIC2P OUT

I2C_SDA/3.5B SDA VDD_CPOUT TP4

9 6

10uF

I2C_SCL/3.5B SCK VDD_CORE C24 SPU0414HR5H-SB 312030079

C23

4

DEV_ID0 21

B 5

TEST

MICBIAS1

C25 10nF

33pF

R13 51R 1%

B

22 MIC2N

R14 10R 8 MIC1P MIC1P

MCLK MCLK 23

R15 10R 15 MIC1N MIC1N

I2S_CLK/3.3B BCLK AVCC_3V3

R16 10R 18 24

I2S_LRCLK/3.1C LRCK MICBIAS2 MIC3

R17 10R 16

I2S_ADC/3.3C SDOUT1 25 C26 100nF 1

17 MIC2P MIC2P VDD

SDOUT2 26 2

MIC2N MIC2N GND

R18 10R 48 C27 100nF R19 0R 3

DMICDAT1 GPIO_1/DMICDAT1 34 GAIN

TP5 R20 10R 1 MICBIAS3 C28 10nF R21 51R 1% 4

DMICCLK GPIO_2/DMICCLK MIC3P OUT

TP6 R22 10R 2 35

DMICDAT2 GPIO_3/DMICDAT2 MIC3P MIC3P C29 SPU0414HR5H-SB 312030079

TP7 R23 10R 3 36

GPIO4 GPIO_4 MIC3N MIC3N

TP8 12 33pF

NC1 37

13 MICBIAS4 C30 10nF R24 51R 1%

NC2 MIC3N

AGND

14 38

NC3 MIC4P

GND

MIC4P

47 39

NC4 MIC4N MIC4N AVCC_3V3

MIC4

C C

33

PAD

C31 100nF 1

VDD

2

GND

C32 100nF R26 0R 3

GAIN

C33 10nF R27 51R 1% 4

MIC4P OUT

C34 SPU0414HR5H-SB 312030079

33pF

MIC4N C35 10nF R28 51R 1%

100nF

VDD_3V3/3.5B

X1 24MHz 306020014 C36

D

1

2

ENABLE

GND

VDD

OUT

4

3 MCLK

Seeed Studio D

TITLE:

CC-BY-SA Design: qxn

Check:

Date: 2017/7/11 11:38 Vision: v1.0

1 2 3 4 5 6

You might also like

- Updated Media List HospitalityDocument14 pagesUpdated Media List HospitalityGarima Jagtani50% (2)

- Meghan markle-WPS OfficeDocument11 pagesMeghan markle-WPS OfficeBernadette BoquecosaNo ratings yet

- Schematic - RF Transmitter and Reciver - 2022!08!05Document1 pageSchematic - RF Transmitter and Reciver - 2022!08!05Soheil Alizadeh100% (1)

- Sports Media List - NewDocument61 pagesSports Media List - Newkarnika puranik100% (1)

- RTL9210-VB-CG Demo V203 PDFDocument5 pagesRTL9210-VB-CG Demo V203 PDFCenusa MihaiNo ratings yet

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- RX15 - SchematicsDocument1 pageRX15 - SchematicsRainhardfrostNo ratings yet

- Infografe Pag SimplesDocument153 pagesInfografe Pag SimplesElizabethSaadCorrêaNo ratings yet

- ReSpeaker 2-Mics Pi HAT - SCHDocument1 pageReSpeaker 2-Mics Pi HAT - SCHbomman69No ratings yet

- SM-T285 Esquematico Completo Anibal Garcia IrepairDocument10 pagesSM-T285 Esquematico Completo Anibal Garcia IrepairJ Ignacio MartinezNo ratings yet

- AAV8790601-00 MergedDocument7 pagesAAV8790601-00 Mergedengineeringcem99No ratings yet

- ©ramandeep Singh 2004: Nokia 3310 LCD To PIC16F628 InterfaceDocument1 page©ramandeep Singh 2004: Nokia 3310 LCD To PIC16F628 InterfaceAnonymous GxeR0L100% (2)

- D2 D3 D4 D5: Revisions CDocument2 pagesD2 D3 D4 D5: Revisions CSemih YelkenNo ratings yet

- TCS3200 Color SensorColor Detector Schematics PDFDocument1 pageTCS3200 Color SensorColor Detector Schematics PDFsiogNo ratings yet

- Modulo 11Document1 pageModulo 11charlyNo ratings yet

- Schematic Ardu Oscilloscope 2022-01-21 Kes1kt9bmpDocument1 pageSchematic Ardu Oscilloscope 2022-01-21 Kes1kt9bmpinsincos administrativoNo ratings yet

- DFR0034SCH V2.0 PDFDocument1 pageDFR0034SCH V2.0 PDFFelipe GarciaNo ratings yet

- SM-J260G Esquematico Completo Anibal Garcia IrepairDocument34 pagesSM-J260G Esquematico Completo Anibal Garcia Irepairloja testeNo ratings yet

- DFR0034SCH V2.0 - Schematic PDFDocument1 pageDFR0034SCH V2.0 - Schematic PDFjoxNo ratings yet

- Sound Sensor 2.0: R3 30K R7 10KDocument1 pageSound Sensor 2.0: R3 30K R7 10KJose Aviles PachecoNo ratings yet

- Schematic Isolated-INA219 Sheet-1 20190330172040Document1 pageSchematic Isolated-INA219 Sheet-1 2019033017204031482No ratings yet

- Designed by Checked by Approved by Date DateDocument2 pagesDesigned by Checked by Approved by Date DateĐoàn bsNo ratings yet

- Schematic - How To Make MT8870 DTMF Phone Audio Decoder - 2022-08-08Document1 pageSchematic - How To Make MT8870 DTMF Phone Audio Decoder - 2022-08-08Florencio cancheNo ratings yet

- Wio Tracker 1110 v1.0 - SCH - PDF - 20230822Document4 pagesWio Tracker 1110 v1.0 - SCH - PDF - 20230822marcelu.phdNo ratings yet

- SPF 27486 Kit33813 SCHDocument3 pagesSPF 27486 Kit33813 SCH刘杰No ratings yet

- RT-RK: PIC901 PIC902 PIC902 PIC901Document15 pagesRT-RK: PIC901 PIC902 PIC902 PIC901Алексей ГомоновNo ratings yet

- Elektor BusDocument6 pagesElektor BusFernando VidalNo ratings yet

- Guia LCD 16fDocument2 pagesGuia LCD 16fAna Sofia MamaniNo ratings yet

- RXDocument1 pageRXVenkat RamaiahNo ratings yet

- Drive of 8-Digit 7-Segment DisplayDocument2 pagesDrive of 8-Digit 7-Segment Displayabba123No ratings yet

- Desktop MillDocument1 pageDesktop MilljaakNo ratings yet

- Aditya Aji Fx. Fendi Fx. Fendi 26/09/18: Designed by Checked by Approved by Date DateDocument1 pageAditya Aji Fx. Fendi Fx. Fendi 26/09/18: Designed by Checked by Approved by Date DateAditya AjiNo ratings yet

- SchmeaticsDocument1 pageSchmeaticsmuhammad samrozNo ratings yet

- SM-T550 Esquematico CompletoDocument10 pagesSM-T550 Esquematico CompletogilroleNo ratings yet

- PDF Created With Pdffactory Pro Trial Version: Coron Jet - Utsch - SheetDocument1 pagePDF Created With Pdffactory Pro Trial Version: Coron Jet - Utsch - SheetdNo ratings yet

- SM-W727V Esquematico Completo Anibal Garcia IrepairDocument13 pagesSM-W727V Esquematico Completo Anibal Garcia IrepairCris CellNo ratings yet

- Modulador AM XR2206Document1 pageModulador AM XR2206Brandon DamianNo ratings yet

- J12 5 Switch Bd1 Schematic PDFDocument2 pagesJ12 5 Switch Bd1 Schematic PDFhighlanderoneNo ratings yet

- Schematic V1.0Document1 pageSchematic V1.0kukuhsatriowibowoNo ratings yet

- Schematic Combo LedDocument12 pagesSchematic Combo LedH S MannNo ratings yet

- ReceivedDocument8 pagesReceivedDHANEESH VELLILAPULLINo ratings yet

- PSM12P: ©2008 LOUD Technologies Inc. All Rights Re Served PSM12P Powered Speakers SchematicsDocument2 pagesPSM12P: ©2008 LOUD Technologies Inc. All Rights Re Served PSM12P Powered Speakers SchematicsCamila SuarezNo ratings yet

- EN21C Surf. RoughnessDocument1 pageEN21C Surf. RoughnessJujhaar BhinderNo ratings yet

- TM1650Document1 pageTM1650mingrenttyyNo ratings yet

- Oscilador Baud Rate para 90HzDocument1 pageOscilador Baud Rate para 90HzmplennaNo ratings yet

- FFRDocument1 pageFFRprathyushareddyNo ratings yet

- Schematic - New 12V Battery Charger Circuit - 2022-12-09Document1 pageSchematic - New 12V Battery Charger Circuit - 2022-12-09FRANCISCO SANABRIANo ratings yet

- SKP VZ194-114-schDocument5 pagesSKP VZ194-114-schSalim ÖzcanNo ratings yet

- Schematic Shift-Registers Sheet-1 20181117003103 PDFDocument1 pageSchematic Shift-Registers Sheet-1 20181117003103 PDFHà Văn ThạnhNo ratings yet

- Stepper Motor Controller: Gert BaarsDocument2 pagesStepper Motor Controller: Gert BaarsJosé ManuelNo ratings yet

- Schematic - DC DC BOOSTER - 2022-05-20Document1 pageSchematic - DC DC BOOSTER - 2022-05-20Duzão Agnusrock Lembke BassNo ratings yet

- Double Muff (EC2010)Document1 pageDouble Muff (EC2010)mark fakundinyNo ratings yet

- 5 - JtagDocument1 page5 - JtagHungNo ratings yet

- Designed by Checked by Approved by Date DateDocument1 pageDesigned by Checked by Approved by Date DateĐoàn bsNo ratings yet

- SM-J320F Esquematico Completo Anibal Garcia Irepair PDFDocument9 pagesSM-J320F Esquematico Completo Anibal Garcia Irepair PDFgustavoNo ratings yet

- Sdo-Dates-A.labh2p-001 2Document1 pageSdo-Dates-A.labh2p-001 2tulus sianturiNo ratings yet

- Exposure Table Timer - SCHDocument1 pageExposure Table Timer - SCHRusselguide ElectronicsNo ratings yet

- Nombre:Midwar Miguel Chura Chura Codigo Fuente Contador Descendente de 200 - 50 de 10 en 10Document3 pagesNombre:Midwar Miguel Chura Chura Codigo Fuente Contador Descendente de 200 - 50 de 10 en 10Midwar Miguel ChuraNo ratings yet

- TV Vertical Deflection Output Circuit: DescriptionDocument8 pagesTV Vertical Deflection Output Circuit: DescriptionSv KoNo ratings yet

- Clock Generator - PDSPRJ 7/24/2019 Clock Generator - PDSPRJDocument1 pageClock Generator - PDSPRJ 7/24/2019 Clock Generator - PDSPRJAsa PutraNo ratings yet

- Nap Isp LPTDocument1 pageNap Isp LPTgaikieuucNo ratings yet

- IndustrialDocument1 pageIndustrialSergio Romero100% (1)

- STM32F103C8T6 Dev Board SCH PDFDocument1 pageSTM32F103C8T6 Dev Board SCH PDFTeuku Makmur TsaniNo ratings yet

- SM-T285M Esquematico Completo Anibal Garcia IrepairDocument8 pagesSM-T285M Esquematico Completo Anibal Garcia IrepairJ Ignacio MartinezNo ratings yet

- Campus JournalismDocument32 pagesCampus JournalismrommeldrmNo ratings yet

- List of Licences Issued STV From Pemra SiteDocument5 pagesList of Licences Issued STV From Pemra SitemoinsNo ratings yet

- Listening CH 6&7Document3 pagesListening CH 6&7Budiman0% (1)

- 2007 - Edition 7Document12 pages2007 - Edition 7The Oppidan PressNo ratings yet

- Data Ketua PC & PW Jra Nusantara PDFDocument10 pagesData Ketua PC & PW Jra Nusantara PDFAhmad Lintang SongoNo ratings yet

- Barkha Dutt: World Economic ForumDocument4 pagesBarkha Dutt: World Economic ForumK.l. NagendraNo ratings yet

- Main Cast Announced For Netflix's Live-Action One Piece SeriesDocument1 pageMain Cast Announced For Netflix's Live-Action One Piece SeriesSam PaulNo ratings yet

- Introduction To JournalismDocument19 pagesIntroduction To JournalismJen MojicaNo ratings yet

- Daily News Toronto - Toronto News and NewspapersDocument2 pagesDaily News Toronto - Toronto News and NewspaperssaigonbaoNo ratings yet

- Surrealismo - Fiona BradleyDocument30 pagesSurrealismo - Fiona BradleyLaís LisboaNo ratings yet

- Public Speaking AssignmentDocument4 pagesPublic Speaking AssignmentSiti NursyafiqahNo ratings yet

- An Inspiring Talk With Sotiris Danezis / by Passarivaki MariaDocument11 pagesAn Inspiring Talk With Sotiris Danezis / by Passarivaki MariaMaria PassarivakiNo ratings yet

- Little Red Riding Hood (Sybille Schenker)Document1 pageLittle Red Riding Hood (Sybille Schenker)Pip JohnsonNo ratings yet

- News - Young People Are Not Watching TV NewsDocument2 pagesNews - Young People Are Not Watching TV NewsCassiane OgliariNo ratings yet

- Dr. Keith Ablow Launches Pain-2-Power Person of The Week: Total Pickup Over TimeDocument4 pagesDr. Keith Ablow Launches Pain-2-Power Person of The Week: Total Pickup Over TimeKeith AblowNo ratings yet

- NAVYAATA The Real ExperienceDocument4 pagesNAVYAATA The Real ExperienceMadhupriya DugarNo ratings yet

- Propaganda Model: Q1:What Are Five Filters of ?Document3 pagesPropaganda Model: Q1:What Are Five Filters of ?hafsa rashidNo ratings yet

- AMC Diary - 2011Document179 pagesAMC Diary - 2011Kalpesh PatelNo ratings yet

- Amy K Lieu - Resume - Reporter/MMJDocument1 pageAmy K Lieu - Resume - Reporter/MMJAmy LieuNo ratings yet

- Journalistic WritingDocument1 pageJournalistic WritingMaria Layca VargasNo ratings yet

- E F Eng l1 l2 Si 068Document1 pageE F Eng l1 l2 Si 068Simona ButeNo ratings yet

- FTA PACKAGE (MRP: 130/-+ Applicable Tax)Document1 pageFTA PACKAGE (MRP: 130/-+ Applicable Tax)UtpalSahaNo ratings yet

- Lecture 8 Agenda Settings: Jess O'Mahony s42921507Document13 pagesLecture 8 Agenda Settings: Jess O'Mahony s42921507jessomahonyNo ratings yet

- 9 Elements of JournalismDocument1 page9 Elements of JournalismCristina Rocas-Bisquera100% (1)

- Detecting Bias in The MediaDocument1 pageDetecting Bias in The MediaHahahahaendndmdNo ratings yet

- Institut Pendidikan Guru Kampus Tengku Ampuan AfzanDocument7 pagesInstitut Pendidikan Guru Kampus Tengku Ampuan Afzanmiszja29No ratings yet