Professional Documents

Culture Documents

MC33072 PDF

MC33072 PDF

Uploaded by

Carlos Posada0 ratings0% found this document useful (0 votes)

28 views16 pagesOriginal Title

MC33072.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

28 views16 pagesMC33072 PDF

MC33072 PDF

Uploaded by

Carlos PosadaCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 16

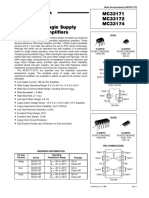

MOTOROLA

SEMICONDUCTOR

TECHNICAL DATA

High Slew Rate, Wide Bandwidth,

Single Supply Operational Amplifiers

Quality bipolar fabrication with innovative design concepts are employed for

‘the MC33071/72/74, MC34071/72/74, MC35071/72/74 series of monolithic

operational amplifiers. This series of operational amplifiers offer 4.5 MHz of gain

bandwidth product, 13 Vius stew rate and fast setting time without the use of

FET device technology. Although this series canbe operated from splitsupplies,

itis particularly suited for single supply operation, since the common mode input

voltage range includes ground potential (Ve). With A Darington inputstage, this,

series exhibits high input resistance, low input offset voltage and high gain. The

all NPN output stage, characterized by no deadband crossover distortion and

large output voltage swing, provides high capacitance drive capability, excellent

phase and gain margins, low open-loop high trequency output impedance and

‘symmetrical source/sink AC frequency response.

The MC33071/72/74, MC34071/72/73, MC3507 1/72/74 series of devices are

‘available in standard or prime performance (A Sulfix) grades and are specified

‘over the commercial, industrialivehicular or military temperature ranges. The

‘compete series of single, dual and quad operational amplifiers are available in

the plastic, ceramic DIP and SOIC surface mount packages.

© Wide Bandwidth: 4.5 MHz

High Slew Rate: 13 Vius

Fast Setting Time: 1.1 ps 10 0.1%

Wide Single Supply Operation: 3.0 V to 44.V

‘Wide Input Common Mode Voltage Range: Includes Ground (VEE)

Low Input Ottset Voltage: 3.0 mV Maximum (A Suffix)

Large Output Voltage Swing: ~14.7 V to +14 V (with +15 V Supplies)

Large Capacitance Drive Capability: 0 pF to 10,000 pF

Low Total Harmonic Distortion: 0.02%

Excollent Phase Margin: 60°

Excellent Gain Margin: 12 68

Output Short Circuit Protection

ESD Diodes/Clamps Provide Input Protection for Dual, and Quad

ORDERING INFORMATION

Op Amp

Funetion Device Temperature Range Package

‘Single MC3HOTIR AP Piastie OP

Me3e0710, aD oto s700 S08

M3070, AU Coram DIP

icss071P, AP Plast DIP

Me320710, aD 40° 0 85:0 S08.

Me30071U, AU ceramic OF

MC3SO71U, AU “sew SC | Ceramic OF

Dual MC340727, AP "Plagie DIP

Me34a720, AD. owe | Ge

Mesao72u, AU Ceramic DIP

MCSB072P. AP Plage DIP

Me330720, AD 40" 0 485°C S08

MG23072U, AU. Gorame DIP

MC35072U, AU, ES OSC Ceram DIP

Guad MCRA07ER. AB Passio OP

Mesa0740,a0 otos70"0 ‘So-14

Mesab7al, AL ceramie DIP

MCSBO7EP, AP Piagie DIP

Me330740,A 40° 10 485°C Son

Mesaoral, AL ceramic DP

MCS507AL, AL Ew ET Ceramic OF

MC34071,2,4

MC35071,2,4

MC33071,2,4

P SUFFIX usurrx |

PLASTIC PACKAGE CERAMIC PACKAGE

CASE 628 CASE 693

Dsurrix

QB vustic Powace

‘CASE 751

(808)

PIN CONNECTIONS

cabal

fee Nc

d veo

wor (> Un ome

Vee 5 etn

(ge. Von

ae Yeo.

= Outpa 2

Some

{Boal ep View

Psurnx Lsurrnx

PLASTICPACKAGE CERAMIC PACKAGE

CASE 646 ‘CASE 622

DsuFFIK

Ff PLASTIC PACKAGE

“ CASE 7518

(0-14

PIN CONNECTIONS

up £3 oupa

wpa {4

Vec |

Bs |

Inputs2 {e |

apa

(Quad, fp View

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-284

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

MAXIMUM RATINGS.

{ Rating Symbol | Value | Unit

‘Supply Voltage (om Vee to Voc) Vs a

Input Diferential Votage Range VipR Note +

Input Voltage Range Vin Note t

‘Ouiput Short Ciruit Duration (Note 2) isc Tndetinte see

‘Operating Junction Temperature Ty *c

Ceramic Package +160

+150

Plastic Package

‘Storage Temperature Range Toto o

Ceramic Package 6510 +160

Plastic Package 6010 +150

NOTES: 1. Either or both input voltages should not exceed the magnitude of Veg or VEE.

2, Power dissipation must be considered to ensure maximum junction temperature (T,)

's not excoeded (see Figure 1),

Equivalent Circuit Schematic

(Each Ampitier)

= +++

cr

\ sy ow

a m3 gy i

bas { 3h

Mi ___| a8} LY os

routs

VeetGns

fst Nu

(39071, 4034071, 35071 ca)

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

2-285

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

ELECTRICAL CHARACTERISTICS |(Vog - +15 V, Vee «15 V, R= connected to ground, uniess otherwise noted

‘See [Note 3} or Ta = Tiow 19 Thigh!

Characteristics

3

Unit

Input Ofset Volage (Rg - 100.2. Voxs - 0 V, Vo =9¥)

Vog = +15 VEE = 15 V. Ta = 425°C

YGg = +80 V, Vee = OV. T= +25

Veo = #18, Vee ~-15V. Ta - Tiow 0 Thigh

mv

‘Average Temperature Goeticent of Input Ofset Voltage

Fig = 1022. Vous =0V. Vo =O,

TAs Tow Thigh

wre.

Ingut Bias Current (Voy = OV. Vo =O Vi

Ta = 2250

TA Mow 19 Thigh

Input Offset Current (Von

Ta= 125°C

TA> Tow 19 Thigh

V.¥o=0V)

mA

Input Common Mode Vottage Range

Tas 1250

Ta~ Tow 0 Thigh

Large Signal Voltage Gan Vo

Ta= 125°C

Ta= Tow to Thigh

S10 V, RL = 208)

aR

view

‘Output Voltage Swing (Vip = 1.0 Vp

Veo = +80. Vee OV. R= 2.0 ksn, Ta = «25°C

Vee = +15V, Vee ~—15 VR = 10K02 Tq = 25°C

Veg = 115 V, Veg =—18 V. RL = 2.0K

Fx = Tow to Thigh

Voc = 15.0, Veg =0V. A,

OK. Ty = 428°C

Vog = +18 V, Veg --15 A. = 10KD, TA = ¥25'

Vog= +18 Veg =—I5 RL = 2048

Ta= Tow '0 Thigh

Output Shot Cireut Curent (Vip = 10V. Vo =O,

Ta ~ 25°C)

Source

Sink

ss

‘Commen Made Rejacion

Fig = 100K. Vou = Vion, Ta = 25°C

Power Supply Rejection (Rg = 100 2),

VogVee = 8 5V-188 Vip -135 v-1a8¥

ia= 25°C

8

Power Supaly Current (Per Ampiier, No Loa)

Vo = +30V, Veg =0V, Vo= 225, 1q= 225°C

mA

Veo = +15V, Vee =-15¥, Vg 0. Ta= +250. = =

Veg = s18V, Veg 15. Vo OV. = =

Fa = Tow! Thigh

NOTES: 3. Tow = -S8°ClorMC35071.2.4./A

“80°C or MC33071.2, 4, 8

(°C for MO34071, 2.4.8

Thigh = +125°C for MC35071.2, 4A

385°C tor MO33071, 2.4.1

2 $70°Gtor Mosd071,2. 4,

MOTOROLA LINEARIINTERFACE ICs DEVICE DATA

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

AC ELECTRICAL CHARACTERISTICS (Vcc = +15 V, Veg =~15 V, RL = connected 1 ground Ta = +25°C, unless otherwise noted )

‘ASuttx Non- Sufix

Characteristics Symbol [min | Typ | Mex | win | Typ | Max | Unit

‘Slow Rate Vin=—10 Vio +10, = 20KR, OL = Vs

yas so | 0 | — | eo | w | —

eee =[3af—]"] 3%

Seting Time (10V Step, Ay 1.0) 8

o0.1% (1/2 S819) -Jul-}-ful-

Todor wii2tseof 128k) =]e2]=}ofe2i

Gain Bandwith Product = 100 kHz) cow | as | 4s | — [os | 45] — | me

Power Bandwidth aw | — |r| —|— | 0] — | we

(AV = #10, =2040, Vo = 20 Vpiy THD = 5.0%

Phase margin Des

RL 20e0 =|@)-|- |e] -

FL > 20K Oy «200 pF =|[o@[=[-]a|=

Gain Margin am rr

Pu = 2040 -fwel-}-jel]-

RL = 20K0, O1 = 00 pF = [4 [= [=| |=

Equivalent Input Noise Voltage - 32 = - 32, VINA

Age TOOT OMe | |

Equivalent input Noise Current eS Seas

TOKE

Diterontal put Resistance an | — [1% | — |— |] — | mo

Vom =0¥ |

Differonal input Capactance ee ee

Vows Ov

Total Harmonie Distorion mo [ — foo |— | — foe,—f« |

[AV = "10, RU = 2000, 20 VppsV0 $20 Vpp-t= 10H

Channel Separation (= 10 KH) = [ae [- [aff e

‘Oper Loep Output impedance (1= 1.0 Mia) wo | — | [-[-[al—-[e

Figure 1. Power Supply Configurations

area vest

b Yoo [ Voc

se >

> oe

ss F] _

a ep

Ne

Figure 2. Offset Null Circuit

Yoo

(Ofst nung range is approximately 80 nV wath a 10k

otortiometer (C9071, MC34071, MISO ot)

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-287

Pp, MAXIMUM POWER DISSIPATION (ni)

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

Figure 3. Maximum Power Dissipation versus

‘Temperature for Package Types

g

8

8 124 Pin Corie Pig

g

PAS 88 14 PnP Pag

8

g

So-8rg

&

°

5-40-20 0 20 0 a] OO

00 120 140 160

Th, AMBIENT TEMPERATURE C)

Figure 5. input Common Mode Voltage

Figure 4. input Offset Voltage versus

‘Temperature for Representative Units

—— |

Seale Cheat oat opt

a, AMBIENT TEMPERATURE (C)

Figure 6. Normalized Input Bias Current

Range versus Temperature = versus Temperature

le ¥ Tuan 2 8"

Veo VooNee= tsui-tsvewcevsey | &

a3

2 2,4,

Voc-18 3 5

Zio

Yoo-24 3 So

3 3

Veeoo1 5 Bos

\e ge I

eg 50s = ew eS US a se

Ty AMBENT TEMPERATURE (0) TH AMBLENT TEMPERATURE 0)

Figure 7. Normalized Input Blas Current versus Figure 8. Spit Supply Output Voltage

Input Common Mode Voltage Swing versus Supply Voltage

gu - % +

I ed

2 { BP ions:

Z rH Zo

S 2 2

2 N 3° Aion

3 19) 2 x

3 2»

ae a 5

a 2

2 2

a rr) 40° 80 2 0 50 10 18 2 B

Vig. NPUT COMMON MODE VOLTAGE (¥)

oo: Nee}, SUPPLY VOLTAGE ()

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-288

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

Figure 8. Split Supply Output Saturation Figure 10. Single Supply Cutput Saturation

versus Load Current versus Load Resistance fo Ground

X “

on FT vcover=s0vi-sovwrvizv | = ‘| Iw

4 Voy tesa 18

5 2 voc-20]

g g

é Brose

5 5

2 =

3 3

ve

3 + i

Vee g 5 10 15 ED 0 1.0K 10K 100k

i, Loan CURRENT 4 LOAD RESISTANCE TO GROUND (0

Figure 11. Single Supply Output Saturation Figure 12. Output Short Circuit Current

versus Load Resistance to Voc ‘versus Temperature

. ©

8 |

z z°

3 5

: ©

@ 2

= 3a

§ 5

5 En

3 to 20

2 OM iH 7

1% 108 10K 100k 2

A LOAD RESISTANCE TO Vee) ‘Ty AMBIENT TEMPERATURE ()

Figure 14. Output Voltage Swing

Figure 13, Output Impedance versus Frequency versus Frequency

= ie

¢ Fa

3 z

: 5

z e

° °

tor 10k 100 ion 10m ok 10k a0n 0k «ORO aM

{FREQUENCY 1 FREQUENCY (a

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA.

2-289

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

Figure 15. Output Distortion versus Frequency

0 ~

a y= 1000

z

Z 03

Bw

é

Sas

2

0

"0 100 19% tok Took

[LEREQUENCY (a)

Figure 17. Open-Loop Voltage Gain

versus Temperature

te

= _

Zin

8 ove st0

Ee

8 4

8 xt —

5 wo +

Sat ae a) a

‘Tay AMBIENT TEMPERATURE (C)

Figure 19. Open-Loop Voltage Gain and

Phase versus Frequency

Figure 16. Output Distortion versus.

Output Voltage Swing

=

g

THD, OUTPUT DISTORTION (X)

° 40 80 1 16 2

Yo, OUTPUT VOLTAGE SWING Vp)

Figure 18. Open-Loop Voltage Gain and

Phase versus Frequency

&

&

‘Ayot OPEN-LOOP VOLTAGE GAIN (8)

a8

'§ EXCESS PHASE (DEGREES)

a

100 10%

{FREQUENCY (He)

tok 100k 10M 10M 100M

Figure 20. Normalized Gain Bandwidth

Produt versus Temperature

g i

3 ag i

s Bet NS

5 z 19]

= 8 oss

; H *, el i 7

Taszse 3 IN

aeons z™

‘FREQUENCY (iz)

“SO SOHCOSSSCOOSCS

‘Tp, AMBIENT TEMPERATURE (C)

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

2-290

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

Figure 21, Percent Overshoot versus Figure 22. Phase Margin versus

‘Loed Capacitance ‘Load Capacitance

| T TTT

geil

; Be

& 3 4] 7 t

é 3

5 »

: 3

# =”

10

5 : |

‘0 100 10k ‘ok 10 100 19k 0k

LOAD CAPAETANCE 9) CL LOAD CAPACITANCE GF)

Figure 23. Gain Margin verous Load Capecitance Figure 24, Phase Margin veraus Temperature

“ r

8 g 1096

Zu Be = oF |

$0 5

z 2° 7

geo

0 i,

2 rt 2

: [

‘0 190 19k 10k S80 8 © 7% wm 1%

CL LOAD CAPACITANCE (9 “Ty AMENT TEMPERATURE (6)

Figure 26, Phase Margin and Gain Margin

Figure 25. Gain Margin versus Temperature ‘Yersus Differential Source Resistance

%s—— 2 n

Veo= #15

Os 10 F Gain ted

a m 7

Tt z

i Ou = 100 pF i ‘a i

3 0

‘ eso 3

7 : ri aE

4 we

re er) 100k kk

Ta, AMBIENT TEMPERATURE (°C) x DIFFERENTIAL SOURCE RESISTANCE (2)

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-291

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

Figure 27. Normalized Siew Rate

versus Temperature Figure 28. Output Settling Time

g

.3,Vo . OUTPUT VOLTAGE SWING FROM OV (¥)

oa ee Cn Fe

Ty, AMBIENT TEMPERATURE (G) 1g, SETTUNG TIME (us)

Figure 29, Small Signal Transient Response Figure 30. Large Signal Transient Reponse

soviow

\ V0

Figure 31. Common Mode Rejection Figure 32. Power Supply Rejection

Versus Frequency ‘versus Frequency

= ‘0

g eee 7

g B tbvoc=¥15¥

# Zw

3 :

34 - 20 \—

3 soot] 2>-0 aio 3

8 a 7 \ Bn

ef fcumet010g (MO soy & PsA

Tver = +15)

° 0

01 10 19 «100 10k 10k 100k 10M 10M 1 10-10 100 10k 10k 100k 10M 10M

{FREQUENCY (tz) {FREQUENCY (2)

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-292

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

Figure 34. Power Supply Rejection

Figure 33, Supply Current versus Supply Voltage versus Temperature:

90) 7 a 7

I [al wees ve

Zao Asie) | 3 Vee =-18V

5 = a |

Eo ee — 2 Fra og = 115

3 ae 2s +

E60 a

2 Ta 25°C ie

Bsa : Bn

g

wo 6s

. o 9 8 =» @ ‘S80 8 w

Vice Nee SUPPLY VOLAGE 1) TA AMBENT TEMPERATURE FO)

Figure 95. Channel Separation versus Frequency

Figure 36. Input Noise versus Frequency

wy _» 2

gi Be all

g z 4

5 208

g | 3 | a

: Ze uk

3° 80 2

: ; 2g

3 iT y

3 7 i » Cure os

a 20 oe

0 a5 | l, =

0 8) m1 mm 0 tok kk

{REQUENCY oe {FREQUENCY wt

APPLICATIONS INFORMATION

CIRCUIT DESCRIPTION/PERFORMANCE FEATURES

[though the bandwidth slew rat, and setting time ofthe maximum rating table. In practice, although not

MC34071 amplifier series are similar to op amp products

utiizing JFET input devices, these amplifiers offer other

additional distinct advantages as a result ofthe PNP transistor

differentia input stage and an all NPN transistor output stage.

‘Since the input common mode voltage range of this input

stage includes the VEE potential, single supply operation is

feasible to as low as 3.0 V with the common mode input

voltage at ground potential.

‘The input stage also allows differential input voltages up to

+444 V, provided the maximum input voltage range is not

exceeded. Specifically, the input voltages must range

between VeE and Vcc supply voltages as shown by the

‘recommended, the input voltagescan exceedthe Vcc vollage

by approximately 3.0 V and decrease below the Vee voltage

by 0.3 V without causing product damage, although output

phase reversal may occur. It is also possible to source up to

Approximately 5.0 mA of current from VEE through either

inputs clamping diode without damage or latching, although

phase reversal may again occur.

If one or both inputs exceed the upper common mode

voltage limit the amplifier outputis readily predictable andmay

be in a low or high state depending on the existing input

bias conditions.

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

2-293

MC34071, 34072, 34074/MC35071,

Since the input capacitance associated with the small

geometry input device is substantially lower (2.5 pF) than the

typical JFET input gate capacitance (5.0 pF), better requency

response for a given input source resistance can be achieved

using the MC34071 series of amplifiers. This performance

‘eature becomes evident, for example, in fast settling D:to-A

Ccurrentto voltage conversion applications where the teedback

resistance can form an input pole with the input capacitance

Of the op amp. This input pole creates a 2nd order system with

the single pole op amp and is therefore detrimental to its

settling time. In this context, lower input capacitance is

desirable especially for higher values of feedback resistances

(lower current DACs). This input pole can be compensated for

by creating a feedback zero with a capacitance across the

feedback resistance, it necessary, to reduce overshoot. For

2.0k@.of feedback resistance, the MC34071 series can settle

to within 1/2 LSB of 8 bits in 1.0 us, and within 1/2 LSB of

12-bits in 2.2 us for a 10 V step. In a inverting unity gain fast,

settling configuration, the symmetrical slew rate is 213 Vius,

In the classic noninverting unity gain configuration the output

Positive slew rateis +10 Vins, and the corresponding negative

slew rate will exceed the positive slew rate as a function of the

fall time of the input waveform,

‘Since the bipolar input device matching characteristics are

‘superior to that of JFETs, a low untrimmed maximum offset

voltage of 3.0 mV prime and 5.0 mV downgrade can be

economically offered with high frequency performance

Characteristics. This combination is ideal for low cost

Precision, high speed quad op amp applications.

‘The all NPN output stage, shown in its basic form on the

equivalent circuit schematic, offers unique advantages over

the more conventional NPN/PNP transistor Class AB

‘output stage. A 10 kat load resistance can swing within 1.0 V

Of the positive rail (Voc). and within 0.3 V of the negative

‘ail (VEE), providing a 28.7 Vp.p swing from +15 V supplies.

This large output swing becomes most noticeable at lower

supply voltages,

The positive swing is limited by the saturation voltage of the

current source transistor Q7, and Vpe of the NPN pull up

transistor Q47, and the voltage drop associated with the short

circuit resistance, Ri. The negative swing is limited by the

saturation voltage of the pull-down transistor Qg, the voltage

drop IL Ag, and the voltage drop associated with resistance Fi.

where IL is the sink load current. For small valued sink

currents, the above voltage drops are negligible, allowing the

negative swing voltage to approach within millvots of VEE

For large valued sink currents (>5.0 mA), diode D3 clamps the

voltage across Rg, thus limiting the negative swing to the

saturation voltage of Q4g, plus the forward diode drop of D3

(Vee 41.0 V). Thus for a given supply voltage.

unprecedented peak-to-peak output voltage swings possible

a indicated by the output swing specifications,

Itthe load resistance isreferencedto Vcc instead of ground

for single supply applications, the maximum possible output

‘swing can be achieved for a given supply voltage. For ight

load currents, the load resistance will pull the output to Voc.

35072, 35074/MC33071, 33072, 33074

uring the positive swing and the output will pull the load

resistance near ground during the negative swing. The load

resistance value should be much less than that of the

feedback resistance to maximize pull up capability,

Because the PNP output emitter-follower transistor has

been eliminated, the MC34071 series offers a20 mA minimum

current sink capabilty, typically to an output vollage of (VEE

+1.8 V). In single supply applications the output can directly

Source or sink base current from a common emitter NPN

transistor for fast high current switching applications,

In adcition, the all NPN transistor output stage is inherently

fast, contributing tothe bipolar amplifiers high gain bandwidth

Product and fast settling capability. The associated high

‘requency low output impedance (30 2 typ @ 1.0 MHz) allows

capacitive drive capabilty from 0 pF to 10,000 pF without

‘oscillation in the unity closed-loop gain configuration. The 60°

phase margin and 12 dB gain margin as well as the general

{gain and phase characteristics are Vitually independent ofthe

Source/sink output swing conditions. This allows easier

system phase compensation, since output swing will not

bbe a phase consideration. The high frequency characteristics,

of the MC34071 series also allow excellent high

‘requency active fier capability, especially for low voltage

single supply applications.

‘Although the single supply specifications is defined at 50 V,

these amplifiers are functional to 3.0 V @ 25°C although slight

changes in parametrics such as bandwidth, slew rate, and DC.

gain may occur.

| power to this integrated circuitis applied in reverse polarity

rif the IC is installed backwards in a socket, large unlimited

current surges will occur through the device that may result in

device destruction.

Special static precautions are not necessary for these

bipolar ampiiiers since there are no MOS transistors on

the die

As usual with most high frequency amplifiers, proper lead

dress, component placement, and PC board layout should

be exercised for optimum frequency performance. For

‘example, long unshielded input or output leads may result in

unwanted input-output coupling. In arder to preserve the

relatively low input capacitance associated with these

amplifiers, resistors connected to the inputs should be

immediately adjacent to the input pin to minimize additional

stray input capacitance. This not only minimizes the input pole

for optimum frequency response, but also. minimizes

extraneous “pick up” at this node. Supply decoupling with

‘adequate capacitance immediately adjacent to the supply pin

is also important, particularly aver temperature, since many

types of decoupling capacitors exhibit great impedance

changes over temperature.

The output of any one amplifier is current limited and thus

protected from a direct short to ground. However, under such

Conditions, itis important not to allow the device to exceed the

‘maximum junction temperature rating. Typically for +15 V

supplies, any one output can be shorted continuously to

‘ground without exceeding the maximum temperature rating,

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

2-294

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

TYPICAL SINGLE SUPPLY APPLICATIONS Voc = 5.0V

Figure 37. AC Coupled Noninverting Amplifer Figure 38. AC Coupled Inverting Amplifier

Yoo

sam

‘y= OE (3.08) = 480 Ke

Figure 39. DC Coupled inverting Ampliter

.

ot L wosr osareex

7

= oy

1 Ll Iw ~=t0

~ a Figure 42. Active Bandpass Filter

Figure 41. Active High-Q Notch Filter

c 3

cee 22 cart

Vin202 Vee wesart Vigo {+ -

vo 1k c Yo

Given tp = Centr Frequency

‘Ag = Gan at Conte Frequeny

one (Choose Value yO, Ao,

“Then

1

‘o> anc Forless han 10% ene rom operatonal apie

200200 Oslo

om one ao

‘Where and GEN are expresso in He

(BW = 45 NH2 Hp,

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-295

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

Figure 43. Low Voltage Fast D/A Converter

(2A) Lado Ne

wok

Seting Tare

Tus fs, 12 LSB)

Figure 45. LED Driver

$ Vee

Qa

YD Tver

Vn

Menor i

SMe 3

Figure 47. AC/DC Ground Current Monitor

tons

oO

tent

+

Ground Cus 3

Souoruisw |

; ge

AL

Vor toads 1+

ForVp201¥

Fa

01 (-3048) «BW | GPS )

Yo

Figure 44, High Speed Low Voltage Comparator

Min

Neg

—_ a

|

° ' I

1 — ll oaus

of 4 age

is) 1 ass

wu the,

| Delay

eee

Yoo

5 5

5

a _

cota: i ee

CoS C

by 1

(A)PNP- [B)NPN

Figure 48, Photovoltaic Cell Amplifier

%

=a ||

ea St.

ce

wee

ves

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-298

MC34071, 34072, 34074/MC35071,

Figure 49, Low Input Voltage Comparator

‘with Hysteresis

Yo Hystrode

i a

i

oe wosior | voy rT

BAL

Vou Ley

g in

: Yiu! Voit

z Vee Meet

Mink rung OL Vet

a

Vowt= ape WOH ed et

at

Yas aaa VOH-VOU

Figure 51. High Imput Impedance

Differential Amplifier

Rt Fe

weMcsor2

20

2 © ota

BE 2 rca to CHAR)

(68) (vee)

(+) (ew

Ra

«

For(V22V1j,.Voo

Figure 53. Low Voltage Peak Detector

Ya mosori

Yo Vin 8)

35072, 35074/MC33071, 33072, 33074

Figure 50. High Compliance Voltage to

‘Sink Current Converter

|. | owe

Va osaort v

Figure 52. Bridge Current Amplifier

Met

° Ae

r, Ste

Re andy? ® :

aR Ar

Vo= Vet sng

aRcek we =

ReooR Wo>0™M

Figure §4. High Frequency Pulse

‘Width Modulation

eee F

f Passe wn =

tee YP * conta Group

BQH

ose. Comparator

High Curent

‘Outpt

MOTOROLA LINEAR/INTERFACE ICs DEVICE DATA

2-297

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

GENERAL ADDITIONAL APPLICATIONS INFORMATION Vs = +15.0 V

Figure 55. Second Order Low-Pass Active Filter Figure 56. Second Order High-Pass Active Fiter

a

Se e a

34m

t—~ 6 T to oseort

At 3 56K Cad -

Py i ch

> se 4, te 100H

- te

eli S“osan “Kgs 10 = oF yas,

ott ty My ie feos

1 Lhe creme ggcr Tne ts

Thn:Ct=26 tt) cat

5 ® i Fe io

a c

ossort

V0

Yo _ fe 7 Rt

vrempnane 6-100 Te mn OM C300@)-caW RE

40 12158 (6-88) ne

conpensand {Soot a

“et 10 12158 (128)

*Optonal Corpensaton SR=13Vis

Figure 59. Basic Noninverting Amplifie

@ 60. Unity Gain Butter (Ay = +1.0)

osaont

vucscor

Ygo—— +

aio

Le |

Vn

Yo /,, we YO=20Vpp

1 il wee) L SR=10Vhi8

W348) -caw|

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-298

MC34071, 34072, 34074/MC35071, 35072, 35074/MC33071, 33072, 33074

Figure 61. High Impedance Differential Amplifier

wes

eso

RB

ee S

i Fe ‘J

eagle:

LotR eRe = 12k Ro

o—) ge Trecaysa0 | N= [142 RE

BW = 15 MHz

Figure 62. Dual Voltage Doubler

MOTOROLA LINEARVINTERFACE ICs DEVICE DATA

2-299

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Manual de Servicio Electrolux DW50X PDFDocument104 pagesManual de Servicio Electrolux DW50X PDFAntonio Rodriguez75% (20)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Whirlpool+No+Frost+36!40!44 48Document46 pagesWhirlpool+No+Frost+36!40!44 48Wendy Alemán88% (33)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Manual DF34 DF35 DF36 DF37 DF38A DF38X DFW35 Rev9Document42 pagesManual DF34 DF35 DF36 DF37 DF38A DF38X DFW35 Rev9jesegovia88416167% (12)

- Manual de Servicio Whirpool Arb250 PDFDocument13 pagesManual de Servicio Whirpool Arb250 PDFandrespioli100% (2)

- Manual de Servicio WHIRLPOOL - ARB240Document15 pagesManual de Servicio WHIRLPOOL - ARB240Carlos Posada0% (1)

- P6ke6v8 (C) A - P6ke440 (C) ADocument3 pagesP6ke6v8 (C) A - P6ke440 (C) ACarlos PosadaNo ratings yet

- MCP3204 MCP3208 PDFDocument20 pagesMCP3204 MCP3208 PDFCarlos PosadaNo ratings yet

- Icl7135c - TLC7135CDocument11 pagesIcl7135c - TLC7135CCarlos PosadaNo ratings yet

- TDA1387 PhilipsDocument16 pagesTDA1387 PhilipsCarlos PosadaNo ratings yet

- CS4338 PDFDocument26 pagesCS4338 PDFCarlos PosadaNo ratings yet

- Neveradfw45ydff44modulo2 PDFDocument12 pagesNeveradfw45ydff44modulo2 PDFDavid LovatoNo ratings yet

- Manual de Heladera Whirlpool ARB-210Document12 pagesManual de Heladera Whirlpool ARB-210Cristian Perez100% (1)

- Ba10324 Rohm PDFDocument5 pagesBa10324 Rohm PDFCarlos PosadaNo ratings yet

- MC 33174Document12 pagesMC 33174Carlos PosadaNo ratings yet

- NE5532 ON Semiconductor PDFDocument10 pagesNE5532 ON Semiconductor PDFCarlos PosadaNo ratings yet

- 2x30w Amplificator Cu TdaDocument7 pages2x30w Amplificator Cu Tdasorin_E2003No ratings yet