Professional Documents

Culture Documents

74373

74373

Uploaded by

James Clerk MaxwellCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74373

74373

Uploaded by

James Clerk MaxwellCopyright:

Available Formats

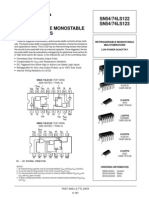

SN54/74LS373

OCTAL TRANSPARENT LATCH SN54/74LS374

WITH 3-STATE OUTPUTS;

OCTAL D-TYPE FLIP-FLOP

WITH 3-STATE OUTPUT OCTAL TRANSPARENT LATCH

WITH 3-STATE OUTPUTS;

OCTAL D-TYPE FLIP-FLOP

The SN54 / 74LS373 consists of eight latches with 3-state outputs for bus

organized system applications. The flip-flops appear transparent to the data WITH 3-STATE OUTPUT

(data changes asynchronously) when Latch Enable (LE) is HIGH. When LE is LOW POWER SCHOTTKY

LOW, the data that meets the setup times is latched. Data appears on the bus

when the Output Enable (OE) is LOW. When OE is HIGH the bus output is in

the high impedance state.

The SN54 / 74LS374 is a high-speed, low-power Octal D-type Flip-Flop fea-

turing separate D-type inputs for each flip-flop and 3-state outputs for bus ori-

J SUFFIX

ented applications. A buffered Clock (CP) and Output Enable (OE) is common CERAMIC

to all flip-flops. The SN54 / 74LS374 is manufactured using advanced Low CASE 732-03

Power Schottky technology and is compatible with all Motorola TTL families. 20

• Eight Latches in a Single Package 1

• 3-State Outputs for Bus Interfacing

• Hysteresis on Latch Enable N SUFFIX

• Edge-Triggered D-Type Inputs PLASTIC

• Buffered Positive Edge-Triggered Clock 20

CASE 738-03

• Hysteresis on Clock Input to Improve Noise Margin 1

• Input Clamp Diodes Limit High Speed Termination Effects

DW SUFFIX

PIN NAMES LOADING (Note a) SOIC

20

HIGH LOW CASE 751D-03

1

D0 – D7 Data Inputs 0.5 U.L. 0.25 U.L.

LE Latch Enable (Active HIGH) Input 0.5 U.L. 0.25 U.L.

CP Clock (Active HIGH going edge) Input 0.5 U.L. 0.25 U.L.

OE Output Enable (Active LOW) Input 0.5 U.L. 0.25 U.L. ORDERING INFORMATION

O0 – O7 Outputs (Note b) 65 (25) U.L. 15 (7.5) U.L.

SN54LSXXXJ Ceramic

SN74LSXXXN Plastic

NOTES:

SN74LSXXXDW SOIC

a) 1 TTL Units Load (U.L.) = 40 µA HIGH/1.6 mA LOW.

b) The Output LOW drive factor is 7.5 U.L. for Military (54) and 25 U.L. for Commercial

(74) Temperature Ranges. The Output HIGH drive factor is 25 U.L. for Military (54) and

65 U.L. for Commercial (74) Temperature Ranges.

CONNECTION DIAGRAM DIP (TOP VIEW)

SN54 / 74LS373 SN54 / 74LS374

VCC O7 D7 D6 O6 O5 D5 D4 O4 LE VCC O7 D7 D6 O6 O5 D5 D4 O4 CP

20 19 18 17 16 15 14 13 12 11 20 19 18 17 16 15 14 13 12 11

1 2 3 4 5 6 7 8 9 10 NOTE: 1 2 3 4 5 6 7 8 9 10

OE O0 D0 D1 O1 O2 D2 D3 O3 GND The Flatpak version OE O0 D0 D1 O1 O2 D2 D3 O3 GND

has the same pinouts

(Connection Diagram) as

the Dual In-Line Package.

FAST AND LS TTL DATA

5-1

SN54/74LS373 • SN54/74LS374

TRUTH TABLE

LS373 LS374

Dn LE OE On Dn LE OE On

H H L H H L H

L H L L L L L

X L L Q0 X X H Z*

X X H Z*

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

* Note: Contents of flip-flops unaffected by the state of the Output Enable input (OE).

LOGIC DIAGRAMS

SN54LS / 74LS373 3 4 7 8 13 14 17 18

VCC = PIN 20

D0 D1 D2 D3 D4 D5 D6 D7 GND = PIN 10

= PIN NUMBERS

D D D D D D D D

LATCH Q Q Q Q Q Q Q Q

ENABLE G G G G G G G G

11

LE

OE

1

O0 O1 O2 O3 O4 O5 O6 O7

2 5 6 9 12 15 16 19

SN54LS / 74LS374

3 4 7 8 13 14 17 18

11 D0 D1 D2 D3 D4 D5 D6 D7

CP

CP D CP D CP D CP D CP D CP D CP D CP D

Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q

OE

1 O0 O1 O2 O3 O4 O5 O6 O7

2 5 6 9 12 15 16 19

GUARANTEED OPERATING RANGES

Symbol Parameter Min Typ Max Unit

VCC Supply Voltage 54 4.5 5.0 5.5 V

74 4.75 5.0 5.25

TA Operating Ambient Temperature Range 54 – 55 25 125 °C

74 0 25 70

IOH Output Current — High 54 – 1.0 mA

74 – 2.6

IOL Output Current — Low 54 12 mA

74 24

FAST AND LS TTL DATA

5-2

SN54/74LS373 • SN54/74LS374

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

Limits

S b l

Symbol P

Parameter Min Typ Max U i

Unit T

Test C

Conditions

di i

Guaranteed Input HIGH Voltage for

VIH Input HIGH Voltage 2.0 V

All Inputs

54 0.7 Guaranteed Input

p LOW Voltage

g for

VIL Input LOW Voltage V

74 0.8 All Inputs

VIK Input Clamp Diode Voltage – 0.65 – 1.5 V VCC = MIN, IIN = – 18 mA

54 2.4 3.4 V VCC = MIN,, IOH = MAX,, VIN = VIH

VOH Output HIGH Voltage

74 2.4 3.1 V or VIL per Truth Table

54, 74 0.25 0.4 V IOL = 12 mA VCC = VCC MIN,

VOL Output LOW Voltage VIN = VIL or VIH

74 0.35 0.5 V IOL = 24 mA per Truth Table

IOZH Output Off Current HIGH 20 µA VCC = MAX, VOUT = 2.7 V

IOZL Output Off Current LOW – 20 µA VCC = MAX, VOUT = 0.4 V

20 µA VCC = MAX, VIN = 2.7 V

IIH Input HIGH Current

0.1 mA VCC = MAX, VIN = 7.0 V

IIL Input LOW Current – 0.4 mA VCC = MAX, VIN = 0.4 V

IOS Short Circuit Current (Note 1) – 30 – 130 mA VCC = MAX

ICC Power Supply Current 40 mA VCC = MAX

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

AC CHARACTERISTICS (TA = 25°C, VCC = 5.0 V)

Limits

LS373 LS374

S b l

Symbol P

Parameter Min Typ Max Min Typ Max U i

Unit T

Test C

Conditions

di i

fMAX Maximum Clock Frequency 35 50 MHz

tPLH Propagation Delay, 12 18

ns

tPHL Data to Output 12 18

CL = 45 pF,

pF

F

tPLH Clock or Enable 20 30 15 28 RL = 667 Ω

ns

tPHL to Output 18 30 19 28

tPZH 15 28 20 28

Output Enable Time ns

tPZL 25 36 21 28

tPHZ 12 20 12 20

Output Disable Time ns CL = 5.0 pF

tPLZ 15 25 15 25

AC SETUP REQUIREMENTS (TA = 25°C, VCC = 5.0 V)

Limits

LS373 LS374

Symbol

S b l Parameter

P Min Max Min Max Unit

U i

tW Clock Pulse Width 15 15 ns

ts Setup Time 5.0 20 ns

th Hold Time 20 0 ns

DEFINITION OF TERMS

SETUP TIME (ts) — is defined as the minimum time required HOLD TIME (th) — is defined as the minimum time following

for the correct logic level to be present at the logic input prior to the LE transition from HIGH-to-LOW that the logic level must

LE transition from HIGH-to-LOW in order to be recognized and be maintained at the input in order to ensure continued

transferred to the outputs. recognition.

FAST AND LS TTL DATA

5-3

SN54/74LS373

AC WAVEFORMS

tW tW

LE 1.3 V

ts th

Dn

tPLH tPHL

OUTPUT

Figure 1

OE 1.3 V 1.3 V OE 1.3 V 1.3 V

tPZL tPLZ tPZH tPHZ

VOH

VOUT 1.3 V 1.3 V 1.3 V

VOUT 1.3 V

VOL 0.5 V

0.5 V

Figure 2 Figure 3

AC LOAD CIRCUIT

VCC

SWITCH POSITIONS

RL

SYMBOL SW1 SW2

tPZH Open Closed

SW1

tPZL Closed Open

tPLZ Closed Closed

TO OUTPUT

UNDER TEST tPHZ Closed Closed

5.0 kΩ

CL* SW2

* Includes Jig and Probe Capacitance.

Figure 4

FAST AND LS TTL DATA

5-4

SN54/74LS374

AC WAVEFORMS

tWH tWL

OE 1.3 V 1.3 V

CP 1.3 V 1.3 V 1.3 V

ts th tPZL tPLZ

Dn 1.3 V VOUT 1.3 V ≈ 1.3 V

VOL

tPLH tPHL

0.5 V

OUTPUT 1.3 V 1.3 V Figure 6

Figure 5

OE 1.3 V 1.3 V

tPZH tPHZ

≥ VOH

VOUT 1.3 V ≈ 1.3 V

0.5 V

Figure 7

AC LOAD CIRCUIT

VCC

SWITCH POSITIONS

RL

SYMBOL SW1 SW2

tPZH Open Closed

SW1

tPZL Closed Open

tPLZ Closed Closed

TO OUTPUT

UNDER TEST tPHZ Closed Closed

5.0 kΩ

CL* SW2

* Includes Jig and Probe Capacitance.

Figure 8

FAST AND LS TTL DATA

5-5

You might also like

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- PNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGFrom EverandPNEUMATICS AND AIR CIRCUITS UNDERSTANDING THE CASCADE VALVE AND PLC UNDERSTANDINGNo ratings yet

- 7 Segment DisplayDocument6 pages7 Segment DisplayFelipe Dias100% (1)

- 74LS175Document3 pages74LS175Yesenia RojoNo ratings yet

- 74LS75 PDFDocument4 pages74LS75 PDFDeni KhanNo ratings yet

- 74LS174Document3 pages74LS174Raul Sedano Lau100% (1)

- 374Document13 pages374Brzata PticaNo ratings yet

- 74164Document4 pages74164milkyway69No ratings yet

- DatasheetDocument4 pagesDatasheetMeetha ShenoyNo ratings yet

- 74LS151 Multiplexer Truth TableDocument3 pages74LS151 Multiplexer Truth TableJack GonNo ratings yet

- 74 Ls 164Document4 pages74 Ls 164Cesar GutierrezNo ratings yet

- 74LS73Document5 pages74LS73Cristin BarnesNo ratings yet

- 74LS74 PDFDocument3 pages74LS74 PDFDeni KhanNo ratings yet

- 9-Bit Odd/Even Parity Generators/Checkers SN54/74LS280: Low Power SchottkyDocument2 pages9-Bit Odd/Even Parity Generators/Checkers SN54/74LS280: Low Power Schottkydistrict19No ratings yet

- SN74LS164NDocument5 pagesSN74LS164NAlex ReyesNo ratings yet

- 74HC573 Octal LatchDocument13 pages74HC573 Octal LatchWonzNo ratings yet

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601No ratings yet

- SN74LS173NDocument7 pagesSN74LS173NMozz WildeNo ratings yet

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DNo ratings yet

- MC74AC253, MC74ACT253 Dual 4 Input Multiplexer With 3 State OutputsDocument11 pagesMC74AC253, MC74ACT253 Dual 4 Input Multiplexer With 3 State OutputsMateus RossiniNo ratings yet

- SN54/74LS240 SN54/74LS241 SN54/74LS244: Low Power SchottkyDocument10 pagesSN54/74LS240 SN54/74LS241 SN54/74LS244: Low Power SchottkyDouglas CorderoNo ratings yet

- CBT3257AD I-St Mixer Elecraft 3Document16 pagesCBT3257AD I-St Mixer Elecraft 3verd leonardNo ratings yet

- Quad D Flip-Flop SN54/74LS175: Low Power SchottkyDocument5 pagesQuad D Flip-Flop SN54/74LS175: Low Power SchottkyEddy DiazNo ratings yet

- 4 X 4 Register File Open-Collector SN54/74LS170: Low Power SchottkyDocument4 pages4 X 4 Register File Open-Collector SN54/74LS170: Low Power Schottkydistrict19No ratings yet

- 8-Bit Shift/Storage Register With 3-State Outputs SN54/74LS299Document5 pages8-Bit Shift/Storage Register With 3-State Outputs SN54/74LS299Giapy Phuc TranNo ratings yet

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoNo ratings yet

- 74138Document6 pages74138Pedro SousaNo ratings yet

- 74 Ls 175Document8 pages74 Ls 175AndrescronqueNo ratings yet

- 1-Of-10 Decoder/Driver Open-Collector SN54/74LS145: Low Power SchottkyDocument3 pages1-Of-10 Decoder/Driver Open-Collector SN54/74LS145: Low Power SchottkyShyamsundar JenaNo ratings yet

- SN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsDocument7 pagesSN54HC573A, SN74HC573A Octal Transparent D-Type Latches With 3-State OutputsMadhukar PuliNo ratings yet

- Octal Buffer/Line Driver With 3-State Outputs SN54/74LS540 SN54/74LS541Document3 pagesOctal Buffer/Line Driver With 3-State Outputs SN54/74LS540 SN54/74LS541AalfonSoo RT KruspeNo ratings yet

- 74LS76 FF JK Con Set y ClearDocument2 pages74LS76 FF JK Con Set y ClearZoy HavelNo ratings yet

- Presettable Bcd/Decade Up/Down Counter Presettable 4-Bit Binary Up/Down Counter SN54/74LS192 SN54/74LS193Document9 pagesPresettable Bcd/Decade Up/Down Counter Presettable 4-Bit Binary Up/Down Counter SN54/74LS192 SN54/74LS193EDERTREVISANNo ratings yet

- 74574Document6 pages74574Alexandre S. CorrêaNo ratings yet

- D D D D: SN54ACT573, SN74ACT573 Octal D-Type Transparent Latches With 3-State OutputsDocument16 pagesD D D D: SN54ACT573, SN74ACT573 Octal D-Type Transparent Latches With 3-State OutputsĐạt Hoàng TrầnNo ratings yet

- 8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsDocument14 pages8-Bit Shift Register With Input Storage Registers (3-State) : Integrated CircuitsskiziltoprakNo ratings yet

- 74HC4094 74HCT4094: 1. General DescriptionDocument23 pages74HC4094 74HCT4094: 1. General DescriptionakbarparlindunganNo ratings yet

- 74HC373Document13 pages74HC373hugodjacobNo ratings yet

- IDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: DescriptionDocument7 pagesIDT54/74FCT373T/AT/CT Fast Cmos Octal Transparent Latch: Features: Descriptiongreentea601No ratings yet

- 74 Ls 121Document10 pages74 Ls 121krlossnNo ratings yet

- DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument6 pagesDM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputssoulchordsNo ratings yet

- 4 BIT D LatchDocument5 pages4 BIT D LatchBront PaulNo ratings yet

- 74LVC14APWDHDocument11 pages74LVC14APWDHIlie GrecuNo ratings yet

- 74LS14Document4 pages74LS14Daniel KösterNo ratings yet