Professional Documents

Culture Documents

Digital Logic Circuit Analysis and Design PDF

Digital Logic Circuit Analysis and Design PDF

Uploaded by

Angélica Trochez0 ratings0% found this document useful (0 votes)

597 views866 pagesOriginal Title

Digital Logic Circuit Analysis and Design.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

597 views866 pagesDigital Logic Circuit Analysis and Design PDF

Digital Logic Circuit Analysis and Design PDF

Uploaded by

Angélica TrochezCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 866

DIGITAL LOGIC

CIRCUIT ANALYSIS

& DESIGN

Victor P. NELSON

H. Troy NAGLE

J. David IRWIN

BILL D. CARROLL

DIGITAL LOGIC

CIRCUIT ANALYSIS

MD) IS) (GIN)

Victor P. NELSON * H. Troy NAGLE * J. Davi IRWIN * BILL D. CARROLL

ge eee ee ea eRe

reader with a clear, comprehensive, and state-of-the-art view of digital design theory and practice.

Features

‘© Covers topies authoritatively and in-depth but with a minimum of formal mathematics

‘= Places a strong emphasis on developing and using systematic problem-solving and design approaches

Pre ra ne a ec ec en Re eee EU

Sree eet ct

‘= Presents a thorough discussion of CAD issues and practices in an integrated manner, allowing CAD

methods to be applied to the correlative concepts and design principles

* Contains two comprehensive chapters describing programmable logic devices and their applications in

Omari ie ReneS

See eee eee ene nae

* Offers good coverage of hierarchical modular design and standard digital circuit modules

PS

Victor P. Nelson is a professor of Electrical Engineering at Auburn University. Dr. Nelson conduets his

research in the areas of computer architecture and design, fault-tolerant computing, multiprocessor

system architectures, microprocessor applications, and CAD tools for VLSI design. He is the author of

three textbooks and the IEEE Press tutorial, Fault Tolerant Computing: An Introduction.

H. Troy Nagle 1s a protessor of lectrical Engineering at North Carolina State University and Research

Professor of Biomedical Engineering at The University of North Carolina at Chapel Hill. Dr. Nagle is

coauthor of the best selling textbook, Digital Control System Analysis and Design, aud currently conducts

Pere ee aa ee ec eer ec ET eC

ene ere ener esa es ees)

PE ae cen oat Secor eee eee

‘The wide range of Dr. Irwin’s professional activities include active membership in the IEEE Computer

Society and Editor of the IEEE Transactions on Industrial Electronics. Dr. Invin is the author of more

than fifty publications, including the bestselling text, Basic Engineering Circuit Analysis,

Bill D, Carroll is an IEEE Fellow and Professor and Chair of the Department of Computer Seience and

eee eee eo UC mee ae ee eect

eee nets caterer cra nsery

education, Widely published, he is coauthor of Fault Tolerant Computing: An Introduction

ISBN O-13-4b3894-8

“SLUB DRESDEN

Le ie eee Kl | | | |

Ta Se Rei ULE 30590118

Digital Logic

Circuit Analysis

and Design

Victor P. Nelson

Auburn University

H. Troy Nagle

North Carolina State Univesity

Bill D. Ci

University 0

i-Arlington

J. David Irwin

Auburn University

Prentice Hall, Upper Saddle River, New Jersey 07458

Ccataloging-in-Pubt cation Oat

Digital gic circuit anelyste and design / Victor P. Nelson... (ey

we

Developed fren tntraguction to coxputer lopic. 1978

Tretuaes fea) neferancee and tnaet.

a 2, Electronte digital

conpute i. Melson, Vietor 9,

to comput

e760" 4.964 1995,

621-388-3020 935122

ce

Acquisitions Editor: Doo Foley

Praduction Editor: Joe Scordato

Copy Bator: Bill Thomas

Designer: Amy Rosen

Cover Designee: Waren Fischbach

‘Buyer: Bill Scazzero

© 1995 by Prentice-Hall, Inc.

Upper Saddle River, New Jersey 07458

‘The author and publisher of this hook have used thet best efforts in preparing this book. These

cffons include the development, esearch, and testing ofthe shears aa programs to determine

their effectivenes. The auibor and pals make no waranty of any kind, expressed or implied,

swith regard to these programs or the documentation contained in this book. The author and pub

lisher shall not be ible in any event for incidental or consequential damages in Connection sith,

cor arising out of, the furishing, performance, or use ofthese programs,

[All igs teserved. No part ofthis book may be reproduced in any form or by any meaas. eth:

‘out permission in writing fom the publisher

Printed in the United States of America

wooar

ISBN O-13-4b389u-8

PRENTICE-HALL INTERNATIONAL (UK) LisrED, LonDON

[PRENTICE-HALL OF AUSTRALIA Pry. LIMITED, SYDNEY

PRENTICE-HALL CANADA INC,, TORONTO

PRENTICE-HALL HispaNoaMaricana, S.A., MEXICO

‘PRENTICE-HALL OF INDIA Pravate LIMITED, New DeLi

PRENTICE-HALL OF [APAN, INC., TOKYO

PEARSON EDUCATION ASIA PTE. L1D,, SINGAPORE

EDITORA PRENTICE-HALL DO Brasit, LtbA., RIO DE JANEIRO

BD Preface

'B 0 Introduction

v4

0.2

0.3

04

Contents

History of Computing

0.1.1 Beginnings: Mechanical Computers

0.1.2 Early Electronic Computers

0.1.3. The First Four Generations of Computers

Q.14 The Fifth Generation and Beyond

Digital Systems

0.2.1 Digital vs Analog Systems

0.2.2 Digital System Design Hierarchy

Organization of a Stored Program Digital Computer

0.3.1 Computer Instructions

0.3.2. Information Representation in Computers

0.3.3 Computer Hardware

0.3.4 Computer Software

Summary

® 1 Number Systems and Codes

141

Number Systems

1.1.1 Positional Notation

1.1.2 Commonly Used Number Systems

xv

me bP even e ao

12

2B

15

M7

19

20

a

a

22

iv Contents

1.2

13

14

1.5

1.6

Arithmetic

1.2.1 Binary Arithmetic

1.2.2 Octal Arithmetic _

1.2.3. Hexadecimal Arithmetic

Base Conversions

1.3.1 Conversion Methods

1.3.2 General Conversion Algorithms

1.3.3 Conversion Between Base A and Base B When B = A‘

Signed Number Representation

1.4.1 Sign-Magnitude Numbers

1.4.2 Complementary Number Systems

Computer Codes

1.8.1 Numeric Codes

1.5.2. Character and Other Codes

15.3 Error Detection Codes and Correction Codes

Summary

® 2 Algebraic Methods for the Analysis and Synthesis

of Logic Circuits

24

22

Fundamentals of Boolean Algebra

2.1.1 Basic Postulates

2.1.2 Venn Diagrams for Postulates [2]

241.3 Duality

2.1.4 Fundamental Theorems of Boolean Algebra

Switching Functions

22.1 Truth Tables

2.2.2 Algebraic Forms of Switching Functions

2.2.3 Derivation of Canonical Forms

2.2.4 Incompletely Specified Functions

78

79

9

81

84

90

93

o4

101

103

23

24

25

26

27

28

Contents v

Switching Circuits

23.1 Electronic Logic Gates

2.3.2 Basic Functional Components

Analysis of Combinational Circuits

2.4.1 Algebraic Method

2.4.2 Analysis of Timing Diagrams

Synthesis of Combinational Logic Circuits

2.5.1 AND-OR and NAND Networks

2.5.2 OR-AND and NOR Networks

2.5.3 Two-Level Circuits

254

25

Applications

Computer-Aided Design of Logic Circuits

2.7.1 The Design Cycle

2.7.2 Digital Cireuit Modeling

2.7.3. Design Synthesis and Capture Tools

2.7.4 Logic Simulation

Summary

B 3 Simplification of Switching Functions

34

3.2

3.3

Simplification Goals

Characteristics of Minimization Methods:

Karnaugh Maps

3.3.1 Relationship to Venn Diagrams and Truth Tables

3.3.2 _K-Maps of Four or More Variables

104

104

108

120

120

123

128

128

130

131

133

134

136

140

140

140

148

152

165

172

173

174

175

176

a7

vi

Contents

3.4

3.5

3.6

37

3.8

3.9

3.10

3.11

3.12

Plotting Functions in Canonical Form on the K-Map

Simplification of Switching Functions Using K-Maps

3.5.1 Guidelines for Simplifying Functions Using K-Maps

3.5.2 General Terminology for Switching Function

Minimization

3.8.3. Algorithms For Deriving Minimal SOP Forms From

K-Maps

PQS Form Using K-Maps

3.6.1 General Terminology for POS Forms

3.6.2. Algorithms For Deriving Minimal POS Forms From

K-Maps

Incompletely Specified Functions

Using K-Maps To Eliminate Timing Hazards

Quine-McCluskey Tabular Minimization Method

3.9.1 Covering Procedure

3.9.2 Incompletely Specified Functions

39.3 Systems With Multiple Outputs

Petrick’s Algorithm

Computer-aided Minimization of Switching

Functions

3.11.1 Cube Representation of Switching Functions

3.11.2 Algebraic Methods for Determining Prime

Implicants

3.11.3 Identifying Essential Prime Imy

3.11.4 Completing a Minimal Cover

3.11.8 Other Minimization Algorithms

nts,

Summary

179

185

187

187

188

197

197

197

203

206

211

215

218

219

222

224

227

228

230

231

234

234

Contents vit

B® 4 Modular Combinational Logic

44

42

43

44

45

46

47

48

49

Top-Down Modular Design

Decoders

421 Decoder Circuit Structures

4.2.2 Implementing Logic Functions Using Decoders

4.2.3 Enable Control Inputs

4.2.4 Standard MSI Decoders

4.2.5 Decoder Appli

Encoders

43.1 Encoder Circuit Structures

4.3.2. Standard MSI Encoders

MultiplexersiData Selectors

4.4.1 Multiplexer Circuit Structures

4.4.2 Standard MSI Multiplexers

44,3 Applications of Multiplexers

Demultiplexers/Data Distributors

Binary Arithmetic Elements

4.6.1 Basic Binary Adder Circuits

4.6.2 MSI Binary Adder Modules

4.6.3 High-speed Adder Units

4.6.4 Binary Subtraction Circuits

46.5 Arithmetic Overflow Detection

Comparators

Design Example: A Computer Arithmetic Logic Unit

Computer-aided Design of Modular Systems

4.9.1 Design Libraries

4.9.2 Drawing Hierarchical Schematics

242

243

245

246

247

249

252

253

259

260

264

268

268

270

277

280

283

285

289

294

295

298

302

312

312

314

viii Contents

4.10 Simulation of Hierarchical Systems

4.11 Summary

'B 5 Combinational Circuit Design with Programmable

Logic Devices

54

eae

5.3

54

55

‘Semicustom Logic Devices

Logic Array Circuits

Diode Operation in Digital Circui

AND and OR Logic Arrays

‘Two-Level AND-OR Arrays

Field-Programmable AND and OR Arrays

Output Polarity Options

Bidirectional Pins and Feedback Lines

‘Commercial Devices

Field-programmable Logic Arrays

5.3.1 FPLA Circuit Structures

5.3.2. Realizing Logic Functions With FPLAs

Programmable Read-only Memory

5.4.1 PROM Circuit Structures

5.4.2 Realizing Logic Functions With PROMs

3. Lookup Tables

5.4.4 General Read-only Memory Applications

5.4.5 Read-only Memory Technologies

Programmable Array Logic

5.5.1 PAL Circuit Structures

5.5.2 Realizing Logic Functions With PALS

5.5.3. PAL Output and Feedback Options

317

319

327

329

330

332

333

338

341

343

345

347

347

347

350

350

352

358

360

361

362

362

363

366

56

5.7

Contents

Computer-aided Design Tools for PLD Design

5.6.1 Design Representation with PDL

5.6.2 Processing a PDL Design File

Summary

B 6 Introduction to Sequential Devices

61

62

63

6.4

65

6.6

67

68

Models for Sequential Circuits

6.1.1 Block Diagram Representation

6.1.2 State Tables and Diagrams

Memory Devices

Latches

63.1 Set-Reset Latch

63.2 Gated SR Latch

633 Delay Lateh

Flip-Flops

Master-Slave SR Flip-Flops

Master-Slave D Flip-Flops

Master-Slave JK Flip-Flops

Edge-triggered D Flip-Flops

Edge-triggered JK Flip-Flops

‘T Flip-flops

Latch and Flip-fop Summary

64.1

64.2

6.4.3

6.4.4

645

6.4.6

64.7

Other Memory Devices

Timing Circuits

6.6.1 One-shots

6.6.2 ‘The 555 Timer Module

Rapidly Prototyping Sequential Circuits

Summary

ix

371

373

379

380

382

383

383

385

387

389

389

396

398

403

404

406

407

409

413

415

417

418

418

418

418

421

425

X Contents

'® 7 Modular Sequential Logic

7A

7.2

73

74

75

7.6

WW

7.8

Shift Registers

7.1 A Generic Shift Register

7.1.2 Standard TTL Shift-Register Modules

Design Examples Using Registers

7.2.1 Serial Adder Unit

7.2.2, Serial Accumulators

7.2.3 Parallel Accumulators

Counters

7.3.1 Synchronous Binary Counters

7.3.2 Asynchronous Binary Counters

7.3.3 Down Counters

7.34 Up/Down Counters

Modulo-N Counters

Synchronous BCD Counters

Asynchronous BCD Counters

‘Modulo-6 and Modulo-12 Counters

Asynchronously Resetting Modulo-N Counters

‘Synchronously Resetting Modulo-N Counters

Shift Registers as Counters

751 Ring Counters

7.5.2 Twisted-ring Counters

Muitipfe-sequence Counters

Digital Fractional Rate Multipliers

171 TTL Modules

7.7.2 Cascading the Digital Fractional Rate Multipliers

Summary

432

433

434

436

446

448

450

450

451

455

458

464

467

470

474

477

477

478,

482

489

489

491

495

496

Contents xi

BD 8 Analysis and Synthesis of Synchronous

Sequential Circuits

84

8.2

8.3

8.4

85

8.6

B 9 Simpl

91

9.2

Synchronous Sequential Circuit Models

8.1.1 Mealy Model

8.1.2 Moore Model

Sequential Circuit Analysis

8.2.1 Analysis of Sequential Circuit State Diagrams

8.2.2 Analysis of Sequential Circuit Logic Diagrams

8.2.3 Summary

Synchronous Sequential Circuit Synthesis

8.3.1 Synthesis Procedure

8.3.2 Flip-flop Input Tables

8.3.3 Application Equation Method for JK Flip-flops

8.3.4 Design Examples

8.3.5 Algorithmic State Machine Diagrams

8.3.6 One-hot Finite-State Machine Design Method

incompletely Specified Circuits

8.4.1 State Assignment and Circuit Realization

Computer-aided Design of Sequential Circuits

8.5.1 Design Capture and Synthesis

8.5.2 Design Analysis and Verification

summary

ation of Sequential Circuits

Redundant States

9.1.1 State Equivalence

9.1.2 Equivalence and Compatibility Relations

State Reduction in Completely Specified Circuits

9.2.1 Inspection

502

503

504

505

507

507

508

S17

519

520

522

524

526

547

553

555

588

558

559

565

568

576

577

377

579

579

379

xii Contents

9.3

94

9.5

92.2 Parti

State Reduction In Incompletely Specified Circuits

9.3.1 State Compatibility

9.3.2 Minimization Procedure

Optimal State Assignment Methods

9.4.1 Unique State Assignments

9.4.2 State Assignment Guidelines

9.4.3 Partitioning

9.44 Optimal State Assignments

Summary

® 10 Asynchronous Sequential Circuits

10.4

10.2

10.3

10.4

10.5

10.6

Types of Asynchronous Circuits

Analysis of Pulse-mode Asynchronous Circuits

‘Synthesis of Pulse—mode Circuits

10.3.1 Design Procedure for Pulse-mode Circuits

Analysis of Fundamental-mode Circuits

10.4.1 Introduction

104.2 Tabular Representations

1043 Analysis Procedure

Synthesis of Fundamental-mode Circuits

10.5.1 Synthesis Procedure

Introduction to Races, Cycles, and Hazards

10.6.1 Races and Cycles

1066.2 Avoidance of Race Conditions

10.6.3 Race-free State Assignments

10.6.4 Hazards

10.65 Analysis,

581

584

588

589

594

602

603

605

614

619

20

624

625

627

632

632

641

643

645

648

648

648

659

660

663

664

onl

673

10.7 Summary

B® 11 Sequential Circuits With Programmable Logi

Contents xili

Devices

11.1. Registered Programmable Logic Devices

11.1.1 Field-Programmable Logic Sequencers

1.1.2

Registered PALs

11.13 PLDs with Programmable Logic Macrocells

11.2, Programmable Gate Arrays

1.2.1

11.2.2

11.3 Sequential Circuit Design and PLD Device Selection

Logic Cell Arrays

ACT FPGAs

11.4 PLD Design Examples

11.5 Computer-aided Design of Sequential PLDs

11.5.1 Sequential Circuit Design Representation with PDL

15.2

Processing a PDL Design File

11.6 Summary

B 12 Logic Circuit Testing and Testable Design

12.1 Digital Logic Circuit Testing

12.2. Fault Models

12.3 Combinational Logic Circuit Testing

12.3.1

12.3.2

Test Generation

Untestable Faults

Multiple Output Networks

Fault Detection Test Sets

Fault Location and Diagnosis

Random Testing

673

686

687

oo

696

700

702

705

13

715

nN7

723

23

29

733

738

739

740

741

742

751

752

753

757

758

xiv Contents

12.4

12.5

12.6

12.7

12.8

Sequential Logic Circuit Testing

Design For Testability

12.5.1 Scan Path Design

Built-in Seff-test

12.6.1 Pseudorandom ‘Test Vector Generation

12.62 Signature Analysis

12,63 Built-In Logic Block Observer

Board and System-level Boundary Scan

Summary

B 13 Design Examples

13.1

13.2

13.3

13.4

B Index

Electronic Slot Machine

13.1.1 Problem Defi

13.1.2 System Requirements and Solution Plan

13.13 Logie Design

Keyless Auto Entry System

13.2.1 Problem Definition

13.2.2 System Requirements

13.2.3 Logic Design

One-lane Traffic Controller

13.3.1 System Requirements

13.3.2 Logie Design

Grocery Store Cash Register

13.4.1 System Requirements

13.4.2 Logie Design

760

763

764

768

769

712

718

777

781

788

789

789

790

792

801

801

805

810

813

815

821

823

824

833

B® The Need for This Book

‘This text has been developed from a previous work, An Introduction 10

Computer Logic (1974) by Nagle, Carroll, and Inwin, which was a widely

adopted text on the fundamentals of combinational and sequential logic circuit

analysis and synthesis. The original book was praised for its clarity and teach-

ing effectiveness, and despite rapid changes in the field in the late 70°s and

early 80's, the book continued to enjoy wide use many years after its original

publication date, underscoring the interesting fact that during most of the pe-

riod since the publication of that book, the mainstream educational approach

to introductory-level courses in digital design evolved quite slowly, even while

‘major technological changes were rapidly being adopted in industry.

How things have changed! Recently, the astronomical proliferation of

digital circuit applications and phenomenal increases in digital circuit com-

plexity have prompted significant changes in the methods and tools used in

digital design. Very Large Scale Integrated (VLSI) circuit chips now routinely

contain millions of transistors; computer-aided design (CAD) methods, stan-

dard cells, programmable logic devices, and gate arrays have made possible

rapid turnaround from concept to finished circuit, supported by increased em-

phasis on hierarchical, modular designs utilizing libraries of standard cells and

other predesigned circuit modules. We have developed a text which supports,

those changes, but we have also worked carefully to preserve the strong cov-

erage of theory and fundamentals.

An effective digital design engineer requires a solid background in fun-

damental theory coupled with knowledge of practical real-world design prin-

ciples. This text contains both. It retains its predecessor's strong coverage of

fundamental theory. To address practical design issues, over half of the text is,

new material that reflects the many changes that have occurred in recent years,

including modular design, CAD methods, and the use of programmable logic,

as well as such practical issues as device timing characteristics and standard

logic symbols,

xvi Preface

B Intended Audience

This book is intended for sophomore, junior, and seaor-fevel courses in digi-

tal logic circuits and digital systems for engineers and scientists who may be

involved with the design of VLSI circuits, printed circuit boards, multi-chip

‘modules, and computer circuits.

No particular background in electronic circuits or computer systems is

assumed or required, and thus the text is suitable for a first course in digital

systems. However, the book contains sufficient advanced material and depth

to support the needs of mote advanced students. This text has heen designed

to allow each instructor the flexibility to select topics according to the needs

of his or her specific course.

This text is also suitable for the reader who wishes to use the self-study

approach to learn digital design, and is useful as a reference for practicing en-

gineers.

® Significant Features

This book is a unique work representing the combined efforts of the four au-

thors at tree universities. In addition to extensive publisher-sponsored

viewing, the manuscript was used in courses at all three schools during its de

velopment, with feedback from students and instructors incorporated into the

book,

Noteworthy features include:

+ Solid coverage of fundamente! concepts and theory coupled with practical

real-world design methods

‘+ Astrong emphasis on developing and using systematic problem solving and

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Gracie Diet PDFDocument12 pagesThe Gracie Diet PDFGabrielNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Food and Nutrition PPT TANMAYDocument12 pagesFood and Nutrition PPT TANMAYTanmay SinghalNo ratings yet

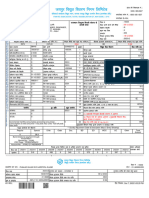

- Billprint 16030727Document1 pageBillprint 16030727Ruloans VaishaliNo ratings yet

- Book Publication SummaryDocument38 pagesBook Publication SummaryYuvraj JadhavNo ratings yet

- 10 1016@j Compgeo 2012 07 011Document5 pages10 1016@j Compgeo 2012 07 011MohamedNo ratings yet

- 1st Holy CommunionDocument162 pages1st Holy Communionmoscle bawatNo ratings yet

- Ferrari On FroomeDocument2 pagesFerrari On FroomeRaceRadioNo ratings yet

- Bangkok: Standard Standard Perez 2000-2009 1991-2010Document5 pagesBangkok: Standard Standard Perez 2000-2009 1991-2010Zaw Moe KhineNo ratings yet

- ASTM E3-11 Standard Guide For Preparation of Metallographic SpecimensDocument12 pagesASTM E3-11 Standard Guide For Preparation of Metallographic SpecimensCamilo PolaniaNo ratings yet

- Reported by Nacito, Julie Ann T. & Tiongson, Annie Joy MDocument19 pagesReported by Nacito, Julie Ann T. & Tiongson, Annie Joy MTrixie Marie Sabile AbdullaNo ratings yet

- Guide Thermal Cameras-CatalogDocument14 pagesGuide Thermal Cameras-CatalogRichard GumanitNo ratings yet

- AVA Food Factory Grading SystemDocument10 pagesAVA Food Factory Grading Systemstewart_hockNo ratings yet

- ASSIGNMENT Organicanalysisnew 20230929150340Document4 pagesASSIGNMENT Organicanalysisnew 20230929150340sogarongtNo ratings yet

- Jelovnik Druga KućaDocument4 pagesJelovnik Druga KućaDragoljub MilinovićNo ratings yet

- Feminist Perspective: Dube and Rege: Dr. Asima JenaDocument23 pagesFeminist Perspective: Dube and Rege: Dr. Asima JenaI Made Wisnu BuanaNo ratings yet

- Jollibee Al Khuwair Breaklist Name Duty Hours Breaks Hours Remarks/Meal CounterDocument42 pagesJollibee Al Khuwair Breaklist Name Duty Hours Breaks Hours Remarks/Meal CounteranneNo ratings yet

- Skanda Shashti Hindu FestivalDocument2 pagesSkanda Shashti Hindu FestivalSanatana Dharma FoundationNo ratings yet

- Contractor SHE Plan-HANNESDocument16 pagesContractor SHE Plan-HANNESMominé Ve100% (2)

- Module 2 HomeworkDocument4 pagesModule 2 HomeworkCj LinceNo ratings yet

- Panchakarma Process PDFDocument6 pagesPanchakarma Process PDFPartheebanNo ratings yet

- Plunger and Barrel WebDocument2 pagesPlunger and Barrel WebTanishq ShettyNo ratings yet

- Case Study: Tourism and Biodiversity (Ecotourism - A Sustainable Development Tool, A Case For Belize)Document34 pagesCase Study: Tourism and Biodiversity (Ecotourism - A Sustainable Development Tool, A Case For Belize)Aarthi PadmanabhanNo ratings yet

- Gujarat Technological University: Subject Code: 2151603 Date: Subject Name: Computer Graphics Time: Total Marks: 70Document2 pagesGujarat Technological University: Subject Code: 2151603 Date: Subject Name: Computer Graphics Time: Total Marks: 70RutvikNo ratings yet

- Instruction Manual: VLT HVAC Drive FC 102Document88 pagesInstruction Manual: VLT HVAC Drive FC 102Franz BlunkNo ratings yet

- Choledo A4Document53 pagesCholedo A4Czarina ManinangNo ratings yet

- Centre For Transformation, Growth, Healing & Health JamshedpurDocument103 pagesCentre For Transformation, Growth, Healing & Health Jamshedpurnarendramaharana39No ratings yet

- Verus CFT CommercialDocument2 pagesVerus CFT CommercialLuchin SheckNo ratings yet

- FSA201906-FMAX Footstep ReplacementDocument4 pagesFSA201906-FMAX Footstep ReplacementmarianchiNo ratings yet

- 5 Nanomaterial in Fuel CellDocument24 pages5 Nanomaterial in Fuel CellElma AmalinaNo ratings yet

- HaffansDocument3 pagesHaffansmanishvashishthaNo ratings yet