Professional Documents

Culture Documents

CMOS amplifier design with 28dB gain and 100MHz bandwidth

Uploaded by

賴正翔Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CMOS amplifier design with 28dB gain and 100MHz bandwidth

Uploaded by

賴正翔Copyright:

Available Formats

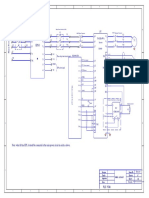

V3

MbreakP MbreakP 1.8

3.3

W W

L L

R3 M5 M6

0

OUT

C1

M1 W W M2 250f

L L

V1 V4

DC MbreakN MbreakN DC 0

AC = 1

0

0 0

M4 M3

HW#8:

W W

L L

M=1 MbreakN MbreakN M

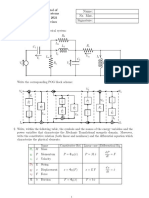

Please design an CMOS amplifier using 0.18um CMOS model to

meet the differential gain Av ≥ 28dB and f3dB ≥ 100MHz. The DC

bias voltage of output port is 0.9V. The loading capacitance is

0.25pF.

1. Please derive the DC voltage gain equation of the above amplifier.

2. Please also write down its small-signal model parameters gm, gds,

Cgs, and Cgd values of M2 and M6 at your bias condition.

3. Please specify all the device sizes, input DC bias voltage, bias

current, the calculated and simulated Gain and the simulated

f3dB.

CYCU/EL, Chun-Chieh Chen, AIC 1

You might also like

- DC-AC Inverter 10KWDocument125 pagesDC-AC Inverter 10KWnishan80% (5)

- 3000 MRLDocument23 pages3000 MRLNguyễn Thân100% (1)

- Electric Drawing-FR2000Document19 pagesElectric Drawing-FR2000MuMoMa100% (1)

- Plano Fuji Yida NuevoDocument18 pagesPlano Fuji Yida Nuevooro plata100% (1)

- King Tone Blues Power SchematicDocument1 pageKing Tone Blues Power SchematicDavid BrownNo ratings yet

- 380V Electrical Drawing PDFDocument34 pages380V Electrical Drawing PDFMujianaNo ratings yet

- Motor Control System Wiring DiagramDocument9 pagesMotor Control System Wiring DiagramVăn Quyền NguyễnNo ratings yet

- MACD Homework 3 Circuit AnalysisDocument4 pagesMACD Homework 3 Circuit AnalysisBerk_Omuz_1936No ratings yet

- Drawing WiringDocument1 pageDrawing WiringPapahnya Qiana MaulinaNo ratings yet

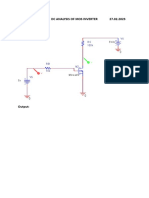

- DC Analysis of Nor Gate: Mbreakp 5VdcDocument3 pagesDC Analysis of Nor Gate: Mbreakp 5VdcPranjal JalanNo ratings yet

- Circuit Diagram:: DC Analysis of Mos Inverter 27.02.2023Document2 pagesCircuit Diagram:: DC Analysis of Mos Inverter 27.02.2023Satyam SinghNo ratings yet

- Assignment 06Document2 pagesAssignment 06Anchal Debnath ee21b017No ratings yet

- MS46 MS41 MS81 - InstallDocument4 pagesMS46 MS41 MS81 - InstallLe HieuNo ratings yet

- WMB 9 Color Hong PDFDocument40 pagesWMB 9 Color Hong PDFfabioboogNo ratings yet

- AUMADocument4 pagesAUMAbj156iNo ratings yet

- Schematic Components That Have Been Frozen by The User Will Appear With Blue Reference DesignatorsDocument1 pageSchematic Components That Have Been Frozen by The User Will Appear With Blue Reference DesignatorsIvanê FonsecaNo ratings yet

- Wiring diagram bagging machine 1TDocument10 pagesWiring diagram bagging machine 1TRahman AuliaNo ratings yet

- Topswitch: Designing Multiple Output Flyback Power Supplies WithDocument24 pagesTopswitch: Designing Multiple Output Flyback Power Supplies WithDinh TucNo ratings yet

- ASADASDDocument4 pagesASADASD195250No ratings yet

- DNSD 339 FDocument2 pagesDNSD 339 FrajeshdaveNo ratings yet

- PRELAB2Document8 pagesPRELAB2Fabricio OrtizNo ratings yet

- High-End Preamp With ECC88 (Schematic-1)Document1 pageHigh-End Preamp With ECC88 (Schematic-1)BIỂN NGUYỄN QUỐCNo ratings yet

- Ipod FM TransmitterDocument19 pagesIpod FM TransmitterLarissa Duron100% (1)

- Webench Design Report: Electrical BOMDocument5 pagesWebench Design Report: Electrical BOMshreerangarbrNo ratings yet

- Schematic - UPS NEW MODEL - 2023-09-11Document1 pageSchematic - UPS NEW MODEL - 2023-09-11aasbuildsNo ratings yet

- Modeling and Control of Electromechanical Systems Test QuestionsDocument6 pagesModeling and Control of Electromechanical Systems Test QuestionsThanujaNo ratings yet

- 1-Power Line DiagramDocument1 page1-Power Line DiagramEmir AzharNo ratings yet

- L10xxy-3 SensoresDocument1 pageL10xxy-3 SensoresDrteslaNo ratings yet

- Schematic1 - Page1Document1 pageSchematic1 - Page1Eldys Juan Lima SotoNo ratings yet

- Main MCCB and control circuit diagramDocument9 pagesMain MCCB and control circuit diagramSatish ShahiNo ratings yet

- Digital Simulation of An Electrical Circuit (Including Dependent Sources) To Find Node Voltages and Branch Currents Using PspiceDocument2 pagesDigital Simulation of An Electrical Circuit (Including Dependent Sources) To Find Node Voltages and Branch Currents Using PspiceVikas BeemaNo ratings yet

- EEE 360 Chapter 9 Power Electronics and Motor Control PSpice SimulationDocument34 pagesEEE 360 Chapter 9 Power Electronics and Motor Control PSpice SimulationMichael DarmstaedterNo ratings yet

- Bass Preamp PCB Schematics (568SCH - 0)Document1 pageBass Preamp PCB Schematics (568SCH - 0)Fernando PastrianNo ratings yet

- 12v 4A 115-300 TOP245GX-TO220Document1 page12v 4A 115-300 TOP245GX-TO220Antonio Rezende NetoNo ratings yet

- Advance Communication Laboratory Experiments: Prepared, Edited byDocument5 pagesAdvance Communication Laboratory Experiments: Prepared, Edited byEloisa VictorioNo ratings yet

- Topswitch: Designing Multiple Output Flyback Power Supplies WithDocument24 pagesTopswitch: Designing Multiple Output Flyback Power Supplies WithHải TrầnNo ratings yet

- MMSR 2-Band Schematic v1.03Document1 pageMMSR 2-Band Schematic v1.03ArielNo ratings yet

- iwomi electDocument5 pagesiwomi electP1nice48No ratings yet

- Splnproc 1703Document9 pagesSplnproc 1703doanminhtien030903No ratings yet

- IIT Kanpur Homework on Oscillators and Bistable CircuitsDocument1 pageIIT Kanpur Homework on Oscillators and Bistable CircuitsAditya TiwariNo ratings yet

- Electrical Drawing 1Document1 pageElectrical Drawing 1Nam NguyễnNo ratings yet

- High Voltage Shunt RegulatorDocument1 pageHigh Voltage Shunt RegulatorHertanto Setiawan Phunsuk WangduNo ratings yet

- PLC - Ctrinh (Ups)Document4 pagesPLC - Ctrinh (Ups)Trần Đức HoàngNo ratings yet

- Multi-output voltage regulator circuit diagramDocument1 pageMulti-output voltage regulator circuit diagramtoony reyesNo ratings yet

- Priyanka ProjectDocument1 pagePriyanka ProjectPriyanka DeshpandeNo ratings yet

- (AP0) (AP1) : MCCB 30ADocument1 page(AP0) (AP1) : MCCB 30AMuhammad Bilal FarooqNo ratings yet

- Hoverboard 6 Mekotron hb-0060k E-Board Repair InfoDocument7 pagesHoverboard 6 Mekotron hb-0060k E-Board Repair InfoElison QuezadaNo ratings yet

- CAP Panel Schematic - FairlightUSDocument37 pagesCAP Panel Schematic - FairlightUSBastiaan de WaardNo ratings yet

- BAn Ve Tu Nuoc Thai (New)Document4 pagesBAn Ve Tu Nuoc Thai (New)Anh NguyenNo ratings yet

- Belimo EV..F K BAC 1 Installation-InstructionsDocument3 pagesBelimo EV..F K BAC 1 Installation-InstructionsArno MatthiasNo ratings yet

- Schematic Mosfet Esc 2022-02-15Document1 pageSchematic Mosfet Esc 2022-02-15Natan MiklasNo ratings yet

- Schematic - Mosfet Esc - 2022-02-15Document1 pageSchematic - Mosfet Esc - 2022-02-15ReymondJosuéArgüelloRojasNo ratings yet

- Mod Dimmer 5A 2LDocument1 pageMod Dimmer 5A 2LRazwan ali saeedNo ratings yet

- MCSEM Test 2021 01 11 SolutionDocument6 pagesMCSEM Test 2021 01 11 SolutionThanujaNo ratings yet

- Panel PLC Biodigester Farm CigandulDocument50 pagesPanel PLC Biodigester Farm Cigandulrahmannafi kurniawanNo ratings yet

- SBD30-100XL 01 Uk PDFDocument5 pagesSBD30-100XL 01 Uk PDFhepcomotionNo ratings yet