Professional Documents

Culture Documents

Advanced Computer Achitecture (CT-404)

Uploaded by

abhiraj12340 ratings0% found this document useful (0 votes)

67 views3 pagesACA

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentACA

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

67 views3 pagesAdvanced Computer Achitecture (CT-404)

Uploaded by

abhiraj1234ACA

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 3

MIS Number [_ I T

COLLEGE OF ENGINEERING, PUNE

(An Autonomous Institute of Govt. of Maharashtra)

Final Exam 2013

(CT 404) Advanced Computer Architecture

Class: - B.Tech (Computer Engineering)

ester: = VII

Max. Marks: - 60

All the Questions are compulsory.

Assume suitable data whenever necessary.

Draw neat figures wherever required

Figures to right indicate full marks

Q.1 Multiple Choice Questions (MCQs) 10

1, Itanium processox Which hazard can be circumvented by register rotation

a. Control Hazards

b. Data Hazards

c. Structural Hazards

4. None

e. None of the answer above is correct.

Interconnection network, topology :How many links has a 5 by 5 mesh?

a 16

b. 25

ce. 40

d. 30

e. None of the answer above is correct

3. The hardware mechanism that enables a device to notify the CPU is called

a. Polling

b. Interrupt

ce. System Call

d. None of the above

4. An interrupt for which hardware automatically transfers the program to a specific

memory location is known as

a. Software interrupt

b. Hardware interrupt

©. Maskable interrupt

d. Vector interrupt

5. In register stack a stack can be organized by a_number of register:

a. Infinite number

b. Finite number

©. Both

.. & None

6. Instruction formats contains the memory address of the,

a. Memory data

b. Main memory

©. CPU

d. ALU

7. Address format can be represented as

a. dst <[srel [sre2]

bb. dst >fsrel]fsre2]

ce. dst <->[srel ][sre2]

Page 1

dd. Allof these

8. In which addressing the operand is actually present in instruction

a, Immediate addressing

b. Direct addressing

c. Register addressing

4d. None of these

9. ength instruction some programs wants a complex instruction set containing more

instruction, more addressing modes and greater address rang, as in case of

a. RIS

b. CISC

©. Both

d._ None

10. which instruction are used to perform Boolean operation on non-numerical data

a. Logical and bit manipulation

b. Shift manipulation

¢. Circular manipulation

4

None of these

Q.2 Write down True or False: 5

1. Computations need not to be completed within a “reasonable” time period

Given p processors and the maximum fraction of a problem that can be provided into

parallel tasks, Amdahi's law predicts that as p goes to infinity, the speedup S(p)

approaches Lf.

3. Linear Speedup is defined as maximum speedup is usually p with p processors

4. Parallel computing is using more than one computer, of a computer with more than

cone processor, to solve a problem.

5, Mutual Exclusion is a mechanism for ensuring that only one process accesses

particular resource ata time to establish sections of code involving the resource as so-

called critical sections and arrange that only one such critical section is executed at at

time

Q.3_ Fillin the blanks:

LA process is a process that is treated as a completely separate

program with its own variables, stack, and memory allocation.

2. ___ are groups of interconnected “commodity” computers achieving

high performance with low cost.

3. as a parallel programming platform is an alternative to expensive

Supercomputers,

4. A hardware design that allows the system to be inereased in size and doing so to

obtain performance could be described as ___or

5. Loosely coupled is also called as

Q.4 What is Latency hiding technique? Elaborate with example. 8

Q.5 Discuss the various context switching policies implemented in multithreading 4

architecture,

OR

Suppose the time delay of the four stages are T1-40ns, T2-90ns, Ts-70ns, T480ns

and the interface latency has a delay of T)-12ns. Caleulate eycle time, clock

frequency, speedup over the non-pipeline adder design and maximum speedup

Page 2

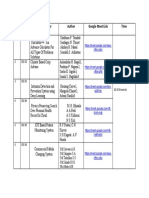

QT

Qs

Qo

can be achieved.

What is the difference between grid computing and cluster computing?

features of grid computing.

Explain with diagram COW and NOW architecture,

Explain in brief the programming model of Cray-1 vector processor.

Explain the arehitecture of itaniun processor in details.

Page 3

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- SYBTech Computer Science Engineering SyllabusDocument34 pagesSYBTech Computer Science Engineering Syllabusabhiraj1234No ratings yet

- UGCON/PGCON-2020: Name of Department: Computer Science and EngineeringDocument2 pagesUGCON/PGCON-2020: Name of Department: Computer Science and Engineeringabhiraj1234No ratings yet

- Sr. No Paper ID Title of Paper Author Google Meet Link Time: Nfmo-ObcDocument1 pageSr. No Paper ID Title of Paper Author Google Meet Link Time: Nfmo-Obcabhiraj1234No ratings yet

- Sr. No Paper ID Title of Paper Author Google Meet Link Time: Nfmo-ObcDocument1 pageSr. No Paper ID Title of Paper Author Google Meet Link Time: Nfmo-Obcabhiraj1234No ratings yet

- UG/PG Conference - 2021: Department of Computer Science & EngineeringDocument3 pagesUG/PG Conference - 2021: Department of Computer Science & Engineeringabhiraj1234No ratings yet

- SY BTech CSE Basic Structure Syllabus 2021-22Document28 pagesSY BTech CSE Basic Structure Syllabus 2021-22abhiraj1234No ratings yet

- Practical PlanDocument1 pagePractical Planabhiraj1234No ratings yet

- Participatory-Sensing-Enabled Efficient Parking Management in Modern CitiesDocument3 pagesParticipatory-Sensing-Enabled Efficient Parking Management in Modern Citiesabhiraj1234No ratings yet

- Threaded Binary Trees: Threads ThreadsDocument56 pagesThreaded Binary Trees: Threads Threadsabhiraj1234No ratings yet

- Avltrees 130531145604 Phpapp02Document43 pagesAvltrees 130531145604 Phpapp02abhiraj1234No ratings yet

- 07 6810 17Document16 pages07 6810 17R Mercy PaulNo ratings yet

- Multiway Search TreeDocument16 pagesMultiway Search Treeabhiraj1234No ratings yet

- B Trees 130126021111 Phpapp02Document31 pagesB Trees 130126021111 Phpapp02abhiraj1234No ratings yet

- Data Structures Lab Manual PDFDocument98 pagesData Structures Lab Manual PDFabhiraj1234No ratings yet

- Data Structures Lab ManualDocument159 pagesData Structures Lab Manualabhiraj1234No ratings yet

- Nomination FormDocument1 pageNomination FormHemakuriNo ratings yet

- Avl T: - Binary Search Trees - AVL TreesDocument26 pagesAvl T: - Binary Search Trees - AVL TreeslathasowmiyahNo ratings yet

- Pandit Madan Mohan Malaviya National Mission On Teachers and Teaching (PMMMNMTT)Document6 pagesPandit Madan Mohan Malaviya National Mission On Teachers and Teaching (PMMMNMTT)abhiraj1234No ratings yet

- FTPDocument2 pagesFTPabhiraj1234No ratings yet

- Multiway Search TreeDocument16 pagesMultiway Search Treeabhiraj1234No ratings yet

- Nomination FormDocument1 pageNomination FormHemakuriNo ratings yet

- GraphDocument8 pagesGraphabhiraj1234No ratings yet

- DownloadDocument3 pagesDownloadabhiraj1234No ratings yet

- Acc Ut-IDocument4 pagesAcc Ut-Iabhiraj1234No ratings yet

- C Lab ManualDocument45 pagesC Lab Manualabhiraj1234No ratings yet

- Librarians Retirement Age From 60 To 62Document4 pagesLibrarians Retirement Age From 60 To 62abhiraj1234No ratings yet

- Subject: Advance Architecture Author: Dr. Deepti Mehrotra Paper Code: MS Vetter: Lesson: Parallel Computer Models Lesson No.: 01Document188 pagesSubject: Advance Architecture Author: Dr. Deepti Mehrotra Paper Code: MS Vetter: Lesson: Parallel Computer Models Lesson No.: 01Jayant BhardwajNo ratings yet

- Report OnDocument2 pagesReport Onabhiraj1234No ratings yet

- SKN Sinhgad College of Engineering: Uuu Set DDocument3 pagesSKN Sinhgad College of Engineering: Uuu Set Dabhiraj1234No ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)