0% found this document useful (0 votes)

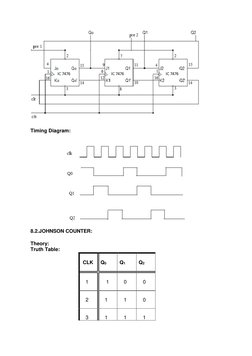

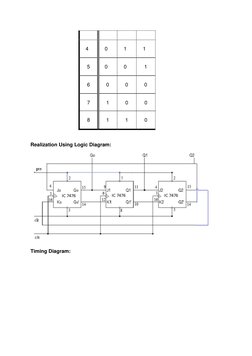

2K views4 pagesExpt No:7. Design and Testing of Ring Counter Date: and Johnson Counter

This document describes the design and testing of a 3-bit ring counter and Johnson counter using JK flip-flops. It includes truth tables, logic diagrams, and timing diagrams for each counter. It also provides the pin configuration of the IC chip used in the experiment and pre-lab and post-lab questions about counters.

Uploaded by

ChiranjeeviCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

2K views4 pagesExpt No:7. Design and Testing of Ring Counter Date: and Johnson Counter

This document describes the design and testing of a 3-bit ring counter and Johnson counter using JK flip-flops. It includes truth tables, logic diagrams, and timing diagrams for each counter. It also provides the pin configuration of the IC chip used in the experiment and pre-lab and post-lab questions about counters.

Uploaded by

ChiranjeeviCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd