Professional Documents

Culture Documents

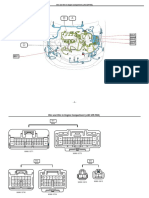

HUAWEI G620 Schematic PDF

HUAWEI G620 Schematic PDF

Uploaded by

hernanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HUAWEI G620 Schematic PDF

HUAWEI G620 Schematic PDF

Uploaded by

hernanCopyright:

Available Formats

DVDD12_EMI BUCK1_FB [4]

For low-power testing proposal.

It can be cancel for cost-down proposal

M11

1.2V IO for DDR2

U11

U12

V11

V12

V13

T13

T16

T17

T18

T21

U201-B

T11 H18

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS DVDD12_EMI

R11 DVSS DVDD12_EMI H16

R2 DVSS DVDD12_EMI H15

G6 DVSS DVDD12_EMI G9 VM_PMU

G7 DVSS DVDD12_EMI G11

G14 DVSS DVDD12_EMI G13

G17 G15 C142 C143 C144 C151 C130

DVSS DVDD12_EMI

G20 G16 VM12_SW_PMU

DVSS DVDD12_EMI

H10 DVSS DVDD12_EMI G18 100nF 100nF 100nF 100nF 10uF

M20 DVSS DVDD12_EMI H8

N11 DVSS DVDD12_EMI E7

A19 DVSS DVDD12_EMI F7

A26 DVSS DVDD12_EMI F8

B4 DVSS DVDD12_EMI G8 check MSDC1/2 Bottom cap/1st cap group check MSDC1/2

B10 DVSS DVDD12_EMI H11

E21 H13 IO power C115 close to pin E1 (150mil) IO power

DVSS DVDD12_EMI

F6

B12

DVSS

E1 C125 close to pin G26 (150mil) R101 0

VMC_PMU

DVSS DVDD28_MSDC1 R102 0

B14 DVSS DVDD28_MSDC2 V1 VIO18_PMU

R103 0

B17 DVSS DVDD28_BPI AD26 VIO18_PMU

B22 DVSS DVDD28_MD U25

B24 DVSS DVDD18_MSDC0 G26

R104 0

C4 DVSS DVDD18_IO0 L26 VIO18_PMU

C8 DVSS DVDD18_IO1 Y26

C11 DVSS DVDD18_IO2 D1

C12 DVSS DVDD18_IO3 W1

C16 AG13 C125 C115 C116 C117 C123 C122 C127 C128

DVSS DVDD18_IO4

C17 DVSS

C18 DVSS VCCK R10 100nF 1.0uF 100nF 100nF 100nF 100nF 100nF 100nF

C20 DVSS VCCK P9

C21 DVSS VCCK L11

C22 DVSS VCCK L12 VCORE_SW_FB [4]

C23 DVSS VCCK L13

C25 DVSS VCCK L14

D4 DVSS VCCK L15

D5 DVSS VCCK L16

VCCK

D7 DVSS VCCK L17

D9 DVSS VCCK M10

D11 DVSS VCCK M18 C140

C104 C124 C131 C152 C153 C129 C136 C137

1.0uF

1.0uF

D13 DVSS VCCK N10

D15 DVSS VCCK N18

D17 P18 100nF 100nF 100nF 1.0uF 22uF

DVSS VCCK 10uF 10uF

D21 DVSS VCCK R9

D24

E5

DVSS VCCK R18

T10

Bottom cap 1st cap group

DVSS VCCK

E8 DVSS VCCK U10

E10 DVSS VCCK V10

E18 DVSS VCCK_VPROC

F18 DVSS VCCK_VPROC N12 VPROC_PMU

P21 DVSS VCCK_VPROC N13

L10 DVSS VCCK_VPROC N14

VCCK_VPROC N15

AE5 N16 C156 C157 C158 C148 C155 C154 C132 C133 C134

1.0uF

1.0uF

1.0uF

AVSS18_WBG VCCK_VPROC

V7 DVSS VCCK_VPROC N17

U7 DVSS VCCK_VPROC P14 100nF 100nF 100nF

22uF 22uF 22uF

W7 DVSS VCCK_VPROC R15

Y7 AVSS18_WBG VCCK_VPROC P15

AB6 AVSS18_WBG VCCK_VPROC R14

AB8 AVSS18_WBG VCCK_VPROC R13

AC3 R12

AC5

AVSS18_WBG

AVSS18_WBG

VCCK_VPROC

VCCK_VPROC R16 Bottom cap 1st cap group

AC7 AVSS18_WBG VCCK_VPROC R17

AD4 AVSS18_WBG VCCK_VPROC T14

AE3 AVSS18_WBG VCCK_VPROC T15

VCCK_VPROC U15

VCCK_VPROC U16

HT107

VCCK_VPROC V15

W20 DVSS VCCK_VPROC V16

GND_VPROC_FB [3]

To MT6323 GND_VPROC_FB pin

U20 HT103

DVSS

V20 DVSS

VPROC_FB [3,4]

To MT6323 VPROC_FB pin

V21 DVSS DVSS M15

U21 DVSS DVSS N21 (1)VPROC_BB, GND pin of 1st cap group should be laid differential

W21 P10

Y20

DVSS DVSS

P11 pair with ground shielding remote sense to PMIC

AVSS18_MD DVSS

Y21 AVSS18_MD DVSS P12

AA21 AVSS18_MD DVSS P13 (2)R107 & R103 must be close to 1st cap group.

AB21 P16

U17

AVSS18_MD DVSS

P17 If you want to remove them,

DVSS DVSS

U18 DVSS DVSS L18 please make sure the VPROC_FB/GND_VPROC_FB must connect from 1st cap. group of VPROC

For low-power testing proposal. DVSS M14

A2 AVSS18_MEMPLL DVSS M13

It can be cancel for cost-down proposal R24 M12

AVSS33_USB DVSS

AE21 AVDD18_MD DVDD18_MIPITX L2

VIO18_PMU VIO18_PMU

R105 0

AE19 AVDD18_AP

DVDD18_MIPIIO G1

VTCXO_PMU

AE22 AVDD28_DAC

C111 C113 For low-power testing proposal.

AE18 DVDD18_PLLGP AVDD33_USB T24

A3 P26

VUSB_PMU

VIO18_PMU 100nF 100nF It can be cancel for cost-down proposal

VIO18_PMU AVDD18_MEMPLL AVDD18_USB

R106 0

AC21 AVSS18_MD

VIO18_PMU

AD22 AVSS18_MD DVSS18_MIPIIO H4

C112 AG26 AVSS18_MD DVSS18_MIPIIO H5 For low-power testing proposal.

V17 DVSS DVSS18_MIPIIO J5

V18 J7 C120 C119

It can be cancel for cost-down proposal

100nF DVSS DVSS18_MIPIIO

AA18 AVSS18_AP DVSS18_MIPITX L4

C108 C109 C110 AB19 AVSS18_AP DVSS18_MIPITX M7

100nF 1uF

DVSS18_MIPITX M8

AF3 AVSS18_WBG DVSS18_MIPITX N3

100nF 100nF 100nF

AG1 AVSS18_WBG

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

DVSS

T12

J21

M16

K21

M17

H12

H20

H17

H14

V14

MT6592

MT6582 R119=NF, R101=0, R102=NF, R120=NF, R110=0

MT6592 R119=0, R101=NF, R102=0, R120=0, R110=NF

MT6582 C135, C137, 可以NF

MT6592 C135=22uF, C137=22uF

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 01_MT6582_POWER SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 1 OF 33

U201-D

ED31 C26 RDQ31 RCS0_B B7 ECS0_B [6]

U201-A ED30 C24 RDQ30 RCS1_B B6 ECS1_B [6]

ED29 A25 RDQ29

AF22 AB24 ED28 B25 RDQ28 RCKE B5

TX_BBIP UL_I_P BPI_BUS0 ASM_VCTRL_A DVDD12_EMI ECKE [6]

AF21 AB23 ED27 B26 RDQ27

TX_BBIN UL_I_N BPI_BUS1

DVDD28_BPI ASM_VCTRL_B

AG20 AD25 ED26 B23 RDQ26

TX_BBQP UL_Q_P BPI_BUS2 ASM_VCTRL_C

AF20 AC24 ED25 A23 RDQ25 RDQM0 D16 EDQM0

TX_BBQN UL_Q_N BPI_BUS3 WG_GGE_PA_ENABLE [6]

AC23 ED24 D25 RDQ24 RDQM1 D18 EDQM1 [6]

BPI_BUS4

AE25 ED23 A11 RDQ23 RDQM2 D10 EDQM2 [6]

BPI_BUS5

AD24 ED22 A14 RDQ22 RDQM3 D23 EDQM3 [6]

BPI_BUS6

2

A13

8.2K

AF16 ED21 RDQ21

BPI_BUS7 W_PA_B1_EN

100nF

C205

AA17 ED20 D12 RDQ20 RDQS0 F15 EDQS0 [6]

BPI_BUS8 W_PA_B2_EN

AD16 ED19 A10 RDQ19 RDQS1 F17 EDQS1 [6]

BPI_BUS9 W_PA_B5_EN

AG25 AC16 ED18 B13 RDQ18 RDQS2 F12

R209

RX_BBIP DL_I_P BPI_BUS10 W_PA_B8_EN EDQS2 [6]

1

AG24 AF15 ED17 C10 RDQ17 RDQS3 E20 EDQS3 [6]

RX_BBIN DL_I_N BPI_BUS11 TD_PA_B40_EN

1

AG22 AC17 ED16 B11 RDQ16

RX_BBQP DL_Q_P BPI_BUS12 SP3T_A

AG23 AB17 ED15 D22 RDQ15 RDQS0_B E15 EDQS0_B [6]

RX_BBQN DL_Q_N BPI_BUS13 SP3T_B

AC15 ED14 B20 RDQ14 RDQS1_B E17 EDQS1_B [6]

BPI_BUS14 RTC32K_BPI_BUS14 [25] [2,6] EVREF

Y15 ED13 D20 RDQ13 RDQS2_B E12 EDQS2_B [6]

BPI_BUS15

ED12 A22 F20

2

RDQ12 RDQS3_B

2

DVDD18_IO4 EDQS3_B [6]

2

ED11 C19 RDQ11

8.2K

1.0uF

C207

100nF

ED10 B19

C206

VM0 AG14 VM0 RDQ10

AF14 ED9 A20 RDQ9 RCLK0_B F9 EDCLK_B [6]

VM1 VM1

B21 E9

R211

ED8 RDQ8 RCLK0

1

EDCLK [6]

1

AD14 ED7 B16 RDQ7

1

BSI_EN BSI-A_EN

AF25 Y14 ED6 A17 RDQ6

VBIAS BSI_CLK BSI-A_CK

AE24 AB14 ED5 B18 RDQ5

WG_GGE_PA_VRAMP APC BSI_DATA0 BSI-A_DAT0

AA14 BSI-A_DAT1

ED4 A16 RDQ4 RA0 B8 EA0

BSI_DATA1

AE14 AC14 ED3 B15 RDQ3 RA1 B9 EA1

DCOC_FLAG TXBPI BSI_DATA2 BSI-A_DAT2

ED2 C15 RDQ2 RA2 D8 EA2

ED1 D14 RDQ1 RA3 A8 EA3

ED0 C14 RDQ0 RA4 A7 EA4

RA5 C7 EA5

RA6 A5 EA6

[2,6] EVREF F16 VREF RA7 D6 EA7

MT6592

RA8 C6 EA8

RA9 A4 EA9

T250

A1 TP_MEMPLL REXTDN B3

1

R221

54.9欧姆,1%,0402

MT6592 54.9

2

SCL0 [2,12]

U201-E

SDA0 [2,12]

SCL1 [2,4,13]

SDA1 [2,4,13] [12] MIPI_TCP M3 TCP LCM_RST U3 LRSTB [12]

SCL2 [2,18] [12] MIPI_TCN M4 TCN DSI_TE Y3 LPTE [12]

SDA2 [2,18] [12] MIPI_TDP0 M1 TDP0 DISP_PWM AD9 PWM [12]

[12] MIPI_TDN0

M2 TDN0

VIO18_PMU LTE_AP_RSTB [21,25] P2

[12] MIPI_TDP1 TDP1

T205 [12] MIPI_TDN1 N2 TDN1

LTE_PMU_EN_P [21,22]

MIPI_TDP2 P1 TDP2

MIPI_TDN2 R1 TDN2

UTXD3

MIPI_TDP3 N5 TDP3

T206 M5 TDN3

1

MIPI_TDN3

1

EINT18_HP

R218 2.2K

K6 B2

R217 2.2K

MIPI_RCP RCP CMMCLK CMMCLK [13]

[5] K5 B1

MIPI_RCN RCN CMPCLK CMPCLK [13]

MIPI_RDP0 L3 RDP0

MIPI_RDN0 K3 RDN0 CMDAT0 E2

CMDAT0 [13]

2

2

EINT14_CTP_RST [12] MIPI_RDP1 K1 F2

URXD2 RDP1 CMDAT1 CMDAT1 [13]

[21] URXD2 EINT_ACC [18] MIPI_RDN1 K2 RDN1

UTXD2

[21] UTXD2 MT6290_GPIO17 [24] MIPI_RDP2 J1 RDP2_

EINT17_IDDIG [14]

MIPI_RDN2 J2 RDN2_

[2,18] SCL2 MC1INSI [15] G2

[13] CMDAT5 RDP3_

[2,18] SDA2 T204 GPIO_CHG_EN [4] H2

URXD1 [13] CMDAT4 RDN3_

EINT20_GY [18]

T203 UTXD1 KCOL0 [17]

[13] CMDAT7 F5 RCP_A_

URXD0 KROW0 [17] G5

VIO18_PMU T202 UTXD0 [13] CMDAT6 RCN_A_

KCOL1 [17] [13] CMVSYNC G4 RDP0_A

T201 KROW1 [13] CMHSYNC G3 RDN0_A

KCOL2 [2,3] SYSRST_B [13] CMDAT3 J3 RDP1_A

AC11

AD10

AC10

AC13

AD13

AE10

AB13

AE13

AA13

AF10

GPIO93_DRVVBUS [4] H3

AG8

AD8

AC8

AC9

AD7

[13]

AA3

AB3

AE7

AA1

AA2

AB9

AE9

RDN1_A

R23

AF8

P23

P22

Y13

CMDAT2

T23

W2

U2

Y2

V2

U201-C

MT6605 OSC_EN (SRCLKENAI) need to default low

1

SCL0

SCL1

SCL2

SPI_MO

SPI_MI

UTXD0

UTXD1

UTXD2

UTXD3

SDA0

SDA1

SDA2

SPI_CS

SPI_CK

EINT11

EINT14

EINT15

EINT16

EINT17

EINT18

EINT19

EINT20

KPCOL0

KPCOL1

KPCOL2

N1

URXD0

URXD1

URXD2

URXD3

KPROW0

KPROW1

KPROW2

1

MIPI_VRT

VRT

for MT6605 TESTMODE boot-strap

1K

R212 1K

1

[29] CLK1_BB AF26 CLK26M R203

R210

MT6592

DVDD18_IO3 DVDD28_MD M25 SYSRST_B [2,3]

SYSRSTB

2

[3] RTC32K_CK

RTC32K_CK L25 RTC32K_CK 1.5K

2

R223 0

C208

TESTMODE AF11 M24

NF

[2,4,13] SCL1 R224 0 TESTMODE SRCLKENAI SRCLKENAI [21]

FSOURCE_P R5 FSOURCE_P SRCLKENA N25

[2,4,13] SDA1 SRCLKENA [3,4,21,29]

R4 DVDD18_EFUSE

N26 J23

[3] WATCHDOG_B WATCHDOG PWRAP_SPI0_CSN

H23

PMIC_SPI_CS [3] Close to MT6582

T209 PWRAP_SPI0_CK PMIC_SPI_SCK [3]

AF12 JTCK PWRAP_SPI0_MI J24 PMIC_SPI_MISO [3]

AE12 JTDO PWRAP_SPI0_MO H22

T210 PMIC_SPI_MOSI [3]

PWRAP_INT H24 EINT_PMIC [3]

VIO18_PMU

T211 AG11 JTDI

C208 are for ESD ehnhace proposal.

K26

T212 AF13

AUD_CLK_MOSI

K25

AUD_CLK [3] It can be cancel for cost-down proposal

JTMS AUD_DAT_MISO AUD_DAT_MISO [3]

5.1K AUD_DAT_MOSI J25 AUD_DAT_MOSI [3]

2 1 USB_VRT P25 USB_VRT

GPIO12 AG10 GPIO12

R201 R26 AF9

1

1

[14] USB_DP USB_DP GPIO13 GPIO13

Close to MT6582 R25 USB_DM

R220 2.2K

[14] USB_DM

90 Ohm

R219 2.2K

SIM1_SCLK L21

SIM1_SIO K23

differential L23

SIM1_SRST

L20

2

SIM2_SCLK

2

SIM2_SIO L24

[3] CHD_DP

N23 CHD_DP SIM2_SRST K24

[2,12] SCL0 N24 CHD_DM <Parallel Cam./MIPI CSI Mux Table>

[3] CHD_DM

[2,12] SDA0 EINT0 W22 EINT0_MT6333 [4]

EINT1 V22 EINT1_A

AA24

MIPI CSI IF Port Parallel Camera IF Port

[21,24] AP_WAKEMD_INT EINT2 EINT2_CTP [12] BAT_ID BAT_ID [2]

EINT3 V24 EINT3_SUB_CMRST

[2] AUX_IN0_NTC EINT4 W25 EINT4_SUB_CMPDN RDP2 CMDAT9

Y25

[2] AUX_IN1_NTC EINT5 EINT5_RSTB_FROM_LTE [21,25] RDN2 CMDAT8

EINT6 AA23

DVDD28_MD AA26 EINT6_M [18] RDP3 CMDAT5

EINT7 [21,23]

C202

C203

DVDD18_IO3 EINT7_SDIO_INTB_LTE

V5 I2S_BCK EINT8 AA25 RDN3 CMDAT4

U5 Y23 EINT8_AGPS_OUT_LTE [24]

I2S_LRCK EINT9 EINT9_MAINCAM_RST [13]

W5 Y22

I2S_DATA_IN EINT10 [13] RCP_A CMDAT7

100PF

100PF

EINT10_CMPDN

V23 AP_PCM_CK [21,24] For earpohne & MSDC hotplug EINT, RCN_A CMDAT6

PCM_CLK

Plasse reservr R336/NTC301 & R339/NTC302 PCM_RX V26 AP_PCM_RX [21,24] RDP0_A CMVSYNC

PCM_SYNC V25 AP_PCM_FSYNC [21,24] plase choose EINT[0:15] RDN0_A CMHSYNC

for thermal protection option AC19

AD19

AUX_IN0 PCM_TX U24

AP_PCM_TX [21,24] with HW de-bounce function.

AUX_IN1 RDP1_A CMDAT3

AF18

RDN1_A CMDAT2

AUX_XP

VIO18_PMU

[12] LCD_ID_ADC

AG17 AUX_XM

DVDD28_MSDC2 DVDD28_MSDC1 DVDD18_MSDC0

Notice : CMDAT1 CMDAT1

VIO18_PMU AF17 AUX_YP CMDAT0 CMDAT0

C204 100PF

AG16 AUX_YM Please choose EINT[0:15] with

HW debouce for

MSDC0_RSTB

MSDC2_DAT3

MSDC2_DAT2

MSDC2_DAT1

MSDC2_DAT0

MSDC1_DAT3

MSDC1_DAT2

MSDC1_DAT1

MSDC1_DAT0

MSDC0_DAT7

MSDC0_DAT6

MSDC0_DAT5

MSDC0_DAT4

MSDC0_DAT3

MSDC0_DAT2

MSDC0_DAT1

MSDC0_DAT0

REFP CMMCLK CMMCLK

MSDC2_CMD

MSDC1_CMD

MSDC0_CMD

[3] BAT_ID_ADC AG19

MSDC2_CLK

MSDC1_CLK

MSDC0_CLK

REFP

AF19 CMPCLK CMPCLK

AVSS_REFN

mechanism plug in/out related application.

39K

R222

100PF

C213

Ex: earphone, MSDC, SIM hot-plug

1uF

[2] AUX_IN0_NTC [2] AUX_IN1_NTC MT6592

C210

T2

T1

T5

T6

R7

T3

D3

C2

D2

E4

C3

E3

F22

F24

G24

G23

G22

D26

G25

E23

E26

E25

E24

区分硬件配置

NTC201

EMMC_RST [6]

10k

EMMC_CMD

注意ADC的最大输入电压为1.5V [6]

10K 10K EMMC_CLK

EMMC_DAT0

[6]

[6]

HT201

EMMC_DAT1 [6]

EMMC_DAT2 [6]

EMMC_DAT3 [6]

EMMC_DAT4 [6]

EMMC_DAT5 [6]

EMMC_DAT6 [6]

EMMC_DAT7 [6]

C213 Close to MT6582

AF19 should connect to C213.2 first, MC1CM [15]

[15]

MC1CK

than connect to GND by via MC1DA0 [15]

MC1DA1 [15]

MC1DA2 [15]

MC1DA3 [15]

MC2CM [21,23]

MC2CK [21,23]

TITLE: <TITLE> REV: <REV>

MC2DA0 [21,23]

MC2DA1 [21,23] DOCUMENT NO.: 02_MT6582_BASEBAND SIZED: A1

MC2DA2 [21,23]

MC2DA3 [21,23] DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 2 OF 33

Regulator Output Voltage(V) Output Current(mA) Input Decoupling Output Decoupling Notes

VPROC 0.7~1.4 2800 >10uF L=0.68uH,C=10uF*4 Total outptu cap>40uF

VSYS 2.2 1200 >10uF L=0.68uH,C=10uF*2 Total outptu cap>20uF

VPA 0.5~3.4 600 >4.7uF L=2.2uH,C=2.2uF+2.2uF Output cap range 4.4uF +/-20%

LDO Output Voltage(V) Output Current(mA) Input Decoupling Output Decoupling Notes

VM 1.24 /1.39/1.54/1.84 700 10uF -20%~+20% Far-end bypass cap

VRF18 1.825 200 1uF -20%~+200% Far-end bypass cap

VIO18 1.8 300 4.7uF -20%~+200% Far-end bypass cap

VCN18 1.8 120 1uF -20%~+20% Far-end bypass cap

VCAMD 1.2 /1.3/1.5/1.8 150 1uF -20%~+20% Far-end bypass cap

VCAM_IO 1.8 100 1uF -20%~+20% Far-end bypass cap

VGP3 1.2 /1.3/1.5/1.8 200 1uF -20%~+20% Far-end bypass cap

VA 2.8 150 1uF -20%~+20% Far-end bypass cap

VTCXO 2.8 40 1uF -20%~+20% Far-end bypass cap

VCN28 2.8 30 1uF -20%~+20% Far-end bypass cap

VCAMA 2.8 150 3.2uF -20%~+20% 1uF near-end ,2.2uF Far-end bypass cap

240(MT6323)

VCN33 3.3/3.4/3.5/3.6 4.7uF -20%~+20% Far-end bypass cap

350(MT6322)

VIO28 2.8 200 2.2uF -20%~+200% Far-end bypass cap

VUSB 3.3 20 1uF -20%~+20% Far-end bypass cap

VMC 1.8 /3.3 100 1uF -20%~+20% Far-end bypass cap

VMCH 3.0 /3.3 400 2.2uF -20%~+20% Far-end bypass cap

VEMC_3V3 3.0 /3.3 400 4.7uF -20%~+20% Far-end bypass cap

1.2/1.3/1.5/1.8 /2.0

VCAM_AF 100 1uF -20%~+20% Far-end bypass cap

2.8/3.0/3.3

VSIM1 1.8 /3.0 50 1uF -20%~+20% Far-end bypass cap

VSIM2 1.8 /3.0 50 1uF -20%~+20% Far-end bypass cap

1.2/1.3/1.5/1.8/2.0

VGP1 100 1uF -20%~+20% Far-end bypass cap

2.8 /3.0/3.3

VGP2 1.2/1.3/1.5/1.8/2.0

100 1uF -20%~+20% Far-end bypass cap

2.5 /2.8/3.0

VIBR 1.2 /1.3/1.5/1.8/2.0

100 1uF -20%~+20% Far-end bypass cap

2.8/3.0/3.3

VDIG18 1.8 20 1uF -20%~+20% Far-end bypass cap

VRTC 2.8 2 0.1uF to 1000uF -20%~+20% Far-end bypass cap

U301

Before you select BJT , please take power dissipation into consideration.

BGA145-5.8X5.8-0.4E0.25B(MT6323)

Refer to MT6323 design notice

SPK_P K1 AU_SPKP[5]

SPK_N L1 AU_SPKN[5]

VBAT C313 P1

VBAT VBAT_SPK

L2 GND_SPK AU_HSP H1 AU_HSP[5]

2.2uF AU_HSN G1 AU_HSN[5]

H4

Charger MICBIAS0

MICBIAS1

F2

G2

AU_MICBIAS0

AU_MICBIAS1

AU_HPL

AU_HPR J4

AU_HPL

AU_HPR

[5]

[5]

1.0uF

C312

[5] AU_VIN0_P E4 AU_VIN0_P ISINK0 E9 LED_RED

F4 AUDIO DRIVER C9

[5] AU_VIN0_N AU_VIN0_N ISINK1 LED_GREEN

VBUS E10

ISINK2 LED_BLUE

[5] AU_VIN1_P

[5] AU_VIN1_N

G3

G4

AU_VIN1_P

AU_VIN1_N

ISINK3 C10 ISINK3

C356,C357,C358,BUCK电路输出端的小电容

VA_PMU VA_PMU AU_VIN2_P

AU_VIN2_N

D2

D1

AU_VIN2_P

AU_VIN2_N

请选择耐压值10V以上的

1. Close to Battery Connector. J2 AVDD28_ABB Please use inductor recommand by MTK

1.0uF

(Rsense (R328) <10mm) D3 AVDD28_AUXADC VPROC_PMU

R329 H2 GND_ABB Refer to MT6323 design notice VPROC_PMU[1,3,4]

C326

2. Main path should be 40mil. VCDT[3]

4.7uF

C333

(VBUS -> U303's E, -> U303's C -> R328 -> VBAT) 330K VCDT rating: 1.268V

R324

3. Star connection from R328 to BAT Connector [5] ACCDET E2 ACCDET BUCK OUTPUT VPROC_SW

1.0uF

C14

C329

VPROC L301

1uF

cap rating depends on 39K E1 D14 0.68UH

CLK_26M_MT6323 CLK26M VPROC

E14

C327

Phone OVP spec. [29] VPROC

40mils

C356

VPROC_FB B12 NF VPROC_FB [1,4]

ISENSE/BSTSNS 4mil CHARGER C12 GND_VPROC_FB[1]

10

GND_VPROC_FB

9

8

7

1

4

BATSNS P13

POWER-NFET+PNP-MI5809

R331 [6] BATSNS[3] BATSNS

differential to Rsense

C

C

C

C

D

D

CHR_LDO[3] ISENSE[3] ISENSE P12 ISENSE VPA A14

BAT_ON[3] BAT_ON K3 B14 VPA_SW VPA_PMU

40mils BATON VPA

3.3K VCDT[3] VCDT

VDRV

A12

M13

VCDT

D12 VPA for WCDMA

U302

VDRV[3] VDRV VPA_FB

C357

CHR_LDO[3] CHR_LDO N13 CHRLDO NF

VSYS_SW

100PF

L303 0.68UH

VSYS H14 VSYS_PMU

G

E

B

S

1.0uF

C316

CONTROL SIGNAL

1.0uF

C317

2

3

6

5

ISENSE_R R316 1K

[17] PWRKEY M2 C358

[4] PWRKEY

C302

R303 0 A1 NF

[2] WATCHDOG_B SYSRSTB

40mils K4 RESETB

[2] SYSRST_B ALDO OUTPUT

A9 FSOURCE VA M3 VA_PMU

[2] EINT_PMIC A7 INT

40mils 4mil Close to PMIC N12 N3 VCN_2V8_PMU

[4] EXT_PMIC_EN EXT_PMIC_EN VCN28

1

HT303 L4 VTCXO_PMU

ISENSE[3] VTCXO VEMC_3V3_PMU VA_PMU DVDD12_EMI

[3] CHR_LDO

SR0805

N2

[3] VDRV

0.02

PMU_TESTMODE

R328

Rsense Differential BATSNS[3] P3 VCAMA_PMU

VCAMA

HT304 [2] AUD_DAT_MOSI E7 M6 VCN_3V3_PMU

AUD_MOSI VCN33

[2] AUD_CLK E8 AUD_CLK AVDD33_RTC C3 VRTC

2

4mil B6 C331

40mils [2] AUD_DAT_MISO AUD_MISO

TP-1.0MM TP-1.0MM TP-1.0MMTP-1.0MM C355

[2,4,21,29]

SRCLKENA A2

100nF

TP309 TP310 TP312 TP313 SRCLKEN

C354

100nF

470nF

1.0uF

AUXADC_REF DLDO OUTPUT

0.47uF

C332

T301

AUXADC_REF[3] FCHR_ENB[3] FCHR_ENB[3] M1 FCHR_ENB

TP-1.0MM 1.0uF DVDD12_EMI

VM J13

TP311

C353

[2] PMIC_SPI_SCK D9 SPI_CLK VRF18 H11 VRF18_PMU

16.9K 1% [2] PMIC_SPI_CS B7 SPI_CSN VIO18 L12 VIO18_PMU

BATTERY VA_PMU [3] [2] PMIC_SPI_MOSI D8 SPI_MOSI VIO28 M4 VIO28_PMU

R334

16.9K

1

1

1

1% [2] PMIC_SPI_MISO B8 SPI_MISO VCN18 J12 VCN18_PMU

VBAT

VCAMD K14 VCAMD_PMU

CONNECTOR

1

VCAM_IO L13 VCAMD_IO_PMU

CON302 40mils F13 VBAT INPUT

40mils VBAT_VPROC

1 VBAT 80mil 40mil F14 VBAT_VPROC

2 R317 VBAT [3,4,12,21,22,30,31] G13 VBAT_VPROC VEMC_3V3 P7 VEMC_3V3_PMU

30mil (4mil if VPA no use) VBAT A13 L6

3 BAT_ON [3] VBAT_VPA VMC VMC_PMU

4 VMCH P4 VMCH_PMU

1K 20mil VBAT H13 N6 VUSB_PMU

VBAT_VSYS VUSB

5 P8 VBAT_LDOS3 VSIM1 P9 VSIM1_PMU

6

Add Zenar Diode500mW 20mil VBAT P6 N9 VSIM2_PMU

R335

VBAT_LDOS3 VSIM2

22uF

C310

27K

10uF_NF

Place on the path 20mil VBAT P5 VBAT_LDOS2 VGP1 L8 VGP1_PMU

C330

R334,R335 must to be close to VBAT P2

27PF

C335

20mil VBAT_LDOS1

from VBAT to IC

1

BATTCON-R6593004-20005A VIBR M7 VIBR_PMU

D302

PMIC AUXADC_REF pin VSYS_PMU 20mil J14 AVDD22_BUCK VGP2 N8 VGP2_PMU

(Battery connector M14 L14 VGP3_PMU

AVDD22_BUCK VGP3

or test point or IO N7 VCAM_AF_PMU

VR301

VR302

DVDD18_DIG_PMIC VCAM_AF

2

connector) A8 DVDD18_DIG

VF : 4.85V~5.36V

VIO18_PMU VIO18_PMU A5 DVDD18_IO

VIO18_PMU

Based on your system level design , if

if battery NTC is 10kohm, R334=16.9K, R335=27K Between IC and IO port AUXADC VREF

better ESD performance is needed on [3] AUXADC_REF AUXADC_REF C2 AUXADC_VREF18

R

e

f

e

r

t

o

M

T

6

3

2

3

H

W

d

e

s

i

g

n

n

o

t

i

c

e

R302 if battery NTC is 47kohm, R334=61.9K, R335=100K AUXADC_TSX AUXADC_TSX B1 AUXADC_AUXIN_GPS VREF P14

TP-1.0MM your system, please refer to ESD GND_AUXADC B2 AVSS28_AUXADC

TP305

100nF

GND_AUXADC

C320

performance enhance proposal CLOSE Batconnector dedicate VSS ball, must return to cap then to main GND:

Refer to MT6323 design C323

1.0uF

C322

BC 1.1

1. GND_VREF(N14) => C320

47K

notice for Zener selection 100nF

[2] CHD_DM A10 CHG_DM GND_VREF N14

HT305

1

[2] CHD_DP A11 CHG_DP

10uF

10uF

R301

Based on your system level design , if

RTC

4.7uF

4.7uF

BAT_ID_ADC [2] X301

C301

C350

RTC_32K1V8 D5 RTC32K_CK [2]

HT301

SIM LVS RTC

1K better EOS performance is needed on your C322 must to be close RTC_32K2V8 C4

RTC 32K : X301+C324+C319=> mount, R333=> NC

C303

C305 B5 A3 32K_IN

SIM1_SCLK SIM1_AP_SCLK XIN

system, please refer to EOS performance to PMIC AUXADC_TSX pin M11 A4 32K_OUT

0.01uF

SIM1_SIO SIMLS1_AP_SIO XOUT 32K-less: X301+C324=> remove, C319+R333=> 0R

C339

enhance proposal E6 1 2

SIM1_SRST SIM1_AP_SRST

R305

100K

VR305

10uF

10uF

1uF

SIM2_SCLK C5 B10

1uF

1.0uF

SIM2_AP_SCLK GND_ISINK

K11 SIMLS2_AP_SIO GND_VSYS G11

18PF

SIM2_SIO

C324

18PF

C319

D6 SIM2_AP_SRST GND_VPA E13

C304

SIM2_SRST

Connect TSX/XTAL GND E11

C306

GND_VPROC XTAL-32.768K-KYOCERA

C307

C308

C309

SCLK M9 SIMLS1_SCLK GND_VPROC F11

to AUXADC_GND first SIO N11 F10

SIMLS1_SIO GND_VPROC

than connect to main GND SRST M10 SIMLS1_SRST

GND_LDO K6

SCLK2 K9 SIMLS2_SCLK GND_LDO K8

L11

HT302

SIO2 SIMLS2_SIO

SRST2 K10 SIMLS2_SRST GND_LDO F5 Close to chip

GND_LDO F6

GND_LDO F7 DCXO_32K

F8

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

refer to system analog LDO GND_LDO F9

GND_LDO G5

performance improve proposal GND_LDO G6

H8

H5

G7

H9

H7

H6

G9

G8

J9

J8

J7

J6

J10

H10

MT6323

VRTC

Refer to MT6323 design notice

for Buck GND layout rule

R312

1K

Vibra VIBR_PMU

Refer to GPS co-clock layout rule

22uF

C325

1

C311

1uF

3

NP

VIB-GS-2701

CON301

2

==> for longer RTC time sustain after battery remove,

please refer to RTC design notice

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 03_MT6323_PMIC_AUDIO SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 3 OF 33

当使用Switching charger :Rsense R328 use 56m ohm

VBUS VBUS_1

U302 placement, please be close to MT6322

GND GND

I2C Address

L307 placement, please be close to L301

[3,4,12,21,22,30,31]

FAN53555 : 0xC0

VBUS_1

NCP6335D: 0x1C

VBAT

VBAT

[10] ANT_SEL1

C337 must to be close

[10] ANT_SEL2 to U302

40mil 40mil

OTG-BOOST

GND

[4] VPROC_PMU

[2,4,13] SDA1 As short as possible and L307 as close as possible to L301,

[2,4,13] SCL1

NC : FN5405/FN54015 then connect to VPROC_PMU

GND

10nF : BQ24153

[2] GPIO_CHG_EN ISENSE_R ISENSE_R [3,4]

[2] GPIO93_DRVVBUS

BATSNS_L 40mil

VBAT [3,4,12,21,22,30,31]

[2,4,13] SDA1

[2,4,13] SCL1 VPROC_FB[1,3]

VPROC_FB should be ground shielding.

OTG-BOOST

[4]

GND GND GND

GND GND

If switching charger is used:

FN5405 R410=10K,R412=NF, C402=NF (1) R1801~R1805, C1801~C1806, L1801, U1801 are needed

(2) U303, U304 change to NC

FN5402 R410=NF, R412=10K,C402=NF (3) R328 change to 56m Ohm

BQ24158 R410=10K,R412=NF, C402=10nF

External DC-DC for VPROC

Switching Charger

EXT_PMIC

MT6333 switching charger function de-feature (Need to add external SWCHR)

Change notice:

Page 4

1. Delete R813/C839/U3/R817/R1812/C1815/R335 MT6333 I2C Address: 0xD6, 0xD7

2. Change C1809 to 1uf

3. Add R341/C1810 for ESD protection 10V L1801 / L304 / L305 / L306

4. Delete ISENSE/BATSNS net

25V rating Please use inductor recommand by MTK

5. Change C1806 location (close to MT6333)

6. Add U402 and related circuits Refer to MT6333 design notice

25mil 40mil 40mil

40mil

25mil

40mil

VLED

40mil 40mil

VBAT

VIO18_PMU 40mil

25mil

Close to L1801

BUCK1_SW

[2] EINT0_MT6333 VM12_SW_PMU

BUCK1_FB

BUCK1_FB [1,4]

[2,4,13] SCL1

[2,4,13] SDA1

Need pull-up resistor to VIO18

BUCK2_SW

[2,3,21,29]

SRCLKENA VCORE_SW_PMU

[3] EXT_PMIC_EN

VCORE_SW_FB

C338 / C339 are for VMEM_FB / VCORE_FB decoupling proposal.

It can be cancel for cost-down proposal

VRF_SW_PMU

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 04_POWER_SWCHR_EXT_PMIC SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 4 OF 33

Earphone Audio close to IC

same power domain

close to connector

R505 470K

VIO18_PMU

R506 47K

[2] EINT18_HP

Reserve bead+C footprint for FM

performance tuning

NF

NF

Based on your system level design , if better BEAD501

AUDIO-EAR-PJES-050-1-G-BLK

C553

C552

[5] HP_MIC HP_MIC-1 [5]

desense performance is needed on your

1800ohm 6

system , please refer to desense BEAD503 1800ohm 22uF 100 BEAD502 5

C519 R507 HP_MP3L [5]HP_MP3R-1

[3] AU_HPL HP_MP3L-1 [5] 4

performance enhance proposal [5]EAR_DET

Receiver [3] AU_HPR

BEAD504 1800ohm

C520 22uF R508 100

1800ohm

BEAD505 EAR_DET [5]

HP_MP3R-1 [5] [5] HP_MP3L-1

3

1

VR502

HP_MP3R [5]FM_ANT-1

1800ohm 2

33PF

33PF

close to IC close to connector [5] HP_MIC-1

FM_ANT-1 [5]

CON501

C506

33PF

C522

C521

1

R520 CON503

VR501

[3] AU_HSP[3]

AUDIO-RECIEVER-1506-S3001/11.5

0

2

100PF

C505

470

470

R521 R501

[3] AU_HSN[3] 1 2 FM_ANT[10]

0 0

R530

R531

L502

C504

33PF

Based on your system level design , if better ESD

VR503

2.5Kohm

performance is needed on your system, please

refer to ESD performance enhance proposal R502

1 2 FM_RX_N_6572[10]

0

VR506

VR505

VR504

Single via to GND plane

PAD-2.0X2.0SS

PAD-2.0X2.0

XJ504

XJ501

XJ502

XJ503

1

1

220ohm

[3] AU_SPKP

SPK_P

BEAD506

小板喇叭

100PF

C503

220ohm

[3] AU_SPKN

SPK_N

BEAD507

VR511

33PF

33PF

VR510

C501

C502

MICBIAS1

Earphone MICPHONE

1K

Close to BB Close to MIC GND of C(4.7uF) and headset

should tie together and single

R511

[3] AU_VIN1_N

C550 100nF AU_VIN1_N1 C554 4.7uF via to GND

GND plane

C526 R518

Close to EarJack

1.5K

33PF

100PF

C525

C551

33PF

C560 100nF

[3] AU_VIN1_P HP_MIC [5]

R519

together then single

1K

Handset Microphone 1 [3] ACCDET

via to main GND

MICBIAS0

TP-1.0MM

VR508

TP501

R532

1K

TP-1.0MM

TP502

Close to Close to

Close to

MIC MIC

BB

1

1.5K

1

R515

Analog MIC Analog MIC

C511 CON502

[3] AU_VIN0_P

C513 R522 0 1

100nF

100PF

C508

R523 0 2

4.7uF

C512

[3] AU_VIN0_N AUDIO-MIC-SMT4013-PRJ7665

33PF

33PF

100nF

1.5K

R516

C509

C510

VR509

if you use digital MIC,

please change cap

R517

1K

(C511,C512) to 1.0uF

together then single via to main GND TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 05_AUDIO SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 5 OF 33

eMMC+LPDDR2

162 Ball, 0.5mm pitch R618 0

VIO18_PMU DVDD18_EMI

VDD1=1.8V

VDD2=1.20V

VDDCA=1.2V

VDDQ= 1.20V

VDD1 : Core 1

DVDD18_EMI

U601

EA0 U3 CA0 VDD1 E6

EA1 T3 F1

100nF

CA1 VDD1

EA2 R3 V1 VDD2 : Core 2

C642 2.2uF

CA2 VDD1 DVDD12_EMI

EA3 R2 CA3 VDD1 W6

EA4 R1 CA4

C631

EA5 K2 CA5 VDD2 E5

EA6 J2 CA6 VDD2 G2

EA7 J3 CA7 VDD2 K1 GND GND

EA8 H3 CA8 VDD2 M7

EA9 H2 CA9 VDD2 U2

VDD2 W5

ED0 T8 DQ0

ED1 R8 DQ1 VDDQ F7

ED2 R7 DQ2 VDDQ F10

ED3 R9 DQ3 VDDQ G5

Power

100nF

100nF

100nF

100nF

100nF

ED4 R6 H9

C601

C627

C629

C628

C630

DQ4 VDDQ

ED5 P7 J10

2.2uF

4.7uF

C640

C639

DQ5 VDDQ

ED6 P8 DQ6 VDDQ L6

ED7 P9 DQ7 VDDQ M6

ED8 K9 DQ8 VDDQ N6

ED9 K8 DQ9 VDDQ R10

ED10 K7 DQ10 VDDQ T9 GND GND GND GND GND GND

ED11 J6 DQ11 VDDQ U5

ED12 J9 DQ12 VDDQ V7

ED13 J7 DQ13 VDDQ V10

ED14 J8 DQ14

ED15 H8 DQ15 VDDCA J1

ED16 W7 L1 1. VCC : Core Voltage 2.7v ~ 3.6v

DQ16 VDDCA

ED17 U6 DQ17 VDDCA T2 2. VCCQ : IO Voltage 1.7v~1.95v (low voltage range)

ED18 W8 DQ18 R612

ED19 T5 DQ19 VCC A8 EMMC_VCC

VEMC_3V3_PMU

ED20 U7 DQ20 VCC B2

ED21 W9 B8 EMMC_VCCQ 0

DQ21 VCCQ VIO18_PMU

ED22 V8 DQ22 VDDI A5

R613

100nF

ED23 T6 R614 0 0

DQ23

1uF

ED24 H6 DQ24 CLKM B5 EMMC_CLK [2]

0.22uF

100nF

ED25 F8 C1

2.2uF

C624

C637

C643

DQ25 RST EMMC_RST [2]

ED26 E9 C5

4.7uF

C636

DQ26 CMD EMMC_CMD [2]

C623

eMMC

C634

ED27 G7 DQ27

ED28 H5 DQ28 DAT7 B4 EMMC_DAT7 [2]

ED29 E8 DQ29 DAT6 A4 EMMC_DAT6 [2] GND

ED30 G6 DQ30 DAT5 A6 EMMC_DAT5 [2] GND GND GND GND

ED31 E7 DQ31 DAT4 B6 EMMC_DAT4 [2]

R609 DAT3 A7 EMMC_DAT3 [2]

1 2 G3 B7

ZQ0 DAT2 EMMC_DAT2 [2]

1 2 F3 B3

240 ZQ1 DAT1 EMMC_DAT1 [2]

DAT0 A3 EMMC_DAT0 [2] Close to Memory

R610240

GND

F6 VSSQ CS0# P1 ECS0_B[2] Check MCP part's requirement

F9 VSSQ CS1# P2 ECS1_B[2]

G10 VSSQ

H10 VSSQ CKE0 N1 ECKE ECKE[2,6]

J5 VSSQ CKE1 N2 ECKE ECKE[2,6]

K10 VSSQ

M5 VSSQ CLK M3 EDCLK EDCLK[2]

P10 VSSQ CLK# L3 EDCLK_B EDCLK_B[2]

R5 VSSQ

T10 VSSQ DQS0 P6 EDQS0[2]

U10 VSSQ DQS0# P5 EDQS0_B[2]

V6 VSSQ DQS1 K6 EDQS1[2]

V9 VSSQ DQS1# K5 EDQS1_B[2]

DQS2 U8 EDQS2[2]

T1 VSSCA DQS2# U9 EDQS2_B[2]

M1 VSSCA DQS3 G8 EDQS3[2]

H1 VSSCA DQS3# G9 EDQS3_B[2]

B9 VSSM DM0 N5 EDQM0[2]

E1 VSSM DM1 L5 EDQM1[2]

F2 VSS LP-DDR2 DM2 T7 EDQM2[2]

F5 VSS DM3 H7 EDQM3[2]

G1 VSS

L2 VSS VREFCA K3 EVREF[2]

M8 VSS VREFDQ M9

U1 VSS

V2 VSS NC C2

V5 C4

100nF

VSS NC

C3 VSSQM NC C6

D1

4.7uF

C638

NC

A1 DNU NC D2

A2 DNU NC D3

C641

A9 DNU NC D4

A10 DNU NC D5

B1 DNU NC D6 GND GND

B10 DNU NC E2

E10 DNU NC E3

W1 DNU NC M2

W10 DNU NC N3

GND Y1 DNU NC P3

Y2 DNU NC V3

Y9 DNU NC W2

Y10 DNU NC W3

Hynix H9TP32A4GDMCPR;Micron MT29PZZZ4D4TKETF-25

BGA162-12X13.5-0.5PB0.27(H9TP32A8JDMCPR)

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 06_MEMORY_EMMC_LPDDR2 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 6 OF 33

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 07_RF_MT6166_TXVR_2G_B34_B39 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 7 OF 33

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 08_RF_MT6166_WCDMA SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 8 OF 33

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 09_RF_MT6166_B40 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 9 OF 33

X1001

XTAL-CRYSTAL-26M-7L26002009

R1013 0 3 4

OUTPUT VCC VCN_2V8_PMU U201-F

WB_RSTB AF6 WB_RSTB AVDD18_WBG AE4 AVDD18_WBG

2 1 XIN_WBG AD6 XO_IN

GND GND

C1046

C1022

100nF

AF5 GPS_RX_QN

1.0uF

[10] XO_IN GPS_RXQN

GPS_RXQP AG5 GPS_RX_QP

FM_DATA Y10 F2W_DATA GPS_RXIN AG4 GPS_RX_IN

FM_CLK AA10 F2W_CLK GPS_RXIP AF4 GPS_RX_IP

SYSCLK_WCN WB_SCLK AG7 AF2 WB_TX_QN

WB_SCLK WB_TXQN

WB_SDATA AF7 WB_SDATA WB_TXQP AG2 WB_TX_QP

WB_SEN AE6 WB_SEN WB_TXIN AF1 WB_TX_IN

WB_TXIP AE1 WB_TX_IP

WB_CTRL0 Y6 WB_CRTL0 WB_RXQN AE2 WB_RX_QN

WB_CTRL1 AA6 WB_CRTL1 WB_RXQP AD2 WB_RX_QP

WB_CTRL2 AA5 WB_CRTL2 WB_RXIN AC2 WB_RX_IN

WB_CTRL3 AA4 WB_CRTL3 WB_RXIP AC1 WB_RX_IP

WB_CTRL4 AB5 ANT_SEL0 [10]

WB_CRTL4

WB_CTRL5 AB4 WB_CRTL5

AB25 ANT_SEL0 T1002

ANT_SEL0

WIFI/BT/GPS Single ANT Ref.

50 Ohm AC26 ANT_SEL1

ANT_SEL1

ANT_SEL2 AC25 ANT_SEL2 T1001

T1003

MT6592

Debug usage

ANT1001 ANT1002

1

L1020

NF

WB_CTRL3 [10]

L1031

NF

U1003

2

RF-SAW-885033

GND

GND

WB_CTRL2 [10]

1 [10] WB_CTRL4

IN

GND

WB_CTRL1 [10]

OUT

[10] WB_CTRL5

Close to MT6572

U1007

5

WB_CTRL0 [10]

6 GND WIFI 1

[10] AVDD18_WB

0

WB_RX_IP [10] HT1004

0

5 2 [10]AVDD18_WBG VCN18_PMU

1 2 ANT GND

1 2

R1006

R1005 WB_RX_IN [10]

C1042

4 3 2 1

NF

GND GPS

NF

C1026 18PF

L1004

L1015

NF

30

29

28

27

26

25

24

23

22

21

RF-SAW-DP1608-V1524CAT

WB_RX_IP

WB_RX_IN

W_LNA_EXT

WB_CTRL5

WB_CTRL4

WB_CTRL3

WB_CTRL2

WB_CTRL1

WB_CTRL0

AVDD18_WBT

GND

50 Ohm 31 WB_GPS_RF_IN WB_RX_QP 20 WB_RX_QP [10]

[10] AVDD18_WB

HT1002

VCN18_PMU

50 Ohm 32 19

GPS_DPX_RFOUT WB_RX_QN WB_RX_QN [10]

[10] AVDD18_GPS HT1003

VCN18_PMU

Based on your system level design , if

better WiFi TX performance is needed on AVDD33_WB 33 AVDD33_WBT WB_TX_IP 18 WB_TX_IP [10]

[10]

your system, please refer to WiFi Star Conn

100nF

C1007

performance enhance proposal 34 17 for WB/GPS/WBG 1V8

NC WB_TX_IN WB_TX_IN [10]

50 Ohm

U1000 C1008

C1005

1nF

C1006

35 16

1.0uF

NC WB_TX_QP WB_TX_QP [10]

MQFN40-5X5-0.4E(MT6627) 100PF

VCN_2V8_PMU_FM 36 AVDD28_FM WB_TX_QN 15 WB_TX_QN [10]

[10]

钢网做屏蔽处理

37 FM_LANT_N GPS_RX_IP 14 GPS_RX_IP [10]

[5] FM_RX_N_6572 FM_RX_N_6572

L1011

[5] FM_ANT FM_LANT_P

38 FM_LANT_P GPS_RX_IN 13 GPS_RX_IN [10]

82nH 91NH

L1012

100NH

39 12

50 Ohm GPS_RFIN GPS_RX_QP GPS_RX_QP [10] refer to FM desense performance

91NH

enhance proposal

AVDD18_GPS 40 AVDD18_GPS GPS_RX_QN 11 GPS_RX_QN [10]

[10] FB1010

AVDD28_FSOURCE

VCN_2V8_PMU_FM VCN_2V8_PMU

41

R1010

DVSS 600ohm

0

L1032

NF

0.01uF

F2W_DATA

C1002

F2W_CLK

FM_DBG

U1002

HRST_B

SDATA

XO_IN

CEXT

SCLK

SEN

U1004 1 6

GND RFOUT

R1032 MT6627 SMD QFN40

2 5

1

9

4

10

C1031 GND EN ANT_SEL0 [10]

L1001

0

1 4 3 4

IN OUT RFIN VDD

Close to MT6627

GND

GND

GND

33PF 9.1nH 1.0uF

C1025

GPS-LNA-RDALN16

C1030

HT1001

NF

2

[10]AVDD33_WB VCN_3V3_PMU

100PF WB_RSTB

4.7uF

C1004 100PF

C10111.0uF100PF

2.2uF

[10] XO_IN

0.22uF

C1028

[10]

C1020

R1002 0

C1003

C1041

C1040

NF

C1012

[10] FM_DATA

VCN_2V8_PMU [3,10]

[10] FM_CLK

Based on your system level design , if

better GPS performance is needed on

[10] WB_SCLK

your system, please refer to GPS

performance enhance proposal [10]WB_SDATA

[10] WB_SEN

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 10_WIFI_BT_GPS_FM_MT6627 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 10 OF 33

NFC

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 11_NFC SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 11 OF 33

默认3*3封装

TP-1.0MM

<=8LEDs,可换2520封装

TP-1.0MM TP-1.0MM TP-1.0MM TP-1.0MM TP-1.0MM

TP1206 VBAT

TP1205 TP1204 TP1203 TP1202 TP1201

CTP

FB1201 D1201

L1201

1

R1205 10K_NF 10uH

1

1

GND

30ohm

VIO18_PMU VIO18_PMU C1233 FB1202

R1218 1K

[2] EINT14_CTP_RST CTP_GPIO_CTP_RSTB [12] LEDA [12]

R1217 1K U1201

[2] EINT2_CTP CTP_EINT_CTP [12] 2.2uF 600ohm

6 1

[3,12] VGP1_PMU VGP1_PMU [3,12] GND

VIN SW C1238 50V C1239

GND 2 GND NC/OVP/VOUT

5

R1206 0

[2] SDA0 CTP_SDA_1 [12] R1202 1uF 47PF

4 3

[2] PWM EN FB

R1204 0

[2] SCL0 CTP_SCL_1 [12] 0 GND GND

LED-DRIVER-ET5119A

R1212

C1222

NF

J1201 R1208

NF

LEDK [12]

100K

1

[12] CTP_GPIO_CTP_RSTB

2

[12] CTP_EINT_CTP R1203

3 C1224

[3,12] VGP1_PMU

47PF

GND

[12]LCD_CABC 7.5

0.1uF

4

NF

1nF

2

[12] CTP_SCL_1

1nF

2

2

NF

VR1203

5

VR1205

[12] CTP_SDA_1

VR1204

VR1201

VR1202

GND 6 GND GND

C1215

1

C1207

C1214

1

1

C1212

1

C1213

1

ZIF-04-6298-006-000-883+

GND GND GND GND GND

Backlight LED Driver

Main LCM

LEDA [12]

47PF

C1203

ZIF-FH26-25S-0.3SHW

GND 27

26

R1207 1K 25

[2] LCD_ID_ADC

24

100PF

23

22

[12] LEDK

C1209

21

20

[12] LEDA

19

18

R1216 0 17

VIO28_PMU

R1215 0 16

VIO18_PMU

15

[2] LRSTB

R1201 33

100nF

14

100nF

LPTE

C1208 100nF

[2]

13

C1206

C1205

12

11

GND [12] LCD_CABC LCD_CABC

EMI1207 10

1 4 9

[2] MIPI_TCP

8

MIPI_TCN 2 3

[2]

EMI1209 7

1 4 6

[2] MIPI_TDP1

5

2 3

[2] MIPI_TDN1

EMI1208 4

3

1 4

[2] MIPI_TDP0 2

2 3

[2] MIPI_TDN0 1

J1202

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 12_LCD_CTP_SIDEKEY SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 12 OF 33

J1301

R1330 NF

VCAM_AF_PMU 25 28

C1319 26 27

NF 1 24

GND 2 23

3 22

R1306 [2,4] SDA1 CMDAT2-1 [13]

VCAMA_PMU 4 21 [13]

VCAMA CMDAT1-1

1.0uF

5 20

1.0uF

0 [2,4] SCL1 CMDAT3-1 [13]

6 19 VLED

[13] EINT9_MAINCAM_RST-1 CMDAT0-1 [13]

7 18

C1320

R1325 [13] CMVSYNC-1 CMDAT4-1 [13]

C1318

[3] VGP3_PMU 8 17

[13] EINT10_CMPDN-1 CMPCLK-1 [13]

VCAMD VCAMD_PMU

R1311

0

0

GND

[13] CMHSYNC-1

9

10

16

15

CMDAT5-1 [13] ELCH07-5070J5J7293910-N0

R1310 0 11 14

VCAM_IO VCAMD_IO_PMU CMDAT6-1 [13]

12 13 [13]

CMDAT7-1 CMMCLK_BTB

1.0uF

1.0uF

100PF

[13]

100PF

BTBS-BBR43-24KBJ03

NF

NF

NF

NF

9

1 5

[2] EINT9_MAINCAM_RST

C1342

EINT9_MAINCAM_RST-1 [13]

C1308

C1310

C1307

C1304

C1309

C1306

C1305

2 6

[2] CMVSYNC CMVSYNC-1 [13]

GND GND 3 7

[2] EINT10_CMPDN EINT10_CMPDN-1 [13]

4 8

[2] CMHSYNC CMHSYNC-1 [13]

EMI1301

10

EMI-ICVE10184E070R101FR

GND

R1302

CMPCLK CMPCLK-1 [13]

[2] 0

9

C1302

[2] 1 5

NF

CMDAT7 CMDAT7-1 [13]

[2] 2 6

CMDAT6 CMDAT6-1 [13]

3 7

OCP8111 R1315=68K R1317=0.22

[2] CMDAT5 CMDAT5-1 [13]

4 8

[2] CMDAT4 CMDAT4-1 [13]

EMI1302

10

EMI-ICVE10184E070R101FR

CMMCLK

[2]

0

R1301

C1301

NF

CMMCLK_BTB [13]

OCP8110 R1315=82K R1317=0.47

FLASH LED

9

1 5

[2] CMDAT3 CMDAT3-1 [13]

2 6

[2] CMDAT2 CMDAT2-1 [13]

3 7 [13]

[2] CMDAT1 CMDAT1-1

4 8 [13]

[2] CMDAT0 CMDAT0-1

EMI1303

10

EMI-ICVE10184E070R101FR

MAIN_camera

light sensor 0x90 Write(STK3171)

light sensor 0x46 Write (LTR-558ALS)

Main Camera / Sub Camera share power domain design

should double check the voltage level is compatible

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 13_CAMERA SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 13 OF 33

USB HS IF

TP-1.0MM

TP1401

R1406

TP-1.0MM TP-1.0MM

NF TP-1.0MM TP-1.0MM TP1403 TP1404

EMI1401 TP1405 TP1402

1

1 4

[2] USB_DM

90 ohm differential

1

2 3

1

1

[2] USB_DP

J1401

R1407 R1405 0 1

VBUS

2

NF

3

4

[2] UTXD0

R1401 1K 5

ESD-TVS-ESD5342N

2

USB-UAF95-05254-S135-A-CUS

DIODE-ZENER-WZD58L6V2

[2] EINT17_IDDIG

GND

VR1403

R1402 0_NF

1

2.2uF_NF

1

D1402

VR1401

D1401

C1405

VR1402

2

3

2

GND

GND

GND

华为项目请预留此二极管,有要求

1. 为方便软件调试打LOG,将UTXD0接至USB接口的Pin 4 ;

2. 如果有OTG功能, R708=0 欧姆

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 14_USB SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 14 OF 33

R1503 0

2 1

[21,22] LTE_USIMLV1_CLK

1R1511 2 0

[21,22] LTE_USIMLV1_RST

1 2 TP-1.0MM TP-1.0MM TP-1.0MM TP-1.0MM TP-1.0MM

[21,22] LTE_USIMLV1_DATA

TP1515 TP1501 TP1502 TP1503 TP1504

R1501 0

NF

NF

NF

C1503

C1505

C1504

J1501

1

1

25 28

26 27

VMCH_PMU

1 24

SIM1 2

3

23

22

MC1INSI [2]

4 21

R1510

R1512 0 5 20

0

[21,22] LTE_VSIM1

R1502 0 6 19

7 18

8 17

9 16

R1507 0 10 15 R1504 0 T卡clk需要保护

[2] MC1DA2 MC1CK [2]

R1508 0 R1505 0

[2]

[2]

MC1DA3

MC1CM

R1509 0

11

12

14

13 R1506 0

MC1DA0 [2]

MC1DA1 [2]

SD CARD

BTBS-BBR43-24KBJ03

C1502

2.2uF

C1508

C1507

C1506

2

NF

NF

NF

1

C1501

1uF

C1511

C1509

C1510

NF

NF

NF

1

TP1508 TP1507 TP1506 TP1505

TP1513 TP1512 TP1511 TP1509

TP-1.0MM TP-1.0MM TP-1.0MM TP-1.0MM

TP-1.0MM TP-1.0MM TP-1.0MM TP-1.0MM

GND

T-card ESD protection is optional depends on

T-card's type and position

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 15_DUAL_SIM SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 15 OF 33

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 16_MEMORY_CARD SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 16 OF 33

R1704 1K

[2] KCOL0 KCOL0' [17]

R1701 1K

[2] KCOL1 KCOL1' [17]

R1702 1K

[2] KROW0 KROW0' [17] HOLE-VIA2.4MM HOLE-VIA2.4MM HOLE-VIA2.4MM

HOLE-VIA2.4MM

TP-1.0MM TP-1.0MM HOLE1701 HOLE1703 HOLE1705 HOLE1706

TP-1.0MM TP-1.0MM

TP1704 TP1703 TP1702 TP1701

1

1

1

1

1

1

1

[3,17] PWRKEY

[17] KCOL1' KCOL1'

[17] KROW0' KROW0'

HOLE-VIA2.4MM

KCOL0' HOLE-VIA1.2MM

[17] KCOL0' HOLE1702

HOLE1713

PWRKEY

HOLE1712

HOLE1711

HOLE-1.6MM

100nF

1

HOLE-1.6MM

1

1

1

C1730

Volume Up(KCOL1 KROW0)

VR1704

VR1702

VR1703

VR1706

Volume Down(KCOL0 KROW0) GND GND

FIDUCIAL-MARK-1MM

FIDUCIAL-MARK-1MM FIDUCIAL-MARK-1MM

FIDUCIAL-MARK-1MM

MARK1701MARK1702 MARK1703 MARK1704

1

PROOF1 PROOF1702

ICO-WATERPROOF-D3

1

1

1

1

1 SN-23X5

PROOF1701

ICO-WATERPROOF-D3

HOLE-VIA1.2MM HOLE-VIA1.2MM

HOLE1714 HOLE1716

HOLE1715

HOLE-1.2MM

1

1

1

J1

1 10

2 9

[17] KCOL1' KCOL0' [17]

3 8

[3,17] PWRKEY KROW0' [17]

4 7

5 6

J1702

BTBS-AXQ1101GX1

1

2

3

4

4PIN-ZHIJIA-S96523A1-SC

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 17_KEY_LEDS SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 17 OF 33

[18]

AUX_I2C_SDA

[18]

AUX_I2C_SCL

优选 HALL

VIO18_PMU

U1801

3 1

VDDIO SDO

GND

4 2 R1803 0

VDDD SDX SDA2 [2,18]

7 12 R1804 0

1uF

R1801 0 VDDA SCK SCL2 [2,18]

9 10

GND CSB

1uF

8 11

C1801

GND PS

6

CAP0 5

INT EINT_ACC

C1813

[2,18]

SENSOR-ACCELER-BMA220

GND

GND GND

BMA222E VIO18_PMU

VIO18_PMU

R1815

8bit 优选

ALS+PS+IR

47K_NF

EINT_ACC

[2,18]

BMA222E与BMA220的外围器件可以不用修改

M-Sensor

Gyroscope

*** ** *

VIO18_PMU

VIO18_PMU

GND VIO18_PMU

GND

GND

VIO18_PMU

VIO28_PMU

EINT20_GY [2]

GND

SDA2 [2,18]

SCL2 [2,18]

GND

AUX_I2C_SDA [18]

AUX_I2C_SCL [18] GND

GND

GND

GND

VIO28_PMU

GND

[2] EINT6_M

GND SDA2 [2,18]

0xD0 Write

VIO18_PMU

GND

MPU6880 SCL2 [2,18]

ECOMPASS_I2C_SCL

AD0=0 7b1101000 0x68

ECOMPASS_I2C_SDA

0x18 Write

AD0=1 7b1101001 0x69

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 18_SENSORS SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 18 OF 33

** ** *

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 98_BLOCK_DIAGRAM SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 19 OF 33

** ** *

Version History

Date Version Page Description

2013/03/11 V0.1 Draft release

2013/03/22 V0.11 01 1. Add R107/R103

2. Delete R605/R107

03 1. Add R326/R328

04 1. Delete U1802 and related circuit

2. Add U401 and related circuit

06 1.Add R418

07 1.Delete R639/R634

10 1. Swap U2 (MT6627) pin 36, 37 and 38 and their circuitry.

2. Remove R1070, R1073

3. F201 change footprint to DIPLEXER/6P/SMD/DP1608

15 1. Change C1218,C1219 to 22pF, Change C1214,C1215 to 1.2pF, Change C1216,C1217 to 68pF , Change c1203 4.7uF

1 1. Remove C138, c153, C145. Change C140, C148 to 1u

3 1. Add C353, R339, C243

2. Modify Isense trace.

789 1. Update RF matching (L615, L600, L619, L616, L622, C670, L623, L626, L625, C629, C627, C603, C662,

C664, L617, C624, R617, C651, C655, C652, L610, C648, C657, L609, L608, L611, C649, C626, L607, R620,

C634, L631, L627, L629, L636)

2013/03/22 V0.12 1 3 6 12 1. Add R360~R367, R101, R108, R105, R106, R109, R102, R104, R116, R117, R118, R115, R114, R113, R111

R418, R512, R513, R915, R916 for low-power testing

10 1. C222 change to 4.7uF

12 1. Add C914 / R904

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 99_VERSION_HISTORY SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 20 OF 33

** ** *

MT6582 BB PART MT6290M

[2,21,23] MC2CK MC2CK [2,21,23]

[2,21,23] MC2CM MC2CM [2,21,23]

[2,21,23] MC2DA3 MC2DA3 [2,21,23]

[2,21,23] MC2DA2 MC2DA2 [2,21,23]

[2,21,23] MC2DA1 MC2DA1 [2,21,23]

[2,21,23] MC2DA0 MC2DA0 [2,21,23]

[2,21,24] AP_PCM_RX AP_PCM_RX [2,21,24]

[2,21,24] AP_PCM_TX AP_PCM_TX [2,21,24]

[2,21,24] AP_PCM_FSYNC AP_PCM_FSYNC [2,21,24]

[2,21,24] AP_PCM_CK AP_PCM_CK [2,21,24]

R8001 0

[2] UTXD2 LTE_SUART1_RXD [24]

Johnson Yang 130627:

[2] URXD2 LTE_SUART1_TXD [24]

R8002 0

LTE_32KIN эパ BPI_BUS14 矗ㄑ

[2,21,22] LTE_PMU_EN_P LTE_PMU_EN_P LTE_PMU_EN_P [2,21,22]

[2,21,25] LTE_AP_RSTB LTE_AP_RSTB LTE_AP_RSTB [2,21,25]

[2,21,25] EINT5_RSTB_FROM_LTE EINT5_RSTB_FROM_LTE [2,21,25]

[2,21,23] EINT7_SDIO_INTB_LTE EINT7_SDIO_INTB_LTE [2,21,23]

LTE_SRCLKEN_OUT0 [22,26,29]

[2] SRCLKENAI

R8003 0

[2,21,24] AP_WAKEMD_INT

R8004 0

VBAT LTE_VBAT_MT6339

VBAT VBAT

LTE_VSIM1 LTE_VSIM1

LTE_VSIM2 LTE_VSIM2

From MT6339 to SIM2

[21,22] LTE_USIMLV2_RST LTE_USIMLV2_RST [21,22]

[21,22] LTE_USIMLV2_DATA LTE_USIMLV2_DATA [21,22]

[21,22] LTE_USIMLV2_CLK LTE_USIMLV2_CLK [21,22]

From MT6339 to SIM1

[15,21,22] LTE_USIMLV1_CLK LTE_USIMLV1_CLK [15,21,22]

[15,21,22] LTE_USIMLV1_DATA LTE_USIMLV1_DATA [15,21,22]

[15,21,22] LTE_USIMLV1_RST LTE_USIMLV1_RST [15,21,22]

[21,24] LTE_CVJTCK LTE_CVJTCK [21,24]

[21,24] LTE_CVJTMS LTE_CVJTMS [21,24]

[21,24] LTE_MDUART_TXD LTE_MDUART_TXD [21,24]

[21,24] LTE_MDUART_RXD LTE_MDUART_RXD [21,24]

AP to MT6169 RF PART

R8005 0

VIO18_PMU MT6169_VIO18_PMU

R8006 0 MT6169_VTCXO_PMU

VTCXO_PMU

[2,3,4,21,29] SRCLKENA SRCLKENA [2,3,4,21,29]

MT6165 RF PART

[21] LTE_RFIC1_BSI_CK LTE_RFIC1_BSI_CK [21]

[21] LTE_RFIC1_BSI_EN LTE_RFIC1_BSI_EN [21]

[21] LTE_RFIC1_BSI_D2 LTE_RFIC1_BSI_D2 [21]

[21] LTE_RFIC1_BSI_D1 LTE_RFIC1_BSI_D1 [21]

[21] LTE_RFIC1_BSI_D0 LTE_RFIC1_BSI_D0 [21]

[21] LTE_2G_RX_BBIP LTE_2G_RX_BBIP [21]

[21] LTE_2G_RX_BBIN LTE_2G_RX_BBIN [21]

[21] LTE_2G_RX_BBQP LTE_2G_RX_BBQP [21]

[21] LTE_2G_RX_BBQN LTE_2G_RX_BBQN [21]

[21] MT6165_CLK1 MT6165_CLK1 [21]

LTE_VIO18_PMU

LTE_VIO18_PMU

LTE_VTCXO2 LTE_VTCXO2

LTE_VRF18_2_PMU LTE_VRF18_2_PMU

TITLE: <TITLE> REV: <REV>

[21,26] LTE_SRCLKEN_OUT1 LTE_SRCLKEN_OUT1 [21,26]

DOCUMENT NO.: 80_AP_MD_I/F_CONNECTION SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 21 OF 33

** ** *

I2C Address

FAN53555 : 0xC0

NCP6335D: 0x1C LTE_VBAT_MT6339

U8103

B4 AGND AVIN D1

C8124

R8109

10uF

LTE_PMU_EN_P

EXT_VCORE_EN A2 EN PVIN D2

E1 C337 must to be close

[2,21,22]

0 PVIN

A1 VSEL PVIN E2 to U302

LTE_SRCLKEN_IN1

B3 D3

100K_NF

R8110

POWER_FAIL SW L8107 0.47UH

SW D4 LTE_DVCCK

B2 INTERRUPT SW E3

VBAT VBAT_BUCK

SW E4 As short as possible and L307 as close as possible to L301,

R8108 then connect to VPROC_PMU

PGND C1

PGND C2 C8123

0 C3

PGND

PGND C4

[24] LTE_I2C_SDA B1 SDA 10uF

[24] LTE_I2C_SCL A3 SCL FB A4

NCP6335 / FAN53555 VPROC_FB should be ground shielding.

LTE_VBAT_MT6339

LTE_VBAT_MT6339 VBAT_BUCK

Star connection into Power input Pin

Star connection into Power input Pin U8101

W:30mil/ (15mil chip ) W:40mil/ (15mil chip )

E2 VBAT_DLDO1 VBAT_VCORE A9

W:30mil/ (15mil chip ) W:30mil/ (15mil chip )

G1 VBAT_DLDO2 VBAT_VIO18 B10

W:20mil/ (15mil chip ) W:30mil/ (15mil chip )

K7 VBAT_ALDO VBAT1_VPA J10

W:30mil/ (15mil chip ) W:30mil/ (15mil chip )

A1 DVDD18_VM12 VBAT2_VPA K10

LTE_VIO18_PMU W:10mil/ (10mil chip ) W:30mil/ (15mil chip )

B1 DVDD18_VUSB11 VBAT_VRF18 G10

VBAT_VRF18_2 D10

Add 0-ohm for current

1.0uF

1.0uF

4.7uF

4.7uF

4.7uF

LTE_DVDD18_MIPI

LTE_VTCXO2 Add 0-ohm for current measurement measurement

Input cap should be

LTE_VFS LTE_VM12 Input cap should be C8119

LTE_VSIM2 C8115 C8116 C8117 C8118 close to the PMIC GND

C8101

C8104

C8103

C8102

close to the PMIC

C8105

LTE_VIO33 LTE_VTCXO1

LDO BUCK to redue the loop area

LTE_VSIM1 2.2uF 2.2uF 4.7uF 4.7uF 10uF

LTE_VA18

1.0uF

C8106 W:10mil LTE_DVCCK

D1 VIO28

W:10mil

D3 VIO33

W:10mil

LTE_VIO33 F1 VMIPI C8114

W:10mil W:40mil/ (15mil chip )

F3 VFS

LTE_DVDD18_MIPI L8101 2.2UH

W:40mil

G2 VMC VCORE A10 10uF

LTE_VFS F2 VMCH

W:8mil

J1 VSIM1

W:10mil W:3mil

H1 VSIM2 VCORE_FB A7

LTE_VIO18_PMU

MT6339

W:6mil W:30mil/ (15mil chip )

K5 VTCXO1

W:6mil

K6 VTCXO2 L8102 2.2UH

W:10mil W:30mil

LTE_VSIM1 K8 VA18 VIO18 C10

C8113

4.7uF

LTE_VSIM2 W:30mil A2 VM12

W:3mil

W:10mil VIO18_FB B8

LTE_VTCXO1 C1 VUSB11

W:20mil/ (15mil chip )

LTE_VTCXO2 L8103 2.2UH

W:20mil

E3 GND_LDO1 VRF18 F10 LTE_VRF18_PMU

LTE_VA18 H3 GND_LDO2

D4 GND_LDO3 W:3mil

E4 VRF18_FB J8

C8112

LTE_VM12

4.7uF

GND_LDO4

1.0uF

F4 GND_LDO5 W:20mil/ (15mil chip )

G4 GND_LDO6

E5

C8107

GND_LDO7 L8104 2.2UH

F5 GND_LDO8 VRF18_2 E10

C6 GND_LDO9

E6 GND_LDO10

F6 GND_LDO11 VRF18_2_FB A8 LTE_VRF18_2_PMU

G6 GND_LDO12 W:30mil/ (15mil chip )

B7 GND_LDO13

C7 2.2UH

C8111

GND_LDO14

4.7uF

D7 L8105 W:30mil

GND_LDO15 VPA H10

E7 GND_LDO16

F7 GND_LDO17 W:3mil

G7 GND_LDO18 VPA_FB K9

H9 GND_LDO19

J9 GND_LDO20 1.LX should be as

LTE_VPA_PMU

short as possible

2.FB should be C8110

shielding with GND and

Signals don't cross with LX 2.2uF

[26] LTE_PMU_BSI_CK LTE_PMU_BSI_CK D5 PMU_BSI_CK

[26] LTE_PMU_BSI_CS0B LTE_PMU_BSI_CS0B C4 PMU_BSI_CS

LTE_PMU_BSI_DO C5 PMU_BSI_DATA

[26] LTE_PMU_BSI_DO

GND1_VCORE C8

GND2_VCORE C9

[2,21,22] LTE_PMU_EN_P H5 PMU_EN GND1_VIO18 D8

H6 PMU_CHGIN GND2_VIO18 D9

[25] LTE_XRSTB LTE_XRSTB A6 XRSTB GND1_VRF18 F8 Output cap should be

R8105 0 LTE_SRCLKEN_IN1 A5 F9

SRCLKEN_IN1 GND2_VRF18

[21,26,29] LTE_SRCLKEN_OUT0

R8106 0 B5 SRCLKEN_IN2 GND1_VRF18_2 E8 close to the PMIC GND

[24] LTE_SRCLKEN_OUT2

B6 E9

[26] LTE_PMU_EINT

LTE_PMU_EINT

D6

PMU_EINT GND2_VRF18_2

G9 to reduce the loop area

GND_GPIO GND2_VPA

GND1_VPA G8

USIM

[23] LTE_USIM1RST LTE_USIM1RST B4 USIM1RST

[23] LTE_USIM1DATA LTE_USIM1DATA J3 USIM1DATA VREF

[23] LTE_USIM1CLK LTE_USIM1CLK B3 USIM1CLK

[15,21] LTE_USIMLV1_RST LTE_USIMLV1_RST J5 USIMLV1_RST AVDD18_DIG C2

[15,21] LTE_USIMLV1_DATA LTE_USIMLV1_DATA K3 USIMLV1_DATA Close to PMIC

[15,21] LTE_USIMLV1_CLK LTE_USIMLV1_CLK J4 USIMLV1_CLK

PMU_VREF J7 LTE_PMU_VREF

[23] LTE_USIM2RST LTE_USIM2RST A3 USIM2RST

[23] LTE_USIM2DATA LTE_USIM2DATA J2 USIM2DATA

[23] LTE_USIM2CLK C3 USIM2CLK GND_VREF J6

LTE_USIM2CLK

[21] LTE_USIMLV2_RST LTE_USIMLV2_RST H2 USIMLV2_RST

[21] LTE_USIMLV2_DATA LTE_USIMLV2_DATA K2 USIMLV2_DATA PMU_FSOURCE B2

LTE_USIMLV2_CLK K1 USIMLV2_CLK PMU_TESTMODE H4

[21] LTE_USIMLV2_CLK

100nF

1.0uF

C8109

C8108

1.GND_VREF couldn't connect to

system GND directly.

2.GND_VREF should routing with

PMU_VREF together and throuh via

connecto GND near the 100nF.

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 81_MT6339 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 22 OF 33

** ** *

LTE_VIO33

AVDD33_USB

C8242

1.0uF

TP-0.5MM

TP-0.5MM

Close to C2 Pin

LTE_VIO18_PMU

AVDD18_USB

T8202

U8201-A

TP-0.5MM

T8201

TP-0.5MM

C2 F3

TP-0.5MM

AVDD18_SSUSB AVDD33_USB SSUSB_RXP

1

B3 AVDD18_USB SSUSB_RXN G3

Close to B3/C1 Pin LTE_DVCCK C1 AVDD18_SSUSB

SSUSB_TXP D2

E1 AVDD11_SSUSB SSUSB_TXN E2

100nF

C8246

A1

USB_DP

A2 USB Trace Routing should be with differential pair

USB_DM

E3

AVDD11_SSUSB AVSS_USB

T8203

1

T8204

T8205

LTE_VIO18_PMU

1

G5 AVSS_USB XTALI_SSUSB C3

Close to E1 Pin XTALO_SSUSB B2

R8226 R8227

B19 USB_DL_MODE SSUSB_VRT B1 LTE_SSUSB_VRT

100nF

C8247

NF(10K) 5.1K

SDIO_CLK A16 MC2CK

[2,21]

MC2CK

SDIO_CMD B15 MC2CM

[2,21]

MC2CM

[22] LTE_USIM1CLK LTE_USIM1CLK M4 USIM1CLK

[22] LTE_USIM1DATA LTE_USIM1DATA M7 USIM1DATA SDIO_DAT3 B14 MC2DA3 MC2DA3 [2,21]

[22] LTE_USIM1RST LTE_USIM1RST M3 USIM1RST SDIO_DAT2 C14 MC2DA2 MC2DA2 [2,21]

[22] LTE_USIM2CLK LTE_USIM2CLK L2 USIM2CLK SDIO_DAT1 C13 MC2DA1 MC2DA1 [2,21]

[22] LTE_USIM2DATA LTE_USIM2DATA M6 USIM2DATA SDIO_DAT0 E14 MC2DA0 MC2DA0 [2,21]

LTE_USIM2RST L4 USIM2RST SDIO_HOST_INTB E18 EINT7_SDIO_INTB_LTE EINT7_SDIO_INTB_LTE [2,21]

[22] LTE_USIM2RST

TP-0.5MM

1

T8206

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 82_MT6290M_USB/SDIO/USIM SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 23 OF 33

** ** *

TP-0.5MM

T8301

U8201-B

A4 MSDC0P_CLK NFI_ALE F22

F7 MSDC0P_CMD NFI_CLE F23

A5 MSDC0P_INS NFI_WEB D22

1

E7 MSDC0P_WP NFI_REB F21

NFI_RBY1 G21

D7 MSDC0P_DAT7 NFI_RBY0 E22

D5 MSDC0P_DAT6 NFI_CE1B F20 LTE_SRCLKEN_OUT3

B6 MSDC0P_DAT5 NFI_CE0B E23

G6 MSDC0P_DAT4 R8331

C7 MSDC0P_DAT3 NFI_DAT15 B23 LTE_AGPS_OUT LTE_AGPS_OUT LTE_AGPS_OUT EINT8_AGPS_OUT_LTE [2]

LTE_VIO18_PMU B4 MSDC0P_DAT2 NFI_DAT14 A22 [24] [24] 0

E6 MSDC0P_DAT1 NFI_DAT13 C23

B5 MSDC0P_DAT0 NFI_DAT12 A23

NFI_DAT11 D20 AP_PCM_RX AP_PCM_RX [2,21]

NFI_DAT10 C22 AP_PCM_TX AP_PCM_TX [2,21]

NFI_DAT9 E20 AP_PCM_FSYNC AP_PCM_FSYNC [2,21]

R8301 10K_NF NFI_DAT8 D21 AP_PCM_CK

AP_PCM_CK [2,21]

LTE_SPI_CLK B13 SPI_CK

[22] LTE_SRCLKEN_OUT2 A14 SPI_CS1B NFI_DAT7 B22

LTE_SPI_CS0B E13 SPI_CS0B NFI_DAT6 B20

B12 SPI_HOLDB NFI_DAT5 B21

R8302 10K_NF

D12 SPI_MISO NFI_DAT4 A20

D13 SPI_MOSI NFI_DAT3 A19

C12 SPI_WB NFI_DAT2 E19

U22 SPITOAHB_CK NFI_DAT1 C21

U23 SPITOAHB_DATA NFI_DAT0 E21

LTE_VIO18_PMU

LTE_JTCK R8303 10K

MT6290_GPIO17: LTE_JTDI R8304 10K

for Conn_LTE co-existence U8201-C

LTE_JTDO 1

[2] MT6290_GPIO17 B8 GPIO17 JTCK N19 LTE_JTCK TP-0.5MM

B7 T8302

[2,21] AP_WAKEMD_INT AP_WAKEMD_INT

GPIO16 JTDI P19 LTE_JTDI

JTDO M22 LTE_JTDO

LTE_JTMS R8305 10K

A10 JTMS P20

TP-0.5MM

LTE_JTMS

[24] I2C_EXIST GPIO15

T8306

1 B10 GPIO14 JTRST_N N22 LTE_JTRST_N LTE_JTRST_N R8306 10K

G8 GPIO13

F8 M19 LTE_CVJTCK [21,24] LTE_CVJTCK R8307 10K

GPIO12 CVJTCK LTE_CVJTCK

E8 GPIO11 CVJTMS M20 LTE_CVJTMS [21,24]

LTE_CVJTMS LTE_CVJTMS R8308 10K

D8 GPIO10

B9 GPIO9 SBJTCK P23 LTE_SBJTCK LTE_SBJTCK R8309 10K

C8 GPIO8 SBJTMS P22 LTE_SBJTMS

LTE_SBJTMS R8310 10K

E12 GPIO7 SUART0_TXD R22 LTE_SUART0_TXD

D9 GPIO6 SUART0_RXD T22 LTE_SUART0_RXD LTE_SUART0_TXD 1 TP-0.5MM

A8 GPIO5 SUART0_RTSB R23 LTE_SUART0_RTSB

T8303

A11 GPIO4 SUART0_CTSB T19 LTE_SUART0_CTSB

B11 LTE_SUART0_RXD R8311 10K

GPIO3

C11 GPIO2 SUART1_TXD P21 LTE_SUART1_TXD LTE_SUART1_TXD [21]

D11 GPIO1 SUART1_RXD R21 LTE_SUART1_RXD

LTE_SUART1_RXD [21,24] LTE_SUART0_RTSB 1

E11 GPIO0 TP-0.5MM

MDUART_TXD R20 LTE_MDUART_TXD LTE_MDUART_TXD [21,24] T8304

MDUART_RXD T20 LTE_MDUART_RXD

LTE_MDUART_RXD [21,24] LTE_SUART0_CTSB R8312 10K

R8313 10K

I2C_SCL V16

LTE_SUART1_RXD

LTE_I2C_SCL [22,24]

I2C_SDA V17 LTE_I2C_SDA [22,24]

LTE_MDUART_TXD 1

TP-0.5MM

T8305

LTE_MDUART_RXD R8314 10K

R8315 1K

[22,24] LTE_I2C_SCL

R8316 1K

[22,24] LTE_I2C_SDA

R8317 10K

[24] I2C_EXIST

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 83_MT6290M_MSDC/SPI/NFI/UART/GP SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 24 OF 33

** ** *

LTE_VA18

R8401

100K

LTE_AUX_IN1

100K

NTC8402

Close to LTE RF-PA

LTE_VA18

R8433

100K

100nF_NF

C8407

100K

LTE_VTCXO1 U8201-D

NTC8401

LTE_VTCXO1 AA11 AVDD28_DAC AUX_IN5 W9

LTE_VIO18_PMU L23 AVDD18_MEMPLL AUX_IN4 AB11

LTE_VA18 AC10 AVDD18_OSC32 AUX_IN3 V9

LTE_VA18 AA8 AVDD18_AUXADC AUX_IN2 AA9 Close to U1607,rounting with

AVDD28_DAC LTE_VIO18_PMU

H3 AVDD18_L_MEMPLL AUX_IN1 AB10 LTE_AUX_IN1 C8403 100nF_NF

E16 AB9 ground guard

100nF

C8405

C8456

1.0uF

LTE_VIO18_PMU AVDD18_SYSPLL AUX_IN0

Close to AA11 Pin

LTE_VA18 AB8 AVDD18_MD APC2 U13

LTE_VIO18_PMU

U10 DVDD18_MD APC1 U12 LTE_APC1_6290 LTE_APC1_6290 [31]

U11 DVDD18_MD

TP-0.5MM

AP_RSTB C17 LTE_AP_RSTB

T8401

LTE_VIO18_PMU LTE_AP_RSTB [2,21] 1

AC13 AVSS_MD OUT_RSTB D18 EINT5_RSTB_FROM_LTE

EINT5_RSTB_FROM_LTE

AC2 AVSS_MD [2,21]

V7 AVSS_MD BOPT_RSV A17 LTE_BOPT_RSV LTE_VIO18_PMU

AVDD18_MEMPLL Y15 AVSS_MD R8463 10K

AC1

100nF

C8406

C8460

1.0uF

AVSS_MD

Close to L23 Pin LTE_0V6_LPDDR2

AB7 AC7 LTE_VREF_P C8458 100nF

AVSS_REF VREF_P

F1 J1 LTE_0V6_LPDDR2 C8459 100nF

AVSS18_L_MEMPLL VREFCA

L21 L22 LTE_0V6_LPDDR2 C8461 100nF

AVSS18_MEMPLL VREFDQ

J4 LTE_REXTDN R8464 NF( 56ohm) 1%

REXTDN

LTE_VA18 240

M17 H2 LTE_ZQ R8465

LTE_VA18 R_TN_MEMPLL ZQ

G2 R_TN_MEMPLLC3

M18 R_TP_MEMPLL XIN AC11 [25]

LTE_32KIN

F2 AC12

470nF

C8468

R_TP_MEMPLLC3 XOUT

AVDD18_OSC32K AVDD18_AUXADC

100nF

C8465

LTE_XRSTB

[22] LTE_XRSTB P2 XRSTB

Close to AC10 Pin Close to AA8 Pin

Y2 ET_P TEST_MODE D17

Y3 E15 R8422

ET_N EFUSE_FSOURCE_P LTE_VFS

NF(100nF)

LTE_32KIN [25] RTC32K_BPI_BUS14 [2]

C8462

LTE_VIO18_PMU B18 R_TN_SYSPLLC3 0

LTE_VIO18_PMU B17 R_TP_SYSPLLC3

AVDD18_SYSPLL

100nF

C8466

1.0uF

AVDD18_L_MEMPLL

Close to E16 Pin

C8469

C8470

1.0uF

100nF

C8472

C8473

1.0uF

Close to H3 Pin

LTE_VA18

AVDD18_MD

100nF

470nF

LTE_VM12

C8475

C8476

Close to AB8 Pin

LTE_VIO18_PMU

R8471

10K

LTE_0V6_LPDDR2

DVDD18_MD

LTE_0V6_LPDDR2

100nF

C8477

C8478

1.0uF

Close to U10/U11 Pin

R8473

C8402

100nF

1.0uF

C8401

10K

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 84_MT6290M_MISC SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 25 OF 33

** ** *

U8201-E

[29] LTE_LTEX26M_IN LTE_LTEX26M_IN U8 LTEX26M_IN RFIC1_BSI_CK AA17

RFIC1_BSI_EN Y17

Y10 TDX26M_IN RFIC1_BSI_D2 AB20

RFIC1_BSI_D1 AC20

RFIC1_BSI_D0 AB19

RFIC0_BSI_CK AA16 LTE_RFIC0_BSI_CK LTE_RFIC0_BSI_CK [29]

[21] LTE_SRCLKEN_OUT1 LTE_SRCLKEN_OUT1 V3 SRCLKEN_OUT1 RFIC0_BSI_EN AB17 LTE_RFIC0_BSI_EN LTE_RFIC0_BSI_EN [29]

[21,22,29] LTE_SRCLKEN_OUT0 LTE_SRCLKEN_OUT0 V2 SRCLKEN_OUT0 RFIC0_BSI_D2 AC19 LTE_RFIC0_BSI_D2 LTE_RFIC0_BSI_D2 [29]

RFIC0_BSI_D1 AC18 LTE_RFIC0_BSI_D1 LTE_RFIC0_BSI_D1 [29]

RFIC0_BSI_D0 AB18 LTE_RFIC0_BSI_D0 LTE_RFIC0_BSI_D0 [29]

[30,31,32] LTE_MIPI0_SCLK LTE_MIPI0_SCLK AB1 MISC_BSI_CK

AA1 MISC_BSI_CS1B PMU_BSI_CK M1 LTE_PMU_BSI_CK LTE_PMU_BSI_CK [22]

W2 MISC_BSI_CS0B PMU_EINT N2 LTE_PMU_EINT LTE_PMU_EINT [22]

Y1 MISC_BSI_DI PMU_BSI_CS1B M5

[30,31,32] LTE_MIPI0_SDATA LTE_MIPI0_SDATA W3 MISC_BSI_DO PMU_BSI_CS0B N3 LTE_PMU_BSI_CS0B LTE_PMU_BSI_CS0B [22]

PMU_BSI_DI M2

PMU_BSI_DO N4 LTE_PMU_BSI_DO LTE_PMU_BSI_DO [22]

U8201-F

[30,31,32,33] LTE_BPI_OUT25 LTE_BPI_OUT25 T3 BPI_OUT25 BPI_OUT15 P6 LTE_BPI_OUT15 LTE_BPI_OUT15 [30,31,32,33]

[30,31,32,33] LTE_BPI_OUT24 LTE_BPI_OUT24 U3 BPI_OUT24 BPI_OUT14 AB22 LTE_BPI_OUT14 LTE_BPI_OUT14 [30,31,32,33]

[30,31,32,33] LTE_BPI_OUT23 LTE_BPI_OUT23 R2 BPI_OUT23 BPI_OUT13 AB23 LTE_BPI_OUT13 LTE_BPI_OUT13 [30,31,32,33]

[30,31,32,33] LTE_BPI_OUT22 LTE_BPI_OUT22 R1 BPI_OUT22 BPI_OUT12 AA23 LTE_BPI_OUT12 LTE_BPI_OUT12 [30,31,32,33]

T2 BPI_OUT21 BPI_OUT11 AA22 LTE_BPI_OUT11 LTE_BPI_OUT11 [30,31,32,33]

P1 BPI_OUT20 BPI_OUT10 W19 LTE_BPI_OUT10 LTE_BPI_OUT10 [30,31,32,33]

T4 BPI_OUT19 BPI_OUT9 Y20

[30,31,32,33] LTE_BPI_OUT18 LTE_BPI_OUT18 U4 BPI_OUT18 BPI_OUT8 AA20

[30,31,32,33] LTE_BPI_OUT17 LTE_BPI_OUT17 P5 BPI_OUT17 BPI_OUT7 AB21

[30,31,32,33]

LTE_BPI_OUT16 R4 BPI_OUT16 BPI_OUT6 AA21 LTE_BPI_OUT6[30,31,32,33]

LTE_BPI_OUT16

BPI_OUT5 W21

[29] LTE_TXBPI LTE_TXBPI N5 LTE_TXBPI BPI_OUT4 V21

AC22 TD_TXBPI BPI_OUT3 W20 LTE_BPI_OUT3 [30,31,32,33]

BPI_OUT2 Y22 LTE_BPI_OUT2 [30,31,32,33]

[30] LTE_PAVM1 LTE_PAVM1 U2 PAVM1 BPI_OUT1 W23

[30] LTE_PAVM0 LTE_PAVM0 U1 PAVM0 BPI_OUT0 W22 LTE_BPI_OUT0 [30,31,32,33]

U8201-G

[29] LTE_RX2_BBIP LTE_RX2_BBIP Y5 LTE_RX2_BBIP TD_RX_BBIP AB14

[29] LTE_RX2_BBIN LTE_RX2_BBIN AA6 LTE_RX2_BBIN TD_RX_BBIN AB13

[29] LTE_RX2_BBQP LTE_RX2_BBQP W7 LTE_RX2_BBQP TD_RX_BBQP AB15

[29] LTE_RX2_BBQN LTE_RX2_BBQN Y7 LTE_RX2_BBQN TD_RX_BBQN AC15

[29] LTE_RX1_BBIP LTE_RX1_BBIP AC5 LTE_RX1_BBIP TD_TX_BBIP AA12

[29] LTE_RX1_BBIN LTE_RX1_BBIN AB5 LTE_RX1_BBIN TD_TX_BBIN Y12

[29] LTE_RX1_BBQP LTE_RX1_BBQP AC6 LTE_RX1_BBQP TD_TX_BBQP W14

[29] LTE_RX1_BBQN LTE_RX1_BBQN AB6 LTE_RX1_BBQN TD_TX_BBQN Y14

[29] LTE_TX_BBIP LTE_TX_BBIP AC3 LTE_TX_BBIP

[29] LTE_TX_BBIN LTE_TX_BBIN AB3 LTE_TX_BBIN

[29] LTE_TX_BBQP LTE_TX_BBQP AB4 LTE_TX_BBQP

[29] LTE_TX_BBQN LTE_TX_BBQN AC4 LTE_TX_BBQN

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 85_MT6290M_RF/IQ/BPI SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 26 OF 33

** ** *

LTE_DVCCK

1.0uF

1.0uF

100nF

1.0uF

100nF

100nF

100nF

1.0uF

1.0uF

C8609

C8604

C8608

C8601

C8607

C8602

C8603

C8606

C8605

LTE_DVCCK

LTE_VIO18_PMU

U8201-H

E10 DVCCK DVDD_GPIO A7

H20 LTE_VIO18_PMU

DVCCK

J17 DVCCK DVDD_NFI C20

LTE_VIO18_PMU LTE_VIO18_PMU

J18 DVCCK LTE_VIO18_PMU

LTE_VIO18_PMU

J19 DVCCK DVDD_MSDC0 C4

J6 DVCCK LTE_VIO18_PMU

K18 DVCCK DVDD_SPI A13

K19 LTE_VIO18_PMU

DVCCK

100nF

1.0uF

K5 DVCCK DVDD_RFBPI AC23

100nF

K6 LTE_VIO18_PMU

100nF

DVCCK

100nF

1.0uF

1.0uF

L17 DVCCK DVDD18_SDIO B16 DVDD_GPIO DVDD_RFBPI

L18 DVCCK DVDD18

C8615

LTE_VIO18_PMU

L19 Close to A7 Pin Close to AC23 Pin

C8616

DVCCK

L5 DVDD18_JTAG M23 Close to

C8614

DVCCK

C8611

C8610

P7

C8613

C8612

DVCCK LTE_DVDD18_MIPI

U15 DVCCK DVDD18_MIPI V1 F12/F16/M9/R7/U14 Pin

LTE_VIO18_PMU

DVDD18_DDR1 H1

DVDD18_DDR1 L1

C16 DVSS DVDD18_DDR0 G22 LTE_VIO18_PMU

G20 DVSS

H22 DVSS

H4 DVSS LTE_VIO18_PMU

H5 DVSS DVDD18 F12

J22 DVSS DVDD18 F16

K10 DVSS DVDD18 M9

K11 DVSS DVDD18 R7

LTE_DVDD18_MIPI

K12 DVSS DVDD18 U14 LTE_VIO18_PMU LTE_VIO18_PMU

LTE_VIO18_PMU

K13 DVSS

K14 DVSS LTE_VM12

K20 DVSS DVDD12_DDR1 J2

K21 DVSS DVDD12_DDR1 K2

100nF

K4 DVSS

LTE_VM12

100nF

100nF

100nF

1.0uF

L10 DVSS DVDD12_DDR0 H23

L11 DVSS DVDD12_DDR0 J23

L12 DVSS DVDD12_DDR0 K22 DVDD18_MIPI

L13 DVSS

DVDD_NFI DVDD_SPI DVDD18_JTAG

C8619

L14 Close to V1 Pin

C8618

C8617

C8620

DVSS

C8621

L20 DVSS

Close to C20 Pin Close to A13 Pin Close to M23 Pin

M10 DVSS

M11 DVSS

M12 DVSS

M13 DVSS

M14 DVSS

N10 DVSS

N11 DVSS

N12 DVSS

N13 DVSS

N14 DVSS

P10 DVSS

P11 DVSS

P12 DVSS

P13 DVSS

P14 DVSS

LTE_VIO18_PMU

100nF

1.0uF

DVDD18_SDIO

Close to B16 Pin within 150mils

C8622

C8623

LTE_VM12 LTE_VIO18_PMU LTE_VIO18_PMU

LTE_VM12

4.7PF(5PF)

4.7PF(5PF)

100nF

4.7uF

1.0uF

100nF

1.0uF

100nF

1.0uF

1.0uF

100nF

1.0uF

1.0uF

C8627

C8624

C8633

C8629

C8626

C8628

C8632

C8625

C8634

C8635

C8630

C8631

C8636

DVDD12_DDR0 DVDD12_DDR1 DVDD18_DDR1 DVDD18_DDR0

Close to H23/J23/K22 Pin Close to J2/K2 Pin Close to H1/L1 Pin Close to G22 Pin

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 86_MT6290M_POWER/GND SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 27 OF 33

** ** *

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 30_RF_MT6165_2G_TRX SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2014-7-30 SHEET: 28 OF 33

** ** *

[29,30,31] LTE_TXDET

[29,30] LTE_TX_HB2

LTE_TX_BBIP [26,29]

[29,30] LTE_TX_HB1

LTE_TX_BBIN [26,29]

LTE_TX_MB1 LTE_TX_BBQN [26,29]

[31]

Off-Page Connector LTE_TX_LB3

LTE_TX_BBQP [26,29]

[31] LTE_RX1_BBIP [26,29]

LTE_RX1_BBIN [26,29]

(To RF front-end) LTE_RFIP1_LB1

[31] LTE_RX1_BBQN [26,29]

LTE_RFIN1_LB1 LTE_RX1_BBQP [26,29]

[31]

LTE_TXDET

[29,30,31] LTE_RX2_BBIP [26,29]

LTE_RFIP1_HB1

[31] LTE_RX2_BBIN [26,29]

LTE_RFIN1_HB1 LTE_RX2_BBQN [26,29]

LTE_TX_HB1

[31]

B34/B39 LTE_TX_HB1

[29,30] LTE_RX2_BBQP [26,29]

LTE_TX_HB2

B38/B40/B41 LTE_TX_HB2

M13

M15

G14

G13

C15

C14

D14

H15

H14

N15

N14

N13

H13

B15

K14

K13

E13

E14

E15

F15

F14

F13

L13

L14

[29,30]

J14

J15

J13

M7

M6

M5

M4

N8

N7

N5

N4

U3101

H12

TX_BBIP

TX_BBQP

TXDET

TX_BBIN

TX_MB1

TX_MB2

TX_HB1

TX_HB2

RX1_BBIP

RX1_BBQP

RX2_BBIP

RX2_BBQP

TX_BBQN

RX1_BBIN

RX1_BBQN

RX2_BBIN

RX2_BBQN

DET_GND

TXO_GND

TXO_GND

TXO_GND

TXO_GND

TXO_GND

TXO_GND

TXO_GND

TXO_GND

TXO_GND

RFIP1_HB1

TX_LB1

TX_LB2

TX_LB3

TX_LB4

TST4

RFIN1_HB1

RFIN1_LB1

RFIP1_LB1

TST3 M12

TXBPI K10 LTE_TXBPI [26,29]

RES-2K-+-1%-0402

LTE_RFIP1_HB2

VRT N10

B41/B38 PRX [29,31]

TST2 M10

R3112 2k

TMEAS M9

LTE_RFIN1_HB2 B14 K6

[29,31] LTE_RFIP1_MB1 RFIP1_MB1 BSI_CK LTE_RFIC0_BSI_CK [26,29]

[31] BSI_EN J7 LTE_RFIC0_BSI_EN [26,29]

B13 J6

R3104

LTE_RFIN1_MB1 RFIN1_MB1 BSI_D0 LTE_RFIC0_BSI_D0 [26,29]

[31] J5

NF

BSI_D1 LTE_RFIC0_BSI_D1 [26,29]

A15 RFIP1_LB2 BSI_D2 K4 LTE_RFIC0_BSI_D2 [26,29]

[29,31] LTE_RFIP1_MB2

B34/B39 PRX A14 RFIN1_LB2

[29,31] LTE_RFIN1_MB2

[29,31] LTE_RFIP1_HB2 B12 RFIP1_HB2

[29,31] LTE_RFIP1_HB3 GND L12

B40 PRX [29,31] LTE_RFIN1_HB2

A12 RFIN1_HB2 GND L11

[29,31] LTE_RFIN1_HB3 GND L10

A11 RFIP1_LB3 GND L9

GND L8

[29,32] LTE_RFIP2_HB1 B11 L7

RFIN1_LB3 GND

B41/B38 DRX [29,32] LTE_RFIN2_HB1

GND L6

[29,31] LTE_RFIP1_MB2 B10 RFIP1_MB2 GND L3

GND K12

[29,31] LTE_RFIN1_MB2 B9 RFIN1_MB2 GND K9

[29,32] LTE_RFIP2_HB2 GND K8

B40 DRX [29,31] LTE_RFIP1_HB3 A9 RFIP1_HB3 GND K7

[29,32] LTE_RFIN2_HB2