Professional Documents

Culture Documents

De0 Nano c4 Rev C (Release - CD - Rom) PDF

De0 Nano c4 Rev C (Release - CD - Rom) PDF

Uploaded by

Bogdan Mihai MaximOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

De0 Nano c4 Rev C (Release - CD - Rom) PDF

De0 Nano c4 Rev C (Release - CD - Rom) PDF

Uploaded by

Bogdan Mihai MaximCopyright:

Available Formats

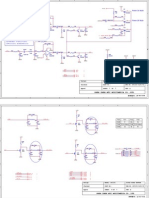

5 4 3 2 1

ALTERA Cyclone IV Development & Education Board (DE0-Nano)

D D

SCHEMATIC CONTENT PAGE

01 TOP Cover Page, Placement,TOP 01 ~ 03

02 EP4CE22 Cyclone IV EP4CE22 BANK1..BANK8 , POWER , CONFIG 04 ~ 08

03 IN/OUT CLOCK, LED, BUTTON,SW, GPIOs, 2X13 HEADER, G-SENSOR, ADC 09 ~ 11

04 MEMORY SDRAM, EEPROM 12 ~ 13

05 POWER POWER 1.2V, 2.5V, 3.3V 14

C C

B B

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B COVER PAGE C

Date: Thursday, July 12, 2012 Sheet 1 of 14

5 4 3 2 1

5 4 3 2 1

D D

C C

B B

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B PLACEMENT C

Date: Thursday, July 12, 2012 Sheet 2 of 14

5 4 3 2 1

5 4 3 2 1

D D

PAGE 4 - 8 PAGE 9 - 11

DRAM_DQ[15..0] GPIO_0_IN[1..0] CLOCK_50

DRAM_ADDR[12..0] DRAM_DQ[15..0] GPIO_0_IN[1..0] GPIO_0[33..0] GPIO_0_IN[1..0] CLOCK_50

PAGE 12 - 13 DRAM_ADDR[12..0] GPIO_0[33..0] GPIO_0[33..0]

DRAM_DQM[1..0] KEY[1..0]

DRAM_BA0 DRAM_DQM[1..0] KEY[1..0]

DRAM_ADDR[12..0] DRAM_DQ[15..0] DRAM_BA1 DRAM_BA0 GPIO_1_IN[1..0] SW[3..0]

DRAM_DQM[1..0] DRAM_ADDR[12..0] DRAM_DQ[15..0] DRAM_CAS_N DRAM_BA1 GPIO_1_IN[1..0] GPIO_1[33..0] GPIO_1_IN[1..0] SW[3..0]

DRAM_BA0 DRAM_DQM[1..0] DRAM_RAS_N DRAM_CAS_N GPIO_1[33..0] GPIO_1[33..0] LED[7..0]

DRAM_BA1 DRAM_BA0 DRAM_WE_N DRAM_RAS_N LED[7..0]

DRAM_CAS_N DRAM_BA1 DRAM_CS_N DRAM_WE_N GPIO_2_IN[2..0]

DRAM_RAS_N DRAM_CAS_N DRAM_CKE DRAM_CS_N GPIO_2_IN[2..0] GPIO_2[12..0] GPIO_2_IN[2..0]

DRAM_WE_N DRAM_RAS_N DRAM_CLK DRAM_CKE GPIO_2[12..0] GPIO_2[12..0] ADC_SDAT

DRAM_CS_N DRAM_WE_N DRAM_CLK ADC_SDAT ADC_CS_N

C DRAM_CS_N ADC_CS_N C

DRAM_CKE CLOCK_50 ADC_SADDR

DRAM_CLK DRAM_CKE CLOCK_50 ADC_SADDR ADC_SCLK

DRAM_CLK KEY[1..0] ADC_SCLK

KEY[1..0] JTAG_TMS I2C_SCLK

I2C_SCLK I2C_SDAT SW[3..0] TMS JTAG_TCK I2C_SDAT I2C_SCLK

I2C_SCLK I2C_SDAT SW[3..0] TCK JTAG_TDI G_SENSOR_CS_N I2C_SDAT

LED[7..0] TDI JTAG_TDO G_SENSOR_INT G_SENSOR_CS_N

04 MEMORY LED[7..0] TDO G_SENSOR_INT

NSTATUS

I2C_SCLK NSTATUS CONF_DONE 03 IN/OUT

I2C_SDAT I2C_SCLK CONF_DONE NCONFIG

G_SENSOR_CS_N I2C_SDAT NCONFIG NCE

G_SENSOR_INT G_SENSOR_CS_N NCE PAGE 14

G_SENSOR_INT

ADC_SDAT

ADC_CS_N ADC_SDAT

ADC_SADDR ADC_CS_N

ADC_SCLK ADC_SADDR

ADC_SCLK

02 EP4CE22

B 05 POWER B

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B TOP C

Date: Thursday, July 12, 2012 Sheet 3 of 14

5 4 3 2 1

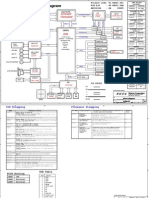

5 4 3 2 1

D D

SW[3..0]

DRAM_ADDR[12..0]

DRAM_DQ[15..0]

LED[7..0]

KEY[1..0]

U1A U1B

LED6 B1 DRAM_DQ5 J2 R1 DRAM_ADDR8

DRAM_WE_N C2 DQS2L/CQ3L,CDPCLK0 DRAM_DQ6 J1 DIFFIO_L7p/DQ1L IO2_0/DQS3L/CQ3L#,CDPCLK1

LED4 D1 DIFFIO_L3p DRAM_DQ4 K2 DIFFIO_L7n/DQ1L K5 DRAM_DQ3

C DIFFIO_L4N DIFFIO_L10p RUP1/DQ1L C

I2C_SCLK F2 DRAM_DQ15 K1 L4 DRAM_ADDR12

I2C_SDAT F1 DIFFIO_L5p DRAM_RAS_N L2 DIFFIO_L10n/DQ1L RDN1/DQ1L

DRAM_DQ0 G2 DIFFIO_L5n DRAM_CAS_N L1 DIFFIO_L11p/DQS1L/CQ1L#,DPCLK1 L3 LED7

DRAM_DQ1 G1 DIFFIO_L6p/DQS0L/CQ1L,DPCLK0 DRAM_ADDR10 N2 DIFFIO_L11n/DQ1L IO/VREFB2N0

DIFFIO_L6n G5 G_SENSOR_CS_N DRAM_ADDR11 N1 DIFFIO_L13p/DQ1L

IO1_0 DRAM_ADDR0 P2 DIFFIO_13n/DQ1L

F3 LED5 DRAM_ADDR9 P1 DIFFIO_L15p/DQ1L M2 G_SENSOR_INT

IO/VREFB1N0 DIFFIO_L15n/DM1L/BWS#1L CLK2/DIFFCLK_1p M1 SW0

CLK3/DIFFCLK_1n

BANK 1

BANK 2

E1 KEY1

CLK1/DIFFCLK_0n EP4CE22F17

EP4CE22F17

B B

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B EP4CE22 BANK1 & BANK2 C

Date: Thursday, July 12, 2012 Sheet 4 of 14

5 4 3 2 1

5 4 3 2 1

SW[3..0]

DRAM_ADDR[12..0]

D D

DRAM_DQ[15..0]

GPIO_1[33..0]

DRAM_DQM[1..0]

GPIO_1_IN[1..0]

U1D

U1C

DRAM_DQ14 N3 T2 DRAM_DQ9 GPIO_114 N9 P9 GPIO_113

DRAM_DQ13 P3 DIFFIO_B1p IO3_0/DQS1B/CQ1B#,CDPCLK2 M6 DRAM_BA1 GPIO_111 R10 DIFFIO_B14n/DQ5B IO4_0/DQS2B/CQ3B,DPCLK5

DRAM_DQ11 R3 DIFFIO_B1n/DM3B/BWS#3B IO3_1/DQ3B L7 DRAM_CKE GPIO_18 T10 DIFFIO_B16p/DQ5B

DRAM_DQ10 T3 DIFFIO_B2p/DQ3B IO3_2/DQ3B GPIO_19 R11 DIFFIO_B16n/DQS4B/CQ5B,DPCLK4

DRAM_ADDR1 N5 DIFFIO_B2n GPIO_17 T11 DIFFIO_B17p/DQ5B M10 GPIO_128

DRAM_ADDR2 N6 DIFFIO_B4p/DQ3B GPIO_16 R12 DIFFIO_B17n RUP2 N11 GPIO_115

DRAM_BA0 M7 DIFFIO_B4n/DQ3B GPIO_15 T12 DIFFIO_B18p/DQ5B RDN2

C DIFFIO_B5p/DQS3B/CQ3B#,DPCLK2 DIFFIO_B18n/DQ5B C

DRAM_DQ12 R5 P6 DRAM_CS_N GPIO_14 R13

DRAM_DQM1 T5 DIFFIO_B6p/DQ3B IO/VREFB3N0 GPIO_13 T13 DIFFIO_B20p P11 GPIO_110

DRAM_DQM0 R6 DIFFIO_B6n R4 DRAM_CLK GPIO_12 T14 DIFFIO_B20n/DQ5B IO/VREFB4N0

DRAM_ADDR7 T6 DIFFIO_B7p/DQ3B PLL1_CLKOUTp T4 DRAM_DQ8 GPIO_11 T15 DIFFIO_B23p/DQ5B

DRAM_DQ7 R7 DIFFIO_B7n PLL1_CLKOUTn GPIO_112 N12 DIFFIO_B23n/DQS0B/CQ1B,CDPCLK3 P14 GPIO_125

DRAM_ADDR5 T7 DIFFIO_B8p/DQ3B DIFFIO_B24p PLL4_CLKOUTp R14 GPIO_122

DRAM_DQ2 L8 DIFFIO_B8n/DQS5B/CQ5B#,DPCLK3 PLL4_CLKOUTn

DRAM_ADDR3 M8 DIFFIO_B9n/DQ3B R8 CLOCK_50 R9 GPIO_1_IN1

DRAM_ADDR6 N8 DIFFIO_B10n/DM5B/BWS#5B CLK15/DIFFCLK_6p T8 SW1 CLK13/DIFFCLK_7p T9 GPIO_1_IN0

DRAM_ADDR4 P8 DIFFIO_B11p/DQ5B CLK14/DIFFCLK_6n CLK12/DIFFCLK_7n

DIFFIO_B12n/DQ5B

BANK 4

BANK 3

EP4CE22F17 EP4CE22F17

B B

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B EP4CE22 BANK3 & BANK4 C

Date: Thursday, July 12, 2012 Sheet 5 of 14

5 4 3 2 1

5 4 3 2 1

D D

KEY[1..0] GPIO_2_IN[2..0]

GPIO_1[33..0] GPIO_2[12..0]

SW[3..0]

U1E U1F

GPIO_121 P16 GPIO_211 G16

GPIO_118 R16 DIFFIO_R15n/DQS3R/CQ3R#,CDPCLK4 GPIO_212 G15 DIFFIO_R5n/INIT_DONE

GPIO_123 N16 DIFFIO_R15p/DQ1R GPIO_29 F16 DIFFIO_R5p/CRC_ERROR

C DIFFIO_R13n/DQ1R DIFFIO_R4n/nCEO C

GPIO_124 N15 GPIO_28 F15

GPIO_129 L13 DIFFIO_R13p/DQ1R GPIO_23 C16 DIFFIO_R4p/CLKUSR

GPIO_116 L16 DIFFIO_R12p/DQ1R GPIO_24 C15 DIFFIO_R1n/PADD20/DQS2R/CQ3R,CDPCLK5

GPIO_119 L15 DIFFIO_R11n/DQ1R N14 GPIO_127 DIFFIO_R1p F13 GPIO_10

GPIO_117 K16 DIFFIO_R11p RUP3/DM1R/BWS#1R P15 GPIO_120 IO6_0 B16 GPIO_21

GPIO_131 K15 DIFFIO_R10n/DQ1R RDN3/DQ1R IO6_1/DQS0R/CQ1R,DPCLK7 D16 GPIO_25

GPIO_130 J16 DIFFIO_R10p/DQS1R/CQ1R#,DRCLK6 IO6_2 D15 GPIO_26

KEY0 J15 DIFFIO_R9n/DEV_OE L14 GPIO_126 IO6_3/PADD23

GPIO_133 J14 DIFFIO_R9p/DEV_CLRn IO/VREFB5N0 F14 GPIO_210

GPIO_132 J13 DIFFIO_R8n/DQ1R IO/VREFB6N0

DIFFIO_R7n/DQ1R E15 GPIO_2_IN0

M15 SW3 CLK4/DIFFCLK_2p E16 GPIO_2_IN1

CLK6/DIFFCLK_3p

BANK 6 CLK5/DIFFCLK_2n

M16 GPIO_2_IN2

CLK7/DIFFCLK_3n

BANK 5

EP4CE22F17

EP4CE22F17

B B

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B EP4CE22 BANK5 & BANK6 C

Date: Thursday, July 12, 2012 Sheet 6 of 14

5 4 3 2 1

5 4 3 2 1

D D

LED[7..0]

SW[3..0]

GPIO_2[12..0] GPIO_0[33..0]

GPIO_0_IN[1..0]

U1G U1H

GPIO_22 C14 E11 GPIO_026 GPIO_016 C8

GPIO_27 D14 DIFFIO_T24n RUP4 E10 GPIO_027 GPIO_020 E8 DIFFIO_T11p/PADD17/DQS5T/CQ5T#,DPCLK10 D8 GPIO_019

GPIO_031 D11 DIFFIO_T24p/DQ5T RDN4 GPIO_021 F8 DIFFIO_T10n/DATA2/DQ3T IO8_0/DQ3T E7 GPIO_018

GPIO_032 D12 DIFFIO_T23n GPIO_014 A7 DIFFIO_T10p/DATA3 IO8_1/DATA5/DQ3T D5 GPIO_09

LED1 A13 DIFFIO_T23p/DQS0T/CQ1T,CDPCLK6 GPIO_012 B7 DIFFIO_T9n/PADD18/DQ3T IO8_2 B3 GPIO_04

LED2 B13 DIFFIO_T22n GPIO_011 A6 DIFFIO_T9p/DATA4/DQ3T IO8_3/DATA12

C DIFFIO_T22p/DQ5T DIFFIO_T7n/DATA14/DQS3T/CQ3T#,DPCLK11 C

GPIO_030 A12 GPIO_010 B6

GPIO_033 B12 DIFFIO_T21n/DQ5T GPIO_017 E6 DIFFIO_T7p/DATA13/DQ3T

LED3 A11 DIFFIO_T21p/DQ5T GPIO_08 A5 DIFFIO_T6p/DATA6/DQ3T C6 GPIO_015

GPIO_029 B11 DIFFIO_T20n/DQ5T C11 GPIO_028 GPIO_07 B5 DIFFIO_T5n/DATA7/DQ3T IO/VREFB8N0

LED0 A15 DIFFIO_T20p/PADD0/DQ5T IO/VREFB7N0 GPIO_013 D6 DIFFIO_T5p/DATA8/DQ3T

GPIO_022 F9 DIFFIO_T19n/PADD1 GPIO_06 A4 DIFFIO_T4n/DATA9 D3 GPIO_00

ADC_CS_N A10 DIFFIO_T17p/PADD4/DQS2T/CQ3T,DPCLK8 GPIO_05 B4 DIFFIO_T3n/DATA10/DM3T/BWS#3T PLL3_CLKOUTp C3 GPIO_01

ADC_SADDR B10 DIFFIO_T16n/PADD5/DQ5T B14 ADC_SCLK GPIO_02 A2 DIFFIO_T3p/DATA11 PLL3_CLKOUTn

GPIO_024 C9 DIFFIO_T16p/PADD6/DQ5T PLL2_CLKOUTp A14 GPIO_20 GPIO_03 A3 DIFFIO_T2n

GPIO_025 D9 DIFFIO_T15n/PADD7/DQ5T PLL2_CLKOUTn DIFFIO_T2p B8 GPIO_0_IN1

GPIO_023 E9 DIFFIO_T15p/PADD8/DM5T/BWS#5T CLK11/DIFFCLK_4p A8 GPIO_0_IN0

DIFFIO_T13p/PADD12/DQS4T/CQ5T,DPCLK9 CLK10/DIFFCLK_4n

BANK 8

B9 SW2

CLK9/DIFFCLK_5p A9 ADC_SDAT

CLK8/DIFFCLK_5n EP4CE22F17

BANK 7

EP4CE22F17

B B

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B EP4CE22 BANK7 & BANK8 C

Date: Thursday, July 12, 2012 Sheet 7 of 14

5 4 3 2 1

5 4 3 2 1

VCC1P2 VCC1P2 VCC1P2 VCC1P2 VCC1P2 VCC1P2

VCC3P3

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17

100u 2.2n 2.2n 4.7n 4.7n 10n 10n 0.47u 0.47u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u

M14

G14

C10

C13

P10

P13

K14

E14

A16

T16

M3

G3

C4

C7

E3

K3

P4

P7

A1

T1

U1I

D D

VCCIO1

VCCIO1

VCCIO2

VCCIO2

VCCIO3

VCCIO3

VCCIO3

VCCIO4

VCCIO4

VCCIO4

VCCIO5

VCCIO5

VCCIO6

VCCIO6

VCCIO7

VCCIO7

VCCIO7

VCCIO8

VCCIO8

VCCIO8

VCCD_PLL

N4

D13 VCCD_PLL1

D4 VCCD_PLL2 VCC3P3 VCC3P3

N13 VCCD_PLL3

VCCD_PLL4 E4

GND E13

F7 GND G4 C18 C19 C20 C21 C22 C23 C24 C25 C26

VCC1P2 VCCINT GND

F11 G13

G6 VCCINT GND K4 100u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u

G7 VCCINT GND K13

G8 VCCINT GND M4

G9 VCCINT GND M13

G10 VCCINT GND N7

H6 VCCINT GND N10

VCCINT

POWER & GND GND

H11 P5

J6 VCCINT GND P12 VCCA VCCD_PLL

K7 VCCINT GND R2

K11 VCCINT GND R15

L6 VCCINT GND E2

K9 VCCINT GND H16 C27 C28 C29 C30 C31 C32 C33 C34

C VCCINT GND C

K10 H15

M9 VCCINT GND 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u

M11 VCCINT M5

J12 VCCINT GNDA1 E12

VCCINT GNDA2 E5

GNDA3 M12

L5 GNDA4

VCCA VCCA1

F12

F5 VCCA2

L12 VCCA3 VCC2P5 VCCA VCC1P2 VCCD_PLL

VCCA4

L1 BEAD L2 BEAD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

EP4CE22F17 C35 C36

H7

H8

H9

H10

J7

J8

J9

J10

F6

F10

J11

K8

K6

L9

L10

L11

K12

G11

B2

B15

C5

C12

D7

D10

10u 10u

VCC3P3 Close to EPCS

VCC3P3 U9

1 8 R41 24.9 DATA0

2 VCC DATA 16 DCLK

C89 9 VCC DCLK 7 NCSO

10 VCC nCS 15 ASDO

VCCA 0.1u GND ASDI

B B

EPCS64

R39

10K

VCCA R1 R2 R3 DNI

U1J 0 0 0

DNI

TCK H3 H13

TCK R4 TBD TMS J5 TCK MSEL0 H12

R5 R6 DNI TDI H4 TMS MSEL1 G12

R7 TDO J4 TDI MSEL2

10K 10K TDO

1K C37 AS Fast POR configuration

TMS DNI TBD DCLK H1 CONFIGURATION at 3.0- or 2.5-V

DCLK R8 R9 R10

TDI NSTATUS F4 C1 ASDO

nSTATUS ASDO D2 NCSO 0 0 0

NCONFIG H5 nCSO H2 DATA0 DNI DNI

nCONFIG DATA0

NCE J3 H14 CONF_DONE

TDO R11 1K nCE CONF_DONE

VCCA

DNI EP4CE22F17

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B EP4CE22 POWER and CONFIGURATION C

Date: Thursday, July 12, 2012 Sheet 8 of 14

5 4 3 2 1

5 4 3 2 1

LED[7..0]

LED0 LEDG

D D

RN1 120

LED0 1 8 LED1 LEDG

LED1 2 7

LED2 3 6 VCC3P3

LED3 4 5 LED2 LEDG

LED3 LEDG C38 Y1

1 4

0.1u EN VCC

2 3 CLOCK_50

GND OUT

LED4 LEDG 50MHZ

RN2 120

LED4 1 8 LED5 LEDG

LED5 2 7

LED6 3 6

LED7 4 5 LED6 LEDG

VCC3P3

LED7 LEDG

C C

SW[3..0]

8

7

6

5

RN3

10K

1

2

3

4

VCC2P5

SW1

ON

1 8 SW0

1

2 7 SW1

R12 VCC2P5 3 6 SW2

100K 4 5 SW3

C41 SW-DIP8

R13

KEY0

4 3 0.1u

VCC2P5

1 2 C39

2K U2

TACK_SW_RA 1n 14 15

1 VCC ETP 2 KEY0

3 1A 1Y 4 KEY1

5 2A 2Y 6

9 3A 3Y 8

B B

11 4A 4Y 10

13 5A 5Y 12 KEY[1..0]

VCC2P5 6A 6Y 7

GND

SN74AUC17

R14

100K

R15

KEY1

4 3

1 2 C40

2K

TACK_SW_RA 1n

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B CLOCK & LED & BUTTON & SWITCH C

Date: Thursday, July 12, 2012 Sheet 9 of 14

5 4 3 2 1

5 4 3 2 1

D GPIO_0[33..0] GPIO_1[33..0] D

GPIO_0_IN[1..0] GPIO_1_IN[1..0]

GPIO - 0 GPIO - 1

JP1 JP2

GPIO_0_IN0 1 2 GPIO_00 GPIO_1_IN0 1 2 GPIO_10

GPIO_0_IN1 3 1 2 4 GPIO_01 GPIO_1_IN1 3 1 2 4 GPIO_11

GPIO_02 5 3 4 6 GPIO_03 GPIO_12 5 3 4 6 GPIO_13

GPIO_04 7 5 6 8 GPIO_05 GPIO_14 7 5 6 8 GPIO_15

GPIO_06 9 7 8 10 GPIO_07 GPIO_16 9 7 8 10 GPIO_17

11 9 10 12 11 9 10 12

VCC_SYS 11 12 VCC_SYS 11 12

GPIO_08 13 14 GPIO_09 GPIO_18 13 14 GPIO_19

GPIO_010 15 13 14 16 GPIO_011 GPIO_110 15 13 14 16 GPIO_111

GPIO_012 17 15 16 18 GPIO_013 GPIO_112 17 15 16 18 GPIO_113

GPIO_014 19 17 18 20 GPIO_015 GPIO_114 19 17 18 20 GPIO_115

GPIO_016 21 19 20 22 GPIO_017 GPIO_116 21 19 20 22 GPIO_117

C 21 22 21 22 C

GPIO_018 23 24 GPIO_019 GPIO_118 23 24 GPIO_119

GPIO_020 25 23 24 26 GPIO_021 GPIO_120 25 23 24 26 GPIO_121

GPIO_022 27 25 26 28 GPIO_023 GPIO_122 27 25 26 28 GPIO_123

29 27 28 30 29 27 28 30

VCC3P3 29 30 VCC3P3 29 30

GPIO_024 31 32 GPIO_025 GPIO_124 31 32 GPIO_125

GPIO_026 33 31 32 34 GPIO_027 GPIO_126 33 31 32 34 GPIO_127

GPIO_028 35 33 34 36 GPIO_029 GPIO_128 35 33 34 36 GPIO_129

GPIO_030 37 35 36 38 GPIO_031 GPIO_130 37 35 36 38 GPIO_131

GPIO_032 39 37 38 40 GPIO_033 GPIO_132 39 37 38 40 GPIO_133

39 40 39 40

GPIO_2[12..0]

GPIO_2_IN[2..0]

Analog_In[7..0]

B B

GPIO - 2

JP3

VCC3P3 1 2 GPIO_2_IN0

GPIO_2_IN1 3 1 2 4 GPIO_2_IN2

GPIO_20 5 3 4 6 GPIO_21

GPIO_22 7 5 6 8 GPIO_23

GPIO_24 9 7 8 10 GPIO_25

GPIO_26 11 9 10 12 GPIO_27

GPIO_28 13 11 12 14 GPIO_29

GPIO_210 15 13 14 16 GPIO_211

GPIO_212 17 15 16 18 Analog_In5

Analog_In6 19 17 18 20 Analog_In7

Analog_In3 21 19 20 22 Analog_In2

Analog_In4 23 21 22 24 Analog_In0

Analog_In1 25 23 24 26

25 26

2X13 HEADER

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B GPIOs & 2X13 Header C

Date: Thursday, July 12, 2012 Sheet 10 of 14

5 4 3 2 1

5 4 3 2 1

D D

VCC3P3_VA VCC3P3

R16 49.9

Analog_In[7..0] C42 C43 C44 C45

1u 0.1u 1u 0.1u

VCC3P3

Digital Accelerometer AGND AGND

Analog_In0 R17 22 ADC_IN0

VCC3P3_VA VCC3P3

VCC_VS C46

1n

R18 U3

13

2

1 14 I2C_SCLK VCC3P3 U4

DNI 2.2K 2 VDD SCL_SCLK 13 I2C_SDAT AGND

VA

VD

3 GND SDA_SDI_SDIO 12 R19 10K Analog_In1 R20 22 ADC_IN1

4 RESERVED SDO_ALT_ADDRESS 11 ADC_IN0 4 1 ADC_CS_N

C GND RESERVED_1 IN0 CS_n C

C47 1u 5 10 C48 ADC_IN1 5

6 GND NC 9 R62 0 ADC_IN2 6 IN1 14 ADC_SADDR

G_SENSOR_CS_N 7 VS INT2 8 DNI R21 1n ADC_IN3 7 IN2 DIN

CS_n INT1 ADC_IN4 8 IN3 15 ADC_SDAT

ADXL345 DNI 2.2K ADC_IN5 9 IN4 DOUT

C49 0.1u VCC_VS AGND ADC_IN6 10 IN5 16 ADC_SCLK

Analog_In2 R22 22 ADC_IN2 ADC_IN7 11 IN6 SCLK

G_SENSOR_INT IN7

C50

DGND

AGND

1n

ADC128S022CIMTX

12

AGND

Analog_In3 R24 22 ADC_IN3

VCC3P3 VCC_VS

VCC_VS C51

AGND

1n

L3 BEAD C52 C53

L4

4.7u 0.1u AGND

Analog_In4 R25 22 ADC_IN4

BEAD

B B

C54 AGND

1n

AGND

Analog_In5 R26 22 ADC_IN5

C55

1n

AGND

Analog_In6 R27 22 ADC_IN6

C56

1n

AGND

Analog_In7 R28 22 ADC_IN7

A A

C57

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

1n All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

AGND

DE0-Nano Board

Size Document Number Rev

B G-Sensor & ADC C

Date: Thursday, July 12, 2012 Sheet 11 of 14

5 4 3 2 1

5 4 3 2 1

DRAM_DQ[15..0]

DRAM_ADDR[12..0] VCC3P3

D D

DRAM_DQM[1..0]

14

27

43

49

1

3

9

U5

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

DRAM_ADDR0 23 2 DRAM_DQ0

DRAM_ADDR1 24 A0 D0 4 DRAM_DQ1

DRAM_ADDR2 25 A1 D1 5 DRAM_DQ2

DRAM_ADDR3 26 A2 D2 7 DRAM_DQ3

DRAM_ADDR4 29 A3 D3 8 DRAM_DQ4

DRAM_ADDR5 30 A4 D4 10 DRAM_DQ5

DRAM_ADDR6 31 A5 D5 11 DRAM_DQ6

DRAM_ADDR7 32 A6 D6 13 DRAM_DQ7

DRAM_ADDR8 33 A7 D7 42 DRAM_DQ8

DRAM_ADDR9 34 A8 D8 44 DRAM_DQ9

DRAM_ADDR10 22 A9 D9 45 DRAM_DQ10

DRAM_ADDR11 35 A10 D10 47 DRAM_DQ11

C C

DRAM_ADDR12 36 A11 SDRAM 16Mx16 D11 48 DRAM_DQ12

DRAM_CLK 38 A12 D12 50 DRAM_DQ13

DRAM_CKE 37 CLK D13 51 DRAM_DQ14

DRAM_DQM0 15 CKE D14 53 DRAM_DQ15

DRAM_DQM1 39 LDQM D15

UDQM

DRAM_WE_N 16

DRAM_CAS_N 17 nWE

DRAM_RAS_N 18 nCAS

DRAM_CS_N 19 nRAS

DRAM_BA0 20 nCS

DRAM_BA1 21 BA0

BA1

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

28

41

54

6

12

46

52

B B

VCC3P3

C58 C59 C60 C61 C62 C63 C64

0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

A All rights reserved. A

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

A SDRAM C

Date: Thursday, July 12, 2012 Sheet 12 of 14

5 4 3 2 1

5 4 3 2 1

D D

VCC3P3

VCC3P3

R29 R30 R31

0 0 0 VCC3P3 R32 R33 VCC3P3

U6 2K 2K

DNI DNI DNI 1 8 C65

2 A0 VCC 7

3 A1 WP 6 I2C_SCLK 0.1u

C C

4 A2 SCL 5 I2C_SDAT

VSS SDA

R34 R35 24LC02B

9

1K 1K R36

1K I2C ADDRESS W/R = 0xA0/0xA1

B B

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

A All rights reserved. A

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

A EEPROM C

Date: Thursday, July 12, 2012 Sheet 13 of 14

5 4 3 2 1

5 4 3 2 1

5V Power from USB Port VCC_SYS REG1 VCC3P3

2 7

D5 R60 0 3 IN OUT 6

VCC5_USB

4 IN OUT 5

3.3V/1.5A

PMEG2010AEB J1 IN OUT C67 C68

1 2 C66 8 R37

GND

DAP

D D6 ADJ 10u 0.1u D

5.36K

SIP2 DNI 10u

PMEG2010AEB LP38500SD-ADJ

1

9

VCC3P3

JP4

1 D7

2 R38

PMEG2010AEB 1.2K

Power - HDR R40

D8

Input Power Range: 120

3.6 ~ 5.7 V PMEG2010AEB VCC_SYS Range:

3.3 ~ 5.5 V

D2

POWER

LEDB

J5 VCC3P3

1 VCC_SYS

2

DNI 3 R45

C C

4 DNI 0

REG2

1X4 HEADER

R46 0 6 1

J6 VIN VOUT VCC2P5 2.5V/150mA

C69 2 C70 C71

1 R47 4 NC1 5

VCC1P2 VEN NC2

2 0.47u 10K 0.47u 0.1u

DNI 3

GND

VCC3P3

PAD

4

LP5900SD-2.5

7

1X4 HEADER

B B

VCC3P3 REG3 VCC1P2

2 7

MH1 MH2 MH3 MH4 R61 0 3 IN OUT 6

4 IN OUT 5

1.2V/1.5A

J2 IN OUT C72 C74

C73 1 2 8 R48

GND

DAP

ADJ 10u 0.1u

4.99K

10u SIP2 DNI

LP38500SD-ADJ

1

9

FID1 FID2 FID3 FID4 FID5 FID6 FID7 FID8

R49

4.99K

A A

Copyright (c) 2007 by Terasic Technologies Inc. Taiwan.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

Title

DE0-Nano Board

Size Document Number Rev

B 1.2V & 2.5V & 3.3V C

Date: Thursday, July 12, 2012 Sheet 14 of 14

5 4 3 2 1

You might also like

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Financial CrisisDocument53 pagesFinancial CrisisMehedi Hassan RanaNo ratings yet

- Tomtom One XL SchematicDocument11 pagesTomtom One XL Schematicsuysuy00100% (1)

- Beginning Arduino Nano 33 IoT: Step-By-Step Internet of Things ProjectsFrom EverandBeginning Arduino Nano 33 IoT: Step-By-Step Internet of Things ProjectsNo ratings yet

- Practical Embedded Controllers: Design and Troubleshooting with the Motorola 68HC11From EverandPractical Embedded Controllers: Design and Troubleshooting with the Motorola 68HC11No ratings yet

- The New 3D Layout for Oil & Gas Offshore Projects: How to ensure successFrom EverandThe New 3D Layout for Oil & Gas Offshore Projects: How to ensure successRating: 4.5 out of 5 stars4.5/5 (3)

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocument67 pagesAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaNo ratings yet

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- Credit Cards: Personal FinanceDocument36 pagesCredit Cards: Personal FinanceAmara MaduagwuNo ratings yet

- IWCF Equipment اسئله Sep 18 MaerskDocument56 pagesIWCF Equipment اسئله Sep 18 MaerskAboZaidNo ratings yet

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Bridge Engineering by Christian MennDocument446 pagesBridge Engineering by Christian MennSandeep SonyNo ratings yet

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCFrom EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNo ratings yet

- AOM NO. 01-Unserviceable PPEDocument3 pagesAOM NO. 01-Unserviceable PPERagnar LothbrokNo ratings yet

- PM-Practice Management System Procurement - Project-CharterDocument14 pagesPM-Practice Management System Procurement - Project-CharterXozan100% (1)

- PIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsFrom EverandPIC32 Microcontrollers and the Digilent Chipkit: Introductory to Advanced ProjectsRating: 5 out of 5 stars5/5 (1)

- M57TE V1.4: Rev. Date Description RemarkDocument9 pagesM57TE V1.4: Rev. Date Description RemarkjmkcbeNo ratings yet

- Shuttle B10ie01 - 71rb10ie0-9ha0 - T8a0 - Rev ADocument23 pagesShuttle B10ie01 - 71rb10ie0-9ha0 - T8a0 - Rev AJoão Luis N. Do AmaralNo ratings yet

- BRD2201A A02 SchematicDocument10 pagesBRD2201A A02 Schematickunalkundanam1046No ratings yet

- Clevo W243HUQ W244HUQ 6-7P-W24H5-002 WWW - MYCOMP.SUDocument42 pagesClevo W243HUQ W244HUQ 6-7P-W24H5-002 WWW - MYCOMP.SURafaNotes SmartsNo ratings yet

- Samsung Sch-A410 Service ManualDocument30 pagesSamsung Sch-A410 Service Manualsaboor ashraf100% (1)

- MTK 6218 SchematicsDocument5 pagesMTK 6218 SchematicssajjadfattahNo ratings yet

- DE0 ReleaseDocument19 pagesDE0 Releasedoniz30No ratings yet

- P+5V P+5V: Power On MuteDocument8 pagesP+5V P+5V: Power On MuteuyrikNo ratings yet

- Ts 4900 Schematic PDFDocument7 pagesTs 4900 Schematic PDFPrashanth KumarNo ratings yet

- A14IEXX Positivo UniqueDocument26 pagesA14IEXX Positivo UniqueJhonatan KalitaNo ratings yet

- Cy2 Fpga Starter Board SchematicDocument21 pagesCy2 Fpga Starter Board SchematicFerry HidayatNo ratings yet

- Arduino Yun SchematicDocument7 pagesArduino Yun SchematicgetmicrosNo ratings yet

- TM 7043Document13 pagesTM 7043Radek KurekNo ratings yet

- At3u Si 0502aDocument37 pagesAt3u Si 0502aAshok JangraNo ratings yet

- Hawkboard Schematics v1Document11 pagesHawkboard Schematics v1Sam KhawseNo ratings yet

- Samsung GT-C3322 Metro Duos SchematicsDocument3 pagesSamsung GT-C3322 Metro Duos SchematicsTerry MetamorfosaNo ratings yet

- Scheme-Hp Pavilion Dv5 - Intel Qt6Document44 pagesScheme-Hp Pavilion Dv5 - Intel Qt6sergeybezrNo ratings yet

- Ak1 MB 1213aDocument30 pagesAk1 MB 1213aAshok JangraNo ratings yet

- Samsung GT-E3210 08 Level 3 Repair - Block-, PCB Diagrams, Flow Chart of TroubleshootingDocument38 pagesSamsung GT-E3210 08 Level 3 Repair - Block-, PCB Diagrams, Flow Chart of TroubleshootingAmat Sofiyan100% (1)

- Acer Aspire-5510 Schematic DiagramDocument40 pagesAcer Aspire-5510 Schematic DiagramAbubakar SidikNo ratings yet

- MCD Demo2 Manual enDocument33 pagesMCD Demo2 Manual enmario_villarreal_110% (1)

- Pickit 2 Clone SMDDocument6 pagesPickit 2 Clone SMDJoc AntNo ratings yet

- Smoothieboard 5driver SchematicDocument4 pagesSmoothieboard 5driver SchematicdududadamikeNo ratings yet

- Albion: Index - Alb522MbDocument18 pagesAlbion: Index - Alb522MbShauna MooreNo ratings yet

- LG r510 - Quanta Ql8 Tw8 - Rev 3asecDocument41 pagesLG r510 - Quanta Ql8 Tw8 - Rev 3asecGerson SoaresNo ratings yet

- DCT700 ph0Document14 pagesDCT700 ph0waltech2005100% (1)

- HP Compaq Presario Cq61 Quanta Op6 Op7 Tango Ballet Rev A SCHDocument37 pagesHP Compaq Presario Cq61 Quanta Op6 Op7 Tango Ballet Rev A SCHHugo G.No ratings yet

- Un32c5000 - 40C5000 - 46C5000 MainDocument16 pagesUn32c5000 - 40C5000 - 46C5000 Mainmj15015No ratings yet

- Acer I5 47501306462469980Document67 pagesAcer I5 47501306462469980fdsaq12No ratings yet

- So Do Nb2dsk01Document72 pagesSo Do Nb2dsk01maithuong85No ratings yet

- Intel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197AklftDocument50 pagesIntel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197Aklftdrop9721No ratings yet

- Ts 7500 SchematicDocument4 pagesTs 7500 Schematicimransiddiquiatvxt100% (1)

- Engineering Service Revenues World Summary: Market Values & Financials by CountryFrom EverandEngineering Service Revenues World Summary: Market Values & Financials by CountryNo ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Marine Machinery, Equipment & Supplies Wholesale Revenues World Summary: Market Values & Financials by CountryFrom EverandMarine Machinery, Equipment & Supplies Wholesale Revenues World Summary: Market Values & Financials by CountryNo ratings yet

- Simple Electronics with GPIO Zero: Take Control of the Real World With your Raspberry PiFrom EverandSimple Electronics with GPIO Zero: Take Control of the Real World With your Raspberry PiRating: 5 out of 5 stars5/5 (1)

- Fluidic Components and Equipment 1968–9: Pergamon Electronics Data SeriesFrom EverandFluidic Components and Equipment 1968–9: Pergamon Electronics Data SeriesNo ratings yet

- 5000 RM-362/RM-363 Service Manual Level 1&2Document0 pages5000 RM-362/RM-363 Service Manual Level 1&2Alexander LempelzivNo ratings yet

- Stratocaster Service ManualDocument4 pagesStratocaster Service ManualAlexander LempelzivNo ratings yet

- Flash ProgrammingDocument5 pagesFlash ProgrammingAlexander LempelzivNo ratings yet

- Altera De0-NanoDocument153 pagesAltera De0-NanoAlexander LempelzivNo ratings yet

- Physician-Induced Demand: EM Johnson, Massachusetts Institute of Technology, Cambridge, MA, USADocument6 pagesPhysician-Induced Demand: EM Johnson, Massachusetts Institute of Technology, Cambridge, MA, USAAnonymous mDkBoIyhjlNo ratings yet

- Ipe1735v2 1610 1 0 d01Document6 pagesIpe1735v2 1610 1 0 d01li nuohaiNo ratings yet

- Textbook Thermal Power Plant Control and Instrumentation The Control of Boilers and Hrsgs 2Nd Edition David Lindsley Ebook All Chapter PDFDocument53 pagesTextbook Thermal Power Plant Control and Instrumentation The Control of Boilers and Hrsgs 2Nd Edition David Lindsley Ebook All Chapter PDFtim.bass844100% (1)

- Module 3 CSMDocument31 pagesModule 3 CSMmayankgami27No ratings yet

- Every Child Matters A Practical Guide For Teachers PDFDocument2 pagesEvery Child Matters A Practical Guide For Teachers PDFBarbaraNo ratings yet

- Radiodermatitis India TransDocument14 pagesRadiodermatitis India TransNaufal Fadhil Mufid LazuardiNo ratings yet

- Present Value, Annuity, and PerpetuityDocument42 pagesPresent Value, Annuity, and PerpetuityEdwin OctorizaNo ratings yet

- 8MA0 21 Que 20211014Document16 pages8MA0 21 Que 20211014S1mple GamingNo ratings yet

- Cell FlexDocument2 pagesCell Flexandrewb2005No ratings yet

- NCR Hp6592Document2 pagesNCR Hp6592k19ajayNo ratings yet

- Types of Extrusion and Extrusion Equipment: NPTEL - Mechanical Engineering - FormingDocument8 pagesTypes of Extrusion and Extrusion Equipment: NPTEL - Mechanical Engineering - FormingtechopelessNo ratings yet

- CM 801 A Process Piping Design Dec 2020Document2 pagesCM 801 A Process Piping Design Dec 2020RAHUL MATHURNo ratings yet

- 105 Mid-Week AssignmentDocument4 pages105 Mid-Week AssignmentSandhya SharmaNo ratings yet

- 20th Century Arch'ReDocument6 pages20th Century Arch'ReRachelleGomezLatrasNo ratings yet

- Stacey Bilte Resume 2014Document4 pagesStacey Bilte Resume 2014api-298461968No ratings yet

- Refrigeration Systems & Comparative Study of VCRSDocument12 pagesRefrigeration Systems & Comparative Study of VCRSShashi Bhushan KumarNo ratings yet

- Lesson PlanDocument6 pagesLesson Plannurulhuda287No ratings yet

- 1 Preparing Persuasive MessagesDocument14 pages1 Preparing Persuasive MessagesAmit GiriNo ratings yet

- Paper 1Document36 pagesPaper 1warnereditsproNo ratings yet

- The Real Business Cycle Model: Quantitative MacroeconomicsDocument36 pagesThe Real Business Cycle Model: Quantitative MacroeconomicsAmil MusovicNo ratings yet

- Automatic Three Phase Induction Motor Star - Delta Starter: A Project Report Submitted at D N Polytechnic MeerutDocument31 pagesAutomatic Three Phase Induction Motor Star - Delta Starter: A Project Report Submitted at D N Polytechnic MeerutDeepanshu SinghNo ratings yet

- Mother Tongue LessonsDocument6 pagesMother Tongue LessonsPrincess CuevasNo ratings yet

- Rurban PowerPoint Presentation Final OneDocument65 pagesRurban PowerPoint Presentation Final OneVIVEK VERMANo ratings yet

- Master Syllabus Fix TOM-JAN2019-BOED PDFDocument4 pagesMaster Syllabus Fix TOM-JAN2019-BOED PDFBogiNo ratings yet