Professional Documents

Culture Documents

Alu PDF

Alu PDF

Uploaded by

Muh Nur FauziOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Alu PDF

Alu PDF

Uploaded by

Muh Nur FauziCopyright:

Available Formats

Tele 2060

A Simple Processor Architecture

Register 1

Register 2

Input

Register 7

Decoder B Select Multiplexer Multiplexer A Select

B Bus A Bus

Destination

Select ALU

Function

S Z V C Select

Shifter Shift

Select

Output

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 1 University of Pittsburgh

Tele 2060

ALU

• Performs Arithmentic Functions

• Performs Logic Functions

• Function is Selected by Control

• Status Bits

C - Carry

V - Overflow

Z = 1 If Resultant Contains All Zeros

S - Sign Bit of the Result

• Decoder Selects Destination for the Resultant

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 2 University of Pittsburgh

Tele 2060

ALU

• Inputs

Operands

Input Carry

Operation Select

Add

Subtract

AND

OR

XOR

Mode (Arithmetic or Logic) Select

• Outputs

Resultant

Output Carry

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 3 University of Pittsburgh

Tele 2060

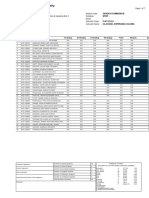

ALU Function Table

Operation Select

S2 S1 S0 Cin Operation Function

0 0 0 0 F=A Transfer A

0 0 0 1 F=A+1 Increment A

0 0 1 0 F=A+B Add A and B

0 0 1 1 F=A+B+1 Add A and B With Carry

0 1 0 0 F=A+B’ Add A and One’s Compement of B

0 1 0 1 F=A+B’+1 Subtract B From A

0 1 1 0 F=A-1 Decrement A

0 1 1 1 F=A Transfer A

1 0 0 0 F=AB AND

1 0 1 0 F=A+B OR

1 1 0 0 F=A XOR B Exclusive OR

1 1 1 0 F=A’ Complement

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 4 University of Pittsburgh

Tele 2060

ALU Components

• Arithmetic

Parallel Add

One Full Adder per Bit

Selection Logic

• Logic

Gates

Multiplexer

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 5 University of Pittsburgh

Tele 2060

Circuit for Arithmetic Component

Cin

S0

S1

A1 X1 C1

Full F1

B1 Adder

Y1

A2 X2 C2

Full F2

B2 Adder

Y2

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 6 University of Pittsburgh

Tele 2060

Circuit for Logic Component

S0

S1

An

MUX Fn

Bn

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 7 University of Pittsburgh

Tele 2060

Internal Structure of ALU

Cn-1

An

Bn Arithmetic

Stage

Multiplexer Fn

Logic

Stage

S0

S1

S2

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 8 University of Pittsburgh

Tele 2060

Shifter

• General

Extension of Shift Register Circuit is Possible

This Requires Several Clock Pulses

This is Time Consuming

• Alternate Approach (Figure 7-18, p. 246 of Mano)

Use Multiplexers

Wire to Cause Shift Effect

Control Determines Nature of Shift

Thus, a Single Clock Cycle is Used

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 9 University of Pittsburgh

Tele 2060

Control Unit Requirements

• MUX A Selector

• MUX B Selector

• ALU Operation Selector

• Shift Selector

• Destination Selector

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 10 University of Pittsburgh

Tele 2060

Control Word

• Number and Organization of Bits Required to Control ALU

• Bit Requirements

A: A Bus Select (Seven Registers Plus Input): 3 bits

B: B Bus Select (Seven Registers Plus Input): 3 bits

D: Destination Select (Seven Registers): 3 bits

F: ALU Control (Four bits)

H: Shift Control (Three bits)

TOTAL = 16 bits

Thus, 16 Bits Can Be Used to Perform All Microoperations

A B D F H

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 11 University of Pittsburgh

Tele 2060

Control Word Encoding

Operation (F)

Code Cin = 0 Cin = 1 A B D H

0 0 0 F=A F=A+1 Input Input None No Shift

0 0 1 F=A+B F=A+B+1 R1 R1 R1 SHL

0 1 0 F=A+B’ F=A+B’+1 R2 R2 R2 SHR

0 1 1 F=A-1 F=A R3 R3 R3 Bus=0

1 0 0 F=AB R4 R4 R4

1 0 1 F=A+B R5 R5 R5 ROL

1 1 0 F=A XOR B R6 R6 R6 ROR

1 1 1 F=A’ R7 R7 R7

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 12 University of Pittsburgh

Tele 2060

Microoperations and Microprograms

• Example Microoperation

R1← R2 - R3

Symbolically: R2,R3,R1,F=A-B,No Shift

Control Word = 010 011 001 0101 000 = 4CA8 (H)

• Clearly, Many Microoperations Are Possible

• Control Memory

Location of Available Microoperations

Width of Control Memory = Control Word

• Microprograms Can be Written Using a Sequence of

Microoperations

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 13 University of Pittsburgh

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Learner - BSBLDR602 Provide Leadership Across The OrganisationDocument37 pagesLearner - BSBLDR602 Provide Leadership Across The OrganisationIrtaqa Raza0% (1)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- GP Prelim Questions 2018Document5 pagesGP Prelim Questions 2018arielhoNo ratings yet

- Victims of Cybercrime Attacks Cybercrime Victims More Likely To BeDocument2 pagesVictims of Cybercrime Attacks Cybercrime Victims More Likely To BeKristavilla OlavianoNo ratings yet

- Components of Culture: Reported By: Kristavilla C. OlavianoDocument13 pagesComponents of Culture: Reported By: Kristavilla C. OlavianoKristavilla OlavianoNo ratings yet

- Vertical MotionDocument41 pagesVertical MotionKristavilla OlavianoNo ratings yet

- Introduction To Visual BasicDocument23 pagesIntroduction To Visual BasicKristavilla OlavianoNo ratings yet

- 2012 Math Challenge-Individual Finals (GR I - VI)Document12 pages2012 Math Challenge-Individual Finals (GR I - VI)Kristavilla OlavianoNo ratings yet

- Assignment 231 Engg EconomyDocument1 pageAssignment 231 Engg EconomyKristavilla OlavianoNo ratings yet

- Pricelist LettersizeDocument3 pagesPricelist LettersizeKristavilla OlavianoNo ratings yet

- 3.11 Evaluation of Job Related Hazards and Development of Safety ProceduresDocument16 pages3.11 Evaluation of Job Related Hazards and Development of Safety ProceduresKristavilla OlavianoNo ratings yet

- PNPACAT 2015 PARTIAL LIST 2nd POSTINGDocument427 pagesPNPACAT 2015 PARTIAL LIST 2nd POSTINGKristavilla OlavianoNo ratings yet

- PNPACAT 2015 PARTIAL LIST 2nd POSTINGDocument427 pagesPNPACAT 2015 PARTIAL LIST 2nd POSTINGKristavilla OlavianoNo ratings yet

- EE 361L Lab 4.2. 4 Bit Arithmetic Logic Unit (ALU)Document1 pageEE 361L Lab 4.2. 4 Bit Arithmetic Logic Unit (ALU)Kristavilla OlavianoNo ratings yet

- Operating System Structures: Meelis R Mroos@ut - EeDocument24 pagesOperating System Structures: Meelis R Mroos@ut - EeKristavilla OlavianoNo ratings yet

- 372 5Document5 pages372 5Phillip TaylorNo ratings yet

- DocDocument7 pagesDocKristavilla OlavianoNo ratings yet

- Sequential PDFDocument16 pagesSequential PDFKristavilla OlavianoNo ratings yet

- 0671C GI-790 BK (Rev26Aug16)Document7 pages0671C GI-790 BK (Rev26Aug16)Kristavilla OlavianoNo ratings yet

- Catalogo Gates XPB-5VXDocument2 pagesCatalogo Gates XPB-5VXCristian Alejandro SalvatierraNo ratings yet

- Lampiran 11Document19 pagesLampiran 11septa bhilal al azizNo ratings yet

- Ajc 5Mar2022152642GMT 1646494002839homeworkDocument4 pagesAjc 5Mar2022152642GMT 1646494002839homeworkFarah TounsiNo ratings yet

- Ac Compressor Model - 5h66Document32 pagesAc Compressor Model - 5h66sting12345100% (2)

- Topic 4 - Implementing HRD ProgrammeDocument20 pagesTopic 4 - Implementing HRD ProgrammeHassan SallehNo ratings yet

- Ethical Considerations in ResearchDocument12 pagesEthical Considerations in ResearchScholarNo ratings yet

- Turbocompounding TechnologyDocument23 pagesTurbocompounding TechnologyPawan BeniwalNo ratings yet

- Railway CrossingDocument18 pagesRailway Crossingshivendra singhNo ratings yet

- EnfuncDocument102 pagesEnfuncRafael OlaveNo ratings yet

- District Industrial Profile: Government of India Ministry of MSMEDocument21 pagesDistrict Industrial Profile: Government of India Ministry of MSMETimmaNo ratings yet

- Users of Financial StatementsDocument21 pagesUsers of Financial StatementsRomar SayoNo ratings yet

- ROUTINE BCSE (AIML) - Sec-G - Sem-1Document1 pageROUTINE BCSE (AIML) - Sec-G - Sem-1weyekim600No ratings yet

- Online ExamDocument5 pagesOnline Exampraful_kohale6642No ratings yet

- Purchase Order ItemsDocument3 pagesPurchase Order ItemsYasir SaeedNo ratings yet

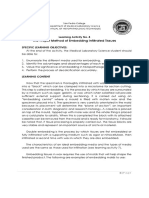

- Act. 8 - Proper Method of Embedding Infiltrated TissuesDocument4 pagesAct. 8 - Proper Method of Embedding Infiltrated Tissueschristian Jay HorseradaNo ratings yet

- Classical Problems of SynchronizationDocument18 pagesClassical Problems of SynchronizationyashNo ratings yet

- Numerical Metods Chapter 1 & 2Document35 pagesNumerical Metods Chapter 1 & 2Naren Sundararajan100% (1)

- Semere Tesfaye MBAO-8977-14BDocument8 pagesSemere Tesfaye MBAO-8977-14Bamirhaile71No ratings yet

- Chapter 5 SFTDocument26 pagesChapter 5 SFTtendulkarnishchalNo ratings yet

- Chapter 6 AnswersDocument2 pagesChapter 6 Answersaiwen_wong2428No ratings yet

- India TodayDocument114 pagesIndia TodayRavishankarNo ratings yet

- User Manual: Document No. 4328. Issue 1.01 - 18/04/2019Document38 pagesUser Manual: Document No. 4328. Issue 1.01 - 18/04/2019Mauricio Cruz FigueroaNo ratings yet

- Post Covid 19 Developing A Homestay Business by Adopting A Social Entrepreneurship Approach PDFDocument11 pagesPost Covid 19 Developing A Homestay Business by Adopting A Social Entrepreneurship Approach PDFMohd Jamalil Azam MustafaNo ratings yet

- Final Output HRMDocument3 pagesFinal Output HRMDanilo MaglinteNo ratings yet

- Validation of Total Pain Questionnaire in Post Spinal Surgery SyndromeDocument1 pageValidation of Total Pain Questionnaire in Post Spinal Surgery SyndromeBiplab SarkarNo ratings yet

- Journal of Geometry and Physics: Serge TabachnikovDocument8 pagesJournal of Geometry and Physics: Serge TabachnikovSAMUEL MAURICIO CRUZ DIAZNo ratings yet

- Module 1: Overview of Modern PhysicsDocument32 pagesModule 1: Overview of Modern PhysicsKay LagunaNo ratings yet

- Artists in East LondonDocument68 pagesArtists in East Londongui_koghiNo ratings yet