Professional Documents

Culture Documents

24C64 PDF

24C64 PDF

Uploaded by

benoit lemayOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

24C64 PDF

24C64 PDF

Uploaded by

benoit lemayCopyright:

Available Formats

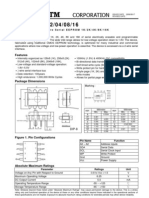

24AA64/24LC64

64K I2C™CMOS Serial EEPROM

DEVICE SELECTION TABLE PACKAGE TYPE

8-LEAD PDIP

Part Vcc Max Clock Temp

Number Range Frequency Ranges A0 1 8 Vcc

†

24AA64 1.8-5.5V 400 kHz C

24xx64

A1 2 7 WP

24LC64 2.5-5.5V 400 kHz I, E

† A2 3 6 SCL

100 kHz for Vcc < 2.5V.

Vss 4 5 SDA

FEATURES

• Low power CMOS technology

- Maximum write current 3 mA at 5.5V

- Maximum read current 400 µA at 5.5V 8-LEAD SOIC

- Standby current 100 nA typical at 5.5V 1 8

A0 Vcc

• 2-wire serial interface bus, I2C compatible

24xx64

2 7 WP

• Cascadable for up to eight devices A1

• Self-timed ERASE/WRITE cycle 3 6 SCL

A2

• 32-byte page or byte write modes available 4 5

Vss SDA

• 5 ms max write cycle time

• Hardware write protect for entire array

• Output slope control to eliminate ground bounce 8-LEAD TSSOP

• Schmitt trigger inputs for noise suppression 1 8

WP SCL

24xx64

• 1,000,000 erase/write cycles guaranteed 2 7

Vcc SDA

• Electrostatic discharge protection > 4000V 6

A0 3 Vss

• Data retention > 200 years 5

A1 4 A2

• 8-pin PDIP, SOIC (150 and 208 mil) and TSSOP

packages

• Temperature ranges:

- Commercial (C): 0° to 70°C

BLOCK DIAGRAM

- Industrial (I): -40°C to +85°C

A0 A1 A2 WP HV GENERATOR

- Automotive (E) -40°C to +125°C

DESCRIPTION

I/O MEMORY EEPROM

The Microchip Technology Inc. 24AA64/24LC64 CONTROL CONTROL XDEC ARRAY

LOGIC LOGIC

(24xx64*) is a 8K x 8 (64K bit) Serial Electrically Eras-

able PROM capable of operation across a broad volt- PAGE LATCHES

age range (1.8V to 5.5V). It has been developed for

advanced, low power applications such as personal I/O

SCL

communications or data acquisition. This device also YDEC

has a page-write capability of up to 32 bytes of data.

This device is capable of both random and sequential SDA

reads up to the 64K boundary. Functional address lines

allow up to eight devices on the same bus, for up to 512 VCC

Kbits address space. This device is available in the VSS SENSE AMP

standard 8-pin plastic DIP, 8-pin SOIC (150 and R/W CONTROL

208 mil), and 8-pin TSSOP.

I2C is a trademark of Philips Corporation.

*24xx64 is used in this document as a generic part number for the 24AA64/24LC64 devices.

2000 Microchip Technology Inc. DS21189D-page 1

24AA64/24LC64

1.0 ELECTRICAL TABLE 1-1 PIN FUNCTION TABLE

CHARACTERISTICS

Name Function

1.1 Maximum Ratings* A0,A1,A2 User Configurable Chip Selects

Vcc .................................................................................................7.0V VSS Ground

All inputs and outputs w.r.t. Vss .............................. -0.6V to Vcc +1.0V SDA Serial Data

Storage temperature ...................................................-65°C to +150°C

Ambient temp. with power applied ..............................-65°C to +125°C SCL Serial Clock

Soldering temperature of leads (10 seconds) ........................... +300°C

ESD protection on all pins .................................................................≥ 4 kV WP Write Protect Input

*Notice: Stresses above those listed under “Maximum Ratings” may VCC +1.8 to 5.5V (24AA64)

cause permanent damage to the device. This is a stress rating only and

functional operation of the device at those or any other conditions +2.5 to 5.5V (24LC64)

above those indicated in the operational listings of this specification is

not implied. Exposure to maximum rating conditions for extended peri-

ods may affect device reliability.

TABLE 1-2 DC CHARACTERISTICS

All parameters apply across the rec- Commercial (C): VCC = +1.8V to 5.5V Tamb = 0°C to +70°C

ommended operating ranges unless Industrial (I): VCC = +2.5V to 5.5V Tamb = -40°C to +85°C

otherwise noted. Automotive (E): VCC = +2.5V to 5.5V Tamb = -40°C to 125°C

Parameter Symbol Min Max Units Conditions

A0, A1, A2,

SCL, SDA, and WP pins:

High level input voltage VIH 0.7 VCC — V

Low level input voltage VIL — 0.3 VCC V VCC ≥ 2.5V

0.2 VCC V VCC < 2.5V

Hysteresis of Schmitt Trigger VHYS 0.05 VCC — V VCC > 2.5V (Note)

inputs (SDA, SCL pins)

Low level output voltage VOL — 0.40 V IOL = 3.0 mA @ VCC = 4.5V

IOL = 2.1 mA @ VCC = 2.5V

Input leakage current ILI -10 10 µA VIN = Vss to VCC, WP = VSS

VIN = Vss or VCC, WP = VCC

Output leakage current ILO -10 10 µA VOUT = Vss to VCC

Pin capacitance CIN, COUT — 10 pF VCC = 5.0V (Note)

(all inputs/outputs) Tamb = 25°C, fc= 1 MHz

Operating current ICC Write — 3 mA VCC = 5.5V

ICC Read — 400 µA VCC = 5.5V, SCL = 400 kHz

Standby current ICCS — 1 µA SCL = SDA = VCC = 5.5V

A0, A1, A2, WP = VSS

Note: This parameter is periodically sampled and not 100% tested.

FIGURE 1-1: BUS TIMING DATA

TF THIGH VHYS TR

SCL

TSU:STA

TLOW THD:DAT TSU:DAT TSU:STO

SDA

THD:STA

IN TSP

TBUF

TAA

SDA

OUT

WP (protected) THD:WP

TSU:WP

(unprotected)

DS21189D-page 2 2000 Microchip Technology Inc.

24AA64/24LC64

TABLE 1-3 AC CHARACTERISTICS

All parameters apply across the spec- Commercial (C): VCC = +1.8V to 5.5V Tamb = 0°C to +70°C

ified operating ranges unless other- Industrial (I): VCC = +2.5V to 5.5V Tamb = -40°C to +85°C

wise noted. Automotive (E): VCC = +2.5V to 5.5V Tamb = -40°C to 125°C

Parameter Symbol Min Max Units Conditions

Clock frequency FCLK — 100 kHz 1.8V ≤ VCC ≤ 2.5V

— 400 2.5V ≤ VCC ≤ 5.5V

Clock high time THIGH 4000 — ns 1.8V ≤ VCC ≤ 2.5V

600 — 2.5V ≤ VCC ≤ 5.5V

Clock low time TLOW 4700 — ns 1.8V ≤ VCC ≤ 2.5V

1300 — 2.5V ≤ VCC ≤ 5.5V

SDA and SCL rise time TR — 1000 ns 1.8V ≤ VCC ≤ 2.5V

(Note 1) — 300 2.5V ≤ VCC ≤ 5.5V

SDA and SCL fall time TF — 300 ns (Note 1)

START condition hold time THD:STA 4000 — ns 1.8V ≤ VCC ≤ 2.5V

600 — 2.5V ≤ VCC ≤ 5.5V

START condition setup time TSU:STA 4700 — ns 1.8V ≤ VCC ≤ 2.5V

600 — 2.5V ≤ VCC ≤ 5.5V

Data input hold time THD:DAT 0 — ns (Note 2)

Data input setup time TSU:DAT 250 — ns 1.8V ≤ VCC ≤ 2.5V

100 — 2.5V ≤ VCC ≤ 5.5V

STOP condition setup time TSU:STO 4000 — ns 1.8V ≤ VCC ≤ 2.5V

600 — 2.5V ≤ VCC ≤ 5.5V

WP setup time TSU:WP 4000 — ns 1.8V ≤ VCC ≤ 2.5V

600 — 2.5V ≤ VCC ≤ 5.5V

WP hold time THD:WP 4000 — ns 1.8V ≤ VCC ≤ 2.5V

1300 — 2.5V ≤ VCC ≤ 5.5V

Output valid from clock TAA — 3500 ns 1.8V ≤ VCC ≤ 2.5V

(Note 2) — 900 2.5V ≤ VCC ≤ 5.5V

Bus free time: Time the bus must be TBUF 4700 — ns 1.8V ≤ VCC ≤ 2.5V

free before a new transmission can 1300 — 2.5V ≤ VCC ≤ 5.5V

start

Output fall time from VIH TOF 10 250 ns CB ≤ 100 pF (Note 1)

minimum to VIL maximum

Input filter spike suppression TSP — 50 ns (Notes 1 and 3)

(SDA and SCL pins)

Write cycle time (byte or page) TWC — 5 ms

Endurance 1M — cycles 25°C, VCC = 5.0V, Block Mode (Note 4)

Note 1: Not 100% tested. CB = total capacitance of one bus line in pF.

2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum

300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

3: The combined TSP and VHYS specifications are due to new Schmitt trigger inputs which provide improved noise spike

suppression. This eliminates the need for a TI specification for standard operation.

4: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please

consult the Total Endurance Model which can be obtained on Microchip’s BBS or website.

2000 Microchip Technology Inc. DS21189D-page 3

24AA64/24LC64

2.0 PIN DESCRIPTIONS 4.0 BUS CHARACTERISTICS

The following bus protocol has been defined:

2.1 A0, A1, A2 Chip Address Inputs

• Data transfer may be initiated only when the bus

The A0,A1,A2 inputs are used by the 24xx64 for multi- is not busy.

ple device operation. The levels on these inputs are • During data transfer, the data line must remain

compared with the corresponding bits in the slave stable whenever the clock line is HIGH. Changes

address. The chip is selected if the compare is true. in the data line while the clock line is HIGH will be

Up to eight devices may be connected to the same bus interpreted as a START or STOP condition.

by using different chip select bit combinations. These Accordingly, the following bus conditions have been

inputs must be connected to either VCC or VSS. defined (Figure 4-1).

2.2 SDA Serial Data 4.1 Bus not Busy (A)

This is a bi-directional pin used to transfer addresses Both data and clock lines remain HIGH.

and data into and data out of the device. It is an open-

drain terminal, therefore, the SDA bus requires a pullup 4.2 Start Data Transfer (B)

resistor to VCC (typical 10 kΩ for 100 kHz, 2 kΩ for

A HIGH to LOW transition of the SDA line while the

400 kHz)

clock (SCL) is HIGH determines a START condition. All

For normal data transfer SDA is allowed to change only commands must be preceded by a START condition.

during SCL low. Changes during SCL high are

reserved for indicating the START and STOP condi- 4.3 Stop Data Transfer (C)

tions.

A LOW to HIGH transition of the SDA line while the

2.3 SCL Serial Clock clock (SCL) is HIGH determines a STOP condition. All

operations must end with a STOP condition.

This input is used to synchronize the data transfer from

and to the device. 4.4 Data Valid (D)

2.4 WP The state of the data line represents valid data when,

after a START condition, the data line is stable for the

This pin can be connected to either Vss, Vcc or left duration of the HIGH period of the clock signal.

floating. An internal pull-down resistor on this pin will The data on the line must be changed during the LOW

keep the device in the unprotected state if left floating. period of the clock signal. There is one clock pulse per

If tied to Vss or left floating, normal memory operation bit of data.

is enabled (read/write the entire memory 0000-1FFF).

Each data transfer is initiated with a START condition

If tied to VCC, WRITE operations are inhibited. Read and terminated with a STOP condition. The number of

operations are not affected. the data bytes transferred between the START and

STOP conditions is determined by the master device.

3.0 FUNCTIONAL DESCRIPTION

4.5 Acknowledge

The 24xx64 supports a bi-directional 2-wire bus and

data transmission protocol. A device that sends data Each receiving device, when addressed, is obliged to

onto the bus is defined as a transmitter, and a device generate an acknowledge signal after the reception of

receiving data as a receiver. The bus must be con- each byte. The master device must generate an extra

trolled by a master device which generates the serial clock pulse which is associated with this acknowledge

clock (SCL), controls the bus access, and generates bit.

the START and STOP conditions while the 24xx64 Note: The 24xx64 does not generate any

works as a slave. Both master and slave can operate as acknowledge bits if an internal program-

a transmitter or receiver but the master device deter- ming cycle is in progress.

mines which mode is activated.

A device that acknowledges must pull down the SDA

line during the acknowledge clock pulse in such a way

that the SDA line is stable LOW during the HIGH period

of the acknowledge related clock pulse. Of course,

setup and hold times must be taken into account. Dur-

ing reads, a master must signal an end of data to the

slave by NOT generating an acknowledge bit on the last

byte that has been clocked out of the slave. In this case,

the slave (24xx64) will leave the data line HIGH to

enable the master to generate the STOP condition.

DS21189D-page 4 2000 Microchip Technology Inc.

24AA64/24LC64

FIGURE 4-1: DATA TRANSFER SEQUENCE ON THE SERIAL BUS

(A) (B) (D) (D) (C) (A)

SCL

SDA

START ADDRESS OR DATA STOP

CONDITION ACKNOWLEDGE ALLOWED CONDITION

VALID TO CHANGE

FIGURE 4-2: ACKNOWLEDGE TIMING

Acknowledge

Bit

SCL 1 2 3 4 5 6 7 8 9 1 2 3

SDA Data from transmitter Data from transmitter

Transmitter must release the SDA line at this point Receiver must release the SDA line at this point

allowing the Receiver to pull the SDA line low to so the Transmitter can continue sending data.

acknowledge the previous eight bits of data.

2000 Microchip Technology Inc. DS21189D-page 5

24AA64/24LC64

5.0 DEVICE ADDRESSING FIGURE 5-1: CONTROL BYTE FORMAT

A control byte is the first byte received following the Read/Write Bit

start condition from the master device (Figure 5-1). The

control byte consists of a four bit control code; for the Chip Select

24xx64 this is set as 1010 binary for read and write Control Code Bits

operations. The next three bits of the control byte are

the chip select bits (A2, A1, A0). The chip select bits S 1 0 1 0 A2 A1 A0 R/W ACK

allow the use of up to eight 24xx64 devices on the

same bus and are used to select which device is

Slave Address

accessed. The chip select bits in the control byte must

correspond to the logic levels on the corresponding A2, Start Bit Acknowledge Bit

A1, and A0 pins for the device to respond. These bits

are in effect the three most significant bits of the word

address.

The last bit of the control byte defines the operation to 5.1 Contiguous Addressing Across

be performed. When set to a one a read operation is Multiple Devices

selected, and when set to a zero a write operation is

selected. The next two bytes received define the The chip select bits A2, A1, A0 can be used to expand

address of the first data byte (Figure 5-2). Because the contiguous address space for up to 512K bits by

only A12...A0 are used, the upper three address bits adding up to eight 24xx64's on the same bus. In this

are don’t care bits. The upper address bits are trans- case, software can use A0 of the control byte as

ferred first, followed by the less significant bits. address bit A13, A1 as address bit A14, and A2 as

Following the start condition, the 24xx64 monitors the address bit A15. It is not possible to sequentially read

SDA bus checking the device type identifier being across device boundaries.

transmitted. Upon receiving a 1010 code and appropri-

ate device select bits, the slave device outputs an

acknowledge signal on the SDA line. Depending on the

state of the R/W bit, the 24xx64 will select a read or

write operation.

FIGURE 5-2: ADDRESS SEQUENCE BIT ASSIGNMENTS

CONTROL BYTE ADDRESS HIGH BYTE ADDRESS LOW BYTE

A A A A A A A A A A

1 0 1 0 2 1 0 R/W X X X 12 11 10 9 8 7 • • • • • • 0

CONTROL CHIP

CODE SELECT X = Don’t Care Bit

BITS

DS21189D-page 6 2000 Microchip Technology Inc.

24AA64/24LC64

6.0 WRITE OPERATIONS 6.2 Page Write

6.1 Byte Write The write control byte, word address and the first data

byte are transmitted to the 24xx64 in the same way as

Following the start condition from the master, the in a byte write. But instead of generating a stop condi-

control code (four bits), the chip select (three bits), and tion, the master transmits up to 31 additional bytes

the R/W bit (which is a logic low) are clocked onto the which are temporarily stored in the on-chip page buffer

bus by the master transmitter. This indicates to the and will be written into memory after the master has

addressed slave receiver that the address high byte will transmitted a stop condition. After receipt of each word,

follow after it has generated an acknowledge bit during the five lower address pointer bits are internally incre-

the ninth clock cycle. Therefore, the next byte transmit- mented by one. If the master should transmit more than

ted by the master is the high-order byte of the word 32 bytes prior to generating the stop condition, the

address and will be written into the address pointer of address counter will roll over and the previously

the 24xx64. The next byte is the least significant received data will be overwritten. As with the byte write

address byte. After receiving another acknowledge sig- operation, once the stop condition is received, an inter-

nal from the 24xx64 the master device will transmit the nal write cycle will begin (Figure 6-2). If an attempt is

data word to be written into the addressed memory made to write to the array with the WP pin held high, the

location. The 24xx64 acknowledges again and the device will acknowledge the command but no write

master generates a stop condition. This initiates the cycle will occur, no data will be written and the device

internal write cycle, and during this time the 24xx64 will will immediately accept a new command.

not generate acknowledge signals (Figure 6-1). If an

attempt is made to write to the array with the WP pin 6.3 Write Protection

held high, the device will acknowledge the command

The WP pin allows the user to write protect the entire

but no write cycle will occur, no data will be written and

array (0000-1FFF) when the pin is tied to Vcc. If tied to

the device will immediately accept a new command.

VSS or left floating, the write protection is disabled. The

After a byte write command, the internal address

WP pin is sampled at the STOP bit for every write com-

counter will point to the address location following the

mand (Figure 1-1) Toggling the WP pin after the STOP

one that was just written.

bit will have no effect on the execution of the write cycle.

FIGURE 6-1: BYTE WRITE

S

BUS ACTIVITY T S

MASTER A CONTROL ADDRESS ADDRESS T

R BYTE HIGH BYTE LOW BYTE DATA O

T P

SDA LINE S 1 0 1 0 A A A

2 1 0 0

X X X P

A A A A

BUS ACTIVITY C C C C

K K K K

X = don’t care bit

FIGURE 6-2: PAGE WRITE

S

T S

BUS ACTIVITY A CONTROL ADDRESS ADDRESS T

MASTER R BYTE HIGH BYTE LOW BYTE DATA BYTE 0 DATA BYTE 31 O

T P

SDA LINE A A A X X X P

S 1 0 1 0 2 1 0 0

A A A A A

BUS ACTIVITY C C C C C

K K K K K

X = don’t care bit

2000 Microchip Technology Inc. DS21189D-page 7

24AA64/24LC64

7.0 ACKNOWLEDGE POLLING FIGURE 7-1: ACKNOWLEDGE POLLING

FLOW

Since the device will not acknowledge during a write

cycle, this can be used to determine when the cycle is

complete (this feature can be used to maximize bus

throughput). Once the stop condition for a write com-

mand has been issued from the master, the device ini- Send

tiates the internally timed write cycle. ACK polling can Write Command

be initiated immediately. This involves the master send-

ing a start condition followed by the control byte for a

write command (R/W = 0). If the device is still busy with Send Stop

the write cycle, then no ACK will be returned. If no ACK Condition to

is returned, then the start bit and control byte must be Initiate Write Cycle

re-sent. If the cycle is complete, then the device will

return the ACK and the master can then proceed with

the next read or write command. See Figure 7-1 for Send Start

flow diagram.

Send Control Byte

with R/W = 0

Did Device NO

Acknowledge

(ACK = 0)?

YES

Next

Operation

DS21189D-page 8 2000 Microchip Technology Inc.

24AA64/24LC64

8.0 READ OPERATION 8.2 Random Read

Read operations are initiated in the same way as write Random read operations allow the master to access

operations with the exception that the R/W bit of the any memory location in a random manner. To perform

control byte is set to one. There are three basic types this type of read operation, first the word address must

of read operations: current address read, random read, be set. This is done by sending the word address to the

and sequential read. 24xx64 as part of a write operation (R/W bit set to 0).

After the word address is sent, the master generates a

8.1 Current Address Read start condition following the acknowledge. This termi-

The 24xx64 contains an address counter that main- nates the write operation, but not before the internal

tains the address of the last word accessed, internally address pointer is set. Then the master issues the

incremented by one. Therefore, if the previous read control byte again but with the R/W bit set to a one. The

access was to address n (n is any legal address), the 24xx64 will then issue an acknowledge and transmit

next current address read operation would access data the 8-bit data word. The master will not acknowledge

from address n + 1. the transfer but does generate a stop condition which

causes the 24xx64 to discontinue transmission

Upon receipt of the control byte with R/W bit set to one, (Figure 8-2). After a random read command, the inter-

the 24xx64 issues an acknowledge and transmits the nal address counter will point to the address location

eight bit data word. The master will not acknowledge following the one that was just read.

the transfer but does generate a stop condition and the

24xx64 discontinues transmission (Figure 8-1). 8.3 Sequential Read

FIGURE 8-1: CURRENT ADDRESS READ Sequential reads are initiated in the same way as a ran-

dom read except that after the 24xx64 transmits the

S

T S first data byte, the master issues an acknowledge as

BUS ACTIVITY A CONTROL DATA T

MASTER opposed to the stop condition used in a random read.

R BYTE BYTE O

T P This acknowledge directs the 24xx64 to transmit the

SDA LINE S 1 0 1 0 A AA 1 P

next sequentially addressed 8-bit word (Figure 8-3).

2 1 0 Following the final byte transmitted to the master, the

A N

BUS ACTIVITY C O

master will NOT generate an acknowledge but will gen-

K

A

erate a stop condition. To provide sequential reads the

C 24xx64 contains an internal address pointer which is

K incremented by one at the completion of each opera-

tion. This address pointer allows the entire memory

contents to be serially read during one operation. The

internal address pointer will automatically roll over from

address 1FFF to address 0000 if the master acknowl-

edges the byte received from the array address 1FFF.

FIGURE 8-2: RANDOM READ

S S

BUS ACTIVITY T T S

MASTER A CONTROL ADDRESS ADDRESS A CONTROL DATA T

R BYTE HIGH BYTE LOW BYTE R BYTE BYTE O

T T P

SDA LINE S1 0 1 0 AAA0 XXX S 1 0 1 0 A A A1 P

2 1 0 2 1 0

A A A A N

BUS ACTIVITY C C C C O

K K K K A

X = Don’t Care Bit C

K

FIGURE 8-3: SEQUENTIAL READ

S

BUS ACTIVITY CONTROL T

MASTER BYTE DATA n DATA n + 1 DATA n + 2 DATA n + X O

P

SDA LINE P

A A A A N

C C C C O

BUS ACTIVITY K K K K A

C

K

2000 Microchip Technology Inc. DS21189D-page 9

24AA64/24LC64

NOTES:

DS21189D-page 10 2000 Microchip Technology Inc.

24AA64/24LC64

24xx64 PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

24xx64 — /P

P = Plastic DIP (300 mil Body), 8-lead

SN = Plastic SOIC (150 mil Body, EIAJ standard), 8-lead

Package: SM = Plastic SOIC (208 mil Body, EIAJ standard), 8-lead

ST = TSSOP, 8-lead

Temperature Blank = 0°C to +70°C

Range: I = -40°C to +85°C

E = -40°C to +125°C

24AA64 64K bit 1.8V I2C Serial EEPROM

24AA64T 64K bit 1.8V I2C Serial EEPROM (Tape and Reel)

24AA64X 64K bit 1.8V I2C Serial EEPROM

in alternate pinout (ST only)

24AA64XT 64K bit 1.8V I2C Serial EEPROM

in alternate pinout (ST only)

Device: 24LC64 64K bit 2.5V I2C Serial EEPROM

24LC64T 64K bit 2.5V I2C Serial EEPROM (Tape and Reel)

24LC64X 64K bit 2.5V I2C Serial EEPROM

in alternate pinout (ST only)

24LC64XT 64K bit 2.5V I2C Serial EEPROM

in alternate pinout (ST only)

Sales and Support

Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-

mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Corporate Literature Center U.S. FAX: (480) 786-7277

3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

2000 Microchip Technology Inc. DS21189D-page 11

WORLDWIDE SALES AND SERVICE

AMERICAS AMERICAS (continued) ASIA/PACIFIC (continued)

Corporate Office Toronto Singapore

Microchip Technology Inc. Microchip Technology Inc. Microchip Technology Singapore Pte Ltd.

2355 West Chandler Blvd. 5925 Airport Road, Suite 200 200 Middle Road

Chandler, AZ 85224-6199 Mississauga, Ontario L4V 1W1, Canada #07-02 Prime Centre

Tel: 480-786-7200 Fax: 480-786-7277 Tel: 905-405-6279 Fax: 905-405-6253 Singapore 188980

Technical Support: 480-786-7627 ASIA/PACIFIC Tel: 65-334-8870 Fax: 65-334-8850

Web Address: http://www.microchip.com Taiwan, R.O.C

Beijing Microchip Technology Taiwan

Atlanta Microchip Technology, Beijing 10F-1C 207

Microchip Technology Inc. Unit 915, 6 Chaoyangmen Bei Dajie Tung Hua North Road

500 Sugar Mill Road, Suite 200B Dong Erhuan Road, Dongcheng District Taipei, Taiwan, ROC

Atlanta, GA 30350 New China Hong Kong Manhattan Building Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

Tel: 770-640-0034 Fax: 770-640-0307 Beijing 100027 PRC

Boston Tel: 86-10-85282100 Fax: 86-10-85282104 EUROPE

Microchip Technology Inc. Hong Kong Denmark

5 Mount Royal Avenue Microchip Asia Pacific Microchip Technology Denmark ApS

Marlborough, MA 01752 Unit 2101, Tower 2 Regus Business Centre

Tel: 508-480-9990 Fax: 508-480-8575 Metroplaza Lautrup hoj 1-3

Chicago 223 Hing Fong Road Ballerup DK-2750 Denmark

Microchip Technology Inc. Kwai Fong, N.T., Hong Kong Tel: 45 4420 9895 Fax: 45 4420 9910

333 Pierce Road, Suite 180 Tel: 852-2-401-1200 Fax: 852-2-401-3431 France

Itasca, IL 60143 India Arizona Microchip Technology SARL

Tel: 630-285-0071 Fax: 630-285-0075 Microchip Technology Inc. Parc d’Activite du Moulin de Massy

Dallas India Liaison Office 43 Rue du Saule Trapu

Microchip Technology Inc. No. 6, Legacy, Convent Road Batiment A - ler Etage

4570 Westgrove Drive, Suite 160 Bangalore 560 025, India 91300 Massy, France

Addison, TX 75248 Tel: 91-80-229-0061 Fax: 91-80-229-0062 Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Tel: 972-818-7423 Fax: 972-818-2924 Japan Germany

Dayton Microchip Technology Intl. Inc. Arizona Microchip Technology GmbH

Microchip Technology Inc. Benex S-1 6F Gustav-Heinemann-Ring 125

Two Prestige Place, Suite 150 3-18-20, Shinyokohama D-81739 München, Germany

Miamisburg, OH 45342 Kohoku-Ku, Yokohama-shi Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

Tel: 937-291-1654 Fax: 937-291-9175 Kanagawa 222-0033 Japan Italy

Detroit Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Arizona Microchip Technology SRL

Microchip Technology Inc. Korea Centro Direzionale Colleoni

Tri-Atria Office Building Microchip Technology Korea Palazzo Taurus 1 V. Le Colleoni 1

32255 Northwestern Highway, Suite 190 168-1, Youngbo Bldg. 3 Floor 20041 Agrate Brianza

Farmington Hills, MI 48334 Samsung-Dong, Kangnam-Ku Milan, Italy

Tel: 248-538-2250 Fax: 248-538-2260 Seoul, Korea Tel: 39-039-65791-1 Fax: 39-039-6899883

Los Angeles Tel: 82-2-554-7200 Fax: 82-2-558-5934 United Kingdom

Microchip Technology Inc. Shanghai Arizona Microchip Technology Ltd.

18201 Von Karman, Suite 1090 Microchip Technology 505 Eskdale Road

Irvine, CA 92612 Unit B701, Far East International Plaza, Winnersh Triangle

Tel: 949-263-1888 Fax: 949-263-1338 No. 317, Xianxia Road Wokingham

New York Shanghai, 200051 P.R.C Berkshire, England RG41 5TU

Microchip Technology Inc. Tel: 86-21-6275-5700 Fax: 86-21-6275-5060 Tel: 44 118 921 5858 Fax: 44-118 921-5835

150 Motor Parkway, Suite 202

01/05/00

Hauppauge, NY 11788

Tel: 631-273-5305 Fax: 631-273-5335

San Jose Microchip received QS-9000 quality system

Microchip Technology Inc. certification for its worldwide headquarters,

2107 North First Street, Suite 590 design and wafer fabrication facilities in

San Jose, CA 95131 Chandler and Tempe, Arizona in July 1999. The

Tel: 408-436-7950 Fax: 408-436-7955 Company’s quality system processes and

procedures are QS-9000 compliant for its

PICmicro® 8-bit MCUs, KEELOQ® code hopping

devices, Serial EEPROMs and microperipheral

products. In addition, Microchip’s quality

system for the design and manufacture of

development systems is ISO 9001 certified.

All rights reserved. © 2000 Microchip Technology Incorporated. Printed in the USA. 1/00 Printed on recycled paper.

Information contained in this publication regarding device applications and the like is intended for suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed

by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip’s products

as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip

logo and name are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.

DS21189D-page 12 2000 Microchip Technology Inc.

You might also like

- CBIP Substation Manual 2006 PDFDocument122 pagesCBIP Substation Manual 2006 PDFPravin Narkhede83% (18)

- Incon 1250Document35 pagesIncon 1250Hugo MoralesNo ratings yet

- 24 LC 2561Document12 pages24 LC 2561ricardo_MassisNo ratings yet

- 24C02C SMDDocument16 pages24C02C SMDWalter RossiNo ratings yet

- 24C32Document12 pages24C32Joao EfremNo ratings yet

- 32K 5.0V I C Smart Serial Eeprom: Obsolete DeviceDocument15 pages32K 5.0V I C Smart Serial Eeprom: Obsolete DeviceDar KeyyNo ratings yet

- 24LC024Document22 pages24LC024David ChaoNo ratings yet

- 24lc08 EepromDocument27 pages24lc08 EepromIsmael Minchola CarhuasNo ratings yet

- Eeprom 24w04Document15 pagesEeprom 24w04davixformusicNo ratings yet

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsDocument12 pages24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsBoris PopovNo ratings yet

- EEprom 24 C65Document25 pagesEEprom 24 C65ESKALENONo ratings yet

- 24LC02BDocument26 pages24LC02Bjab_arx1No ratings yet

- 64K 5.0V I C Smart Serial Eeprom: FeaturesDocument16 pages64K 5.0V I C Smart Serial Eeprom: FeaturesFerner BriceñoNo ratings yet

- 4K 5.0V I C Serial EEPROM: Obsolete DeviceDocument14 pages4K 5.0V I C Serial EEPROM: Obsolete Devicefrank_grimesNo ratings yet

- 24LC04BDocument22 pages24LC04BcarlosNo ratings yet

- 24 LC 16Document12 pages24 LC 16Sebastian QuaroneNo ratings yet

- 24 LC 02Document13 pages24 LC 02MoshikoRanNo ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument23 pages2-Wire Serial EEPROM: FeaturesgillupilluNo ratings yet

- 24AA00/24LC00/24C00: 128 Bit I C Bus Serial EEPROMDocument18 pages24AA00/24LC00/24C00: 128 Bit I C Bus Serial EEPROMJuliano GriguloNo ratings yet

- 24C64WPDocument15 pages24C64WPaldo_suviNo ratings yet

- 24LC16BDocument40 pages24LC16BelqrqNo ratings yet

- 1K 2.5V Dual Mode I C Serial EEPROMDocument26 pages1K 2.5V Dual Mode I C Serial EEPROMbalck_virusNo ratings yet

- 24 C 32Document19 pages24 C 32teroplasNo ratings yet

- Two-Wire Serial EEPROM: FeaturesDocument28 pagesTwo-Wire Serial EEPROM: FeaturesdobsrdjanNo ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument21 pages2-Wire Serial Eeprom: FeaturesRenato Peñaloza CallaNo ratings yet

- Datasheet EEPROMDocument9 pagesDatasheet EEPROMIram Loya ValladaresNo ratings yet

- 24 LC 16Document32 pages24 LC 16josjcrsNo ratings yet

- Eeproms 24CXXDocument18 pagesEeproms 24CXXAlberto YepezNo ratings yet

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsDocument13 pages24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsJose Antonio Lopez JuradoNo ratings yet

- Atmel 24C02Document24 pagesAtmel 24C02chichedemorenoNo ratings yet

- 3Document10 pages3jovel lanat100% (1)

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument22 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ASergioNo ratings yet

- Cmos 24aa256 & 24LC256Document12 pagesCmos 24aa256 & 24LC256Someguy123551234512No ratings yet

- Two-Wire Automotive Temperature Serial EEPROM: FeaturesDocument20 pagesTwo-Wire Automotive Temperature Serial EEPROM: Features강종운No ratings yet

- 24C512Document13 pages24C512kimbo23No ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument26 pages2-Wire Serial EEPROM: FeaturesLinkyNo ratings yet

- Atmel 24C1024Document19 pagesAtmel 24C1024vax1No ratings yet

- ST24 25C04, ST24 25W04Document16 pagesST24 25C04, ST24 25W04Zoran KovacevicNo ratings yet

- DS1307 Datasheet FullDocument15 pagesDS1307 Datasheet FulllamanzanadeadanNo ratings yet

- MCP 79410Document34 pagesMCP 79410Krishna SinghNo ratings yet

- I C, 32-Bit, Binary Counter Clock With 64-Bit ID: General Description FeaturesDocument12 pagesI C, 32-Bit, Binary Counter Clock With 64-Bit ID: General Description FeaturesNur AzizahNo ratings yet

- 64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesDocument13 pages64K (8Kx8) Parallel Eeproms AT28C64 AT28C64X: FeaturesJi HooNo ratings yet

- Atmel 24C02Document26 pagesAtmel 24C02kukinjosNo ratings yet

- 16K 1.8V I C Serial EEPROM: FeaturesDocument12 pages16K 1.8V I C Serial EEPROM: FeaturesKrzysztof BondkaNo ratings yet

- Hanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDocument9 pagesHanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDeepa DevarajNo ratings yet

- 24 LC 16 BDocument12 pages24 LC 16 BAnonymous UxrPsIVNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesAn TrìnhNo ratings yet

- Memoria CAT24M01-D-91485Document15 pagesMemoria CAT24M01-D-91485Feer Rusk EdgarNo ratings yet

- M48T02 150pciDocument15 pagesM48T02 150pciImran YaminNo ratings yet

- Atmel 8568 SEEPROM AT24C256C Datasheet PDFDocument21 pagesAtmel 8568 SEEPROM AT24C256C Datasheet PDFhanifNo ratings yet

- Atmel AT250x0 MemoryDocument19 pagesAtmel AT250x0 MemoryNamburi NandanNo ratings yet

- CAT24C256 256 KB I C CMOS Serial Eeprom: DescriptionDocument18 pagesCAT24C256 256 KB I C CMOS Serial Eeprom: Descriptionjagadees21No ratings yet

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument4 pages24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMcabalaestebanNo ratings yet

- EEPROM 24LC512 - 21754eDocument26 pagesEEPROM 24LC512 - 21754eMarcelo Azevedo BragaNo ratings yet

- 25AA640/25LC640: 64K SPI Bus Serial EEPROMDocument24 pages25AA640/25LC640: 64K SPI Bus Serial EEPROMnguyenluongdpNo ratings yet

- DS1307 Real Time ClockDocument14 pagesDS1307 Real Time Clockpraveen_kodgirwarNo ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 55n06 MosfetDocument7 pages55n06 MosfetachuthkumarNo ratings yet

- Complete RH Plug-In Relays Catalogue - FileADocument21 pagesComplete RH Plug-In Relays Catalogue - FileAachuthkumarNo ratings yet

- Final Kenstar Mwo - Manual KT20GBB3 PDFDocument31 pagesFinal Kenstar Mwo - Manual KT20GBB3 PDFachuthkumarNo ratings yet

- LT Switchhs VGMV Au-H4St - HTLF/-L& Typffi - !# ,#Fi$Ffit$ ' Pt#At TffifflDocument4 pagesLT Switchhs VGMV Au-H4St - HTLF/-L& Typffi - !# ,#Fi$Ffit$ ' Pt#At TffifflachuthkumarNo ratings yet

- Electric Detonators Used in Wireline OperationsDocument8 pagesElectric Detonators Used in Wireline OperationsachuthkumarNo ratings yet

- En733 PDFDocument2 pagesEn733 PDFachuthkumarNo ratings yet

- Relay 736: Technical DataDocument3 pagesRelay 736: Technical DataachuthkumarNo ratings yet

- New Fluke 287: True-Rms Electronics Logging Multimeter With TrendcaptureDocument2 pagesNew Fluke 287: True-Rms Electronics Logging Multimeter With TrendcaptureachuthkumarNo ratings yet

- FQP6N60Document8 pagesFQP6N60achuthkumarNo ratings yet

- Latching Relay DatasheetDocument30 pagesLatching Relay Datasheetachuthkumar100% (1)

- PWM Using ArduinoDocument6 pagesPWM Using ArduinoJulian David RodriguezNo ratings yet

- QRB List of Graphs 1 by Ashish KapoorDocument1 pageQRB List of Graphs 1 by Ashish KapoorAshmit DeshwalNo ratings yet

- Computer NetworkDocument22 pagesComputer NetworkAHMED SOHELNo ratings yet

- BURNDY KA26U SpecsheetDocument2 pagesBURNDY KA26U SpecsheetcarlamanelsaNo ratings yet

- Service Guide N9912A: Agilent Technologies RF Analyzer (2 MHZ - 4 GHZ) (2 MHZ - 6 GHZ)Document132 pagesService Guide N9912A: Agilent Technologies RF Analyzer (2 MHZ - 4 GHZ) (2 MHZ - 6 GHZ)Truong Anh DungNo ratings yet

- Power Tools Inspection ChecklistDocument4 pagesPower Tools Inspection ChecklistRuzaini Mohamed100% (1)

- 2) Sentron 3WT ACBDocument16 pages2) Sentron 3WT ACBchandel100100% (1)

- Amba Bus ProtocolDocument3 pagesAmba Bus Protocolkoti459No ratings yet

- Busway Handling-MaintenanceDocument25 pagesBusway Handling-MaintenanceThức VõNo ratings yet

- Electric Current and Its 14 EffectsDocument5 pagesElectric Current and Its 14 Effectsraja_tanukuNo ratings yet

- Manual de Instrucciones Karceher HD 5 12 C - BTA-5309339-000-01Document40 pagesManual de Instrucciones Karceher HD 5 12 C - BTA-5309339-000-01Christian TrujilloNo ratings yet

- Akai AX-60 Service ManualDocument45 pagesAkai AX-60 Service ManualGiannino BertoliNo ratings yet

- Holux GPS Receiver GR-230 MANUAL000074468Document17 pagesHolux GPS Receiver GR-230 MANUAL000074468a.tadysiakNo ratings yet

- Power QualityDocument43 pagesPower Qualityazzam_aliNo ratings yet

- FSB800 - DDR400 (PC3200)Document96 pagesFSB800 - DDR400 (PC3200)nivaldo de oliveira Oliveira100% (1)

- Sistema Electrico 994F PDFDocument4 pagesSistema Electrico 994F PDFLuis Chatilan AguilarNo ratings yet

- Mini Project Report Industrial Automation SreekuDocument38 pagesMini Project Report Industrial Automation Sreekusreekumar456No ratings yet

- Secflow-2: Ruggedized Scada-Aware Ethernet Switch/RouterDocument434 pagesSecflow-2: Ruggedized Scada-Aware Ethernet Switch/RouterMihai DarstaruNo ratings yet

- GEI-100519 Direct Modbus For Mark VI and EX2100 PDFDocument4 pagesGEI-100519 Direct Modbus For Mark VI and EX2100 PDFmeirangong100% (1)

- Model MBW15 MBW22Document3 pagesModel MBW15 MBW22Liem Nguyen HuuNo ratings yet

- Quantitative Evaluation For Reliability of Hybrid Electric Vehicle PowertrainDocument6 pagesQuantitative Evaluation For Reliability of Hybrid Electric Vehicle PowertrainVenkadakrishnan ThiagarajanNo ratings yet

- Denso BHT-300 - Leaflet English PDFDocument6 pagesDenso BHT-300 - Leaflet English PDFvelNo ratings yet

- Skymasts Tetra Antenna Product Catalogue 2013Document57 pagesSkymasts Tetra Antenna Product Catalogue 2013Fabio CostaNo ratings yet

- Micromachines 11 00666 v2Document25 pagesMicromachines 11 00666 v2Paola GongoraNo ratings yet

- Solar Simulation Standards and QuickSun Measurement SystemDocument34 pagesSolar Simulation Standards and QuickSun Measurement SystemMohamad YazdaniNo ratings yet

- SopDocument7 pagesSopNiranjan ReddyNo ratings yet

- Chapter 33 ETAP User Guide 7 5 2 PDFDocument32 pagesChapter 33 ETAP User Guide 7 5 2 PDFArturo RamirezNo ratings yet

- Earth Station TechnologyDocument18 pagesEarth Station TechnologyBorn MaDNo ratings yet