Professional Documents

Culture Documents

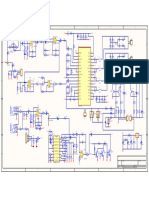

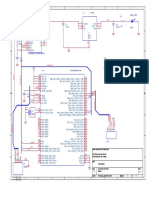

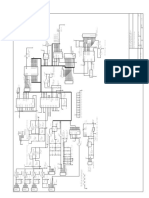

Iprog Mainboard SCH

Uploaded by

nelson linceOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Iprog Mainboard SCH

Uploaded by

nelson linceCopyright:

Available Formats

5 4 3 2 1

U9 IRU1117-33

3 2 VCC_CPU

VIN VOUT C1 100n

U2 ESD200

1 8 BT_TXD

C6 GND RXD BT_RXD U5A 74HC244

+

VCC_CPU 2 7

C3 C4 47uF VCC TXD

+ 3 6 2 18

10 uF 100n BT_RESET STATUS RTS A0 Y0

4 5 4 16

RESET CTS A1 Y1

6 14

C5 A2 Y2 IRQ

8 12

100n A3 Y3

1

OE

VCC R78

D D

R62 10K

VCC_CPU

R1 R7 R8 R3

4.7K 10K 10K 10K R79

R12 R11 R2 R13 R77

4.7K 4.7K 4.7K 4.7K

J2B

GND1 1 U10 AT91SAM7S R80 R 16

U1A 74HC244 17

RST1 1 40 48 PWM0 2 18 IO_RXD 18

TST PA0/PGMEN0 PWM1 A0 Y0 IO_TXD

39 47 4 16 19

D18 1N5819 TCK1 NRST PA1/PGMEN1 PWM2 A1 Y1 IO_RTS

1 55 44 6 14 20

ERASE PA2/PGMEN2 EXT_VCC_DETECT A2 Y2

43 8 12 21

R10 TDI1 PA3 BT_RESET A3 Y3

1 50 36 22

JTAGSEL PA4/PGMNCMD RXD R87

53 35 1 23

1.5K TDO1 TCK PA5/PGMRDY TXD OE

1 33 34 24

TDI PA6/PGMNOE RTS

49 32 25

TMS1 TDO PA7/PGMNVALID CTS

1 51 31 26

USB A1 R14 27 TMS PA8/PGMM0 BT_RXD

30 27

DDM PA9/PGMM1 BT_TXD R88

56 29 28

DDM PA10/PGMM2 SPI_CS

1 57 28 29

C8 DDP PA11/PGMM3 MISO U1B 74HC244

2 27

27p PA12/PGMD0 MOSI

3 22 11 9

R18 27 PA13/PGMD1 SPCK A0 Y0 CONN DSUBHD 44-R

4 62 21 13 7

XIN/PGMCK PA14/PGMD2 IO_IN_EN A1 Y1

20 15 5

PA15/PGMD3 IO0 A2 Y2 R89

19 17 3

PA16/PGMD4 IO1 A3 Y3

61 9

XOUT PA17/PGMD5/AD0 IO2 +12V

10 19

C9 C10 Y1 PA18/PGMD6/AD1 IO3 OE VCC

63 13

15p 15p PLLRC PA19/PGMD7/AD2 IO4

16

PA20/PGMD8/AD3 IO5

VCC_CPU 7 11

C14 R20 VDDIN PA21/PGMD9 IO6

59 14

1000 1.5K VDDFLASH PA22/PGMD10 IO7

15

CRYSTAL PA23/PGMD11 IO_OUT_LATCH R22 R23 R24 R25 R26 R27 R28

R21 R5

18 23 VCC

VDDIO PA24/PGMD12 RDY 10K

45 25

C15 C16 C17 VDDIO PA25/PGMD13 EN_12V U5B

C 58 26 C

22p 22p 10n VDDIO PA26/PGMD14 IO_3_5V

37

VCC_CORE PA27/PGMD15 10_12V RDY

8 38 11 9

VDDOUT PA28 IO_VCC_ON A0 Y0

12 41 13 7

VDDCORE PA29 IRQ A1 Y1

24 42 15 5

VDDCORE PA30 OUT_5V_EN A2 Y2

54 52 17 3

VDDCORE PA31 U4A 74HC244 A3 Y3

64

R29 10 VDDPLL IO0

3 18 2 19

AD4 IO1 Y0 A0 OE

VCC_CPU 1 4 16 4

ADVREF AD5 IO2 Y1 A1

5 14 6

AD6 IO3 Y2 A2 74HC244

2 6 12 8

C18 GND AD7 Y3 A3

17

100n GND

46 1

EXT_VCC GND OE

60

J1 J4 GND IO4 9 11

IO5 Y0 A0

7 13

J3 PHONEJACK IO6 Y1 A1

1 1 VCC_CPU 5 15

10_12V IO7 Y2 A2

3 2 2 3 17

Y3 A3

2 3 3 VCC

1 IO_VCC_ON 4 4 19

EN_12V +12V IO0 OE

5 5 OUT_5V R66 R

IO_3_5V OUT_5V_EN VCC

6 6

R67 R IO1

U6 J2A

VCC_CORE IO2 IO0

R68 R 3 2 D2 R81 1

C20 IO1 D0 Q0 D3 R82

4 5 2

C19 100n R69 R IO3 IO2 D1 Q1 D4 R83

7 6 3

100n IO3 D2 Q2 D5 R84

8 9 4

R70 R IO4 IO4 D3 Q3 D7 R85

13 12 5

IO5 D4 Q4 D8 R86

14 15 6

R71 R IO5 IO6 D5 Q5 D9 R32 33

17 16 7

IO7 D6 Q6 D10 R34 33

18 19 8

R72 R IO6 D7 Q7 R35 33

VCC_CPU 9

11 R37 33 10

R73 R IO7 LE R38 33

VCC_CPU 1 11

OE R39 33 12

R41 R40 33 13

10K C11 C7 C13 C21 74LS373 R42 33 OUT_5V 14

B B

100n 100n 100n 100n 15

EXT_VCC_DETECT

CONN DSUBHD 44-R

R9 10K

VCC +12V

R33 1K Q2

EXT_VCC 2N7002 C34 C2 C26 C30

100n 100n 100n 100n

R36

10K

VCC

J2C

+12V 30

31

R19 51K 32

33

EXT_VCC 34

R49 51K 35

36

37

R57 51K 38

39

40

R54 51K 41

42

43

44

R4 R15 R16 R17

10K 10K 10K 10K CONN DSUBHD 44-R

A A

Title

iProg programmer

Size Document Number Rev

C <Doc> 1.0

Date: Tuesday, February 02, 2010 Sheet 1 of 1

5 4 3 2 1

You might also like

- Peugeot 207 1.4. 16v PDFDocument13 pagesPeugeot 207 1.4. 16v PDFAgustin Berrios Mendoza100% (1)

- K20a6 Ecu Pinout Accord Rsx Dc5Document2 pagesK20a6 Ecu Pinout Accord Rsx Dc5Uros GalovicNo ratings yet

- ABS and Traction Control DiagnosisDocument38 pagesABS and Traction Control DiagnosisThibault ChapelNo ratings yet

- RE4R03ADocument2 pagesRE4R03AAbbode HoraniNo ratings yet

- S13 SR20 Guide 08Document20 pagesS13 SR20 Guide 08Алексей Иванченко100% (1)

- ABS Mod - LAND ROVER CLUB V.IDocument79 pagesABS Mod - LAND ROVER CLUB V.Itim yerbyNo ratings yet

- Project 15 MOTOR BASICSDocument7 pagesProject 15 MOTOR BASICSDarwin VargasNo ratings yet

- MH8206F Mitsu TR4 - 2.016Document1 pageMH8206F Mitsu TR4 - 2.016nelson linceNo ratings yet

- Iprog Powerboard SCHDocument1 pageIprog Powerboard SCHdrsNo ratings yet

- Diagrama ElectricoDocument14 pagesDiagrama ElectricoJose PichinteNo ratings yet

- Toyota Alphard fuse and relay box diagramsDocument1 pageToyota Alphard fuse and relay box diagramsSiu Kit YauNo ratings yet

- Engine Control System 1. General: 37 Engine-4A-Fe and 7A-Fe EnginesDocument10 pagesEngine Control System 1. General: 37 Engine-4A-Fe and 7A-Fe EnginesDavid R PaucaraNo ratings yet

- Alh Wiring HarnessDocument18 pagesAlh Wiring HarnessAlex DavidNo ratings yet

- Re4F04A and Re4F04V Automatic Transmission (A/T) - Solenoid Valve Replacement ProceduresDocument3 pagesRe4F04A and Re4F04V Automatic Transmission (A/T) - Solenoid Valve Replacement ProceduresfulltransmissionNo ratings yet

- Tvip PDFDocument6 pagesTvip PDFamart79196No ratings yet

- FCCCGGGGDocument4 pagesFCCCGGGGYorvic GodoyNo ratings yet

- MIL ON DTC P2820 2014 - 2017 Corolla Transmission(s) CVT 2017 Im Transmission(s) CVTDocument10 pagesMIL ON DTC P2820 2014 - 2017 Corolla Transmission(s) CVT 2017 Im Transmission(s) CVTSajjad HussainNo ratings yet

- SPFRDDocument2 pagesSPFRDSebastianus Ari YudhantoNo ratings yet

- 2008 Chevrolet HHR DTCDocument6 pages2008 Chevrolet HHR DTCTal Benyamin100% (1)

- Bando TototaDocument55 pagesBando TototagaelNo ratings yet

- ImmobilizerDocument6 pagesImmobilizerBenz Aio Calachua Araujo100% (2)

- Can Communication: Can Communication System: Terminals ofDocument11 pagesCan Communication: Can Communication System: Terminals ofKiddNo ratings yet

- Computer Data Lines CircuitDocument4 pagesComputer Data Lines CircuitAliNo ratings yet

- Engine Control For 2TR-FE: 90 Toyota Tacoma (Em01D0U)Document12 pagesEngine Control For 2TR-FE: 90 Toyota Tacoma (Em01D0U)DanielNo ratings yet

- ZF4HP22 transmission diagramDocument10 pagesZF4HP22 transmission diagramAussi SidNo ratings yet

- 2uztrd PDFDocument33 pages2uztrd PDFbob loblawNo ratings yet

- Alphard Chassis Ind PDFDocument70 pagesAlphard Chassis Ind PDFDikyNo ratings yet

- Link Mod Ets2Document63 pagesLink Mod Ets2Eka Febria Lusanto100% (1)

- Adaptronic Blacktop Installation NotesDocument6 pagesAdaptronic Blacktop Installation NotesRayz GsrNo ratings yet

- Engine Compartment Fuse Box (Type 2) : 1 - 2 Head (RH) 10 Right Hand Headlight 3 Head (LH) 10 Left Hand HeadlightDocument7 pagesEngine Compartment Fuse Box (Type 2) : 1 - 2 Head (RH) 10 Right Hand Headlight 3 Head (LH) 10 Left Hand HeadlightCarlos Alberto LopezNo ratings yet

- 32d05 Control of ECTDocument12 pages32d05 Control of ECTMelvin MhdsNo ratings yet

- SSP 040 Automatic Gearbox 001 FabiaDocument46 pagesSSP 040 Automatic Gearbox 001 FabiaKovács EndreNo ratings yet

- Computer Control SystemDocument67 pagesComputer Control SystemToua YajNo ratings yet

- cx5 MitsubichiDocument554 pagescx5 MitsubichiJULIAN VALDERRAMA50% (2)

- 10-6620 For EMS - 30-6620Document14 pages10-6620 For EMS - 30-6620Michael AliNo ratings yet

- PAL MaintenanceDocument4 pagesPAL MaintenanceLucas PrimaniNo ratings yet

- 006 - 1.6 L Engine Marelli 1AV 55 KW, Engine Code Letters ALMDocument9 pages006 - 1.6 L Engine Marelli 1AV 55 KW, Engine Code Letters ALMAndres ChoqueNo ratings yet

- Fuse, Relay and Wiring Diagram Manual for Lifan 720Document130 pagesFuse, Relay and Wiring Diagram Manual for Lifan 720lartsim115No ratings yet

- Fuse Box Diagram Ford EcoSport (2013-2017)Document8 pagesFuse Box Diagram Ford EcoSport (2013-2017)chennaimaterialsupplyNo ratings yet

- Toyota Allion / Premio 240 (2001-2007) : System Capacity (L) Type Lubrication (W Filter)Document1 pageToyota Allion / Premio 240 (2001-2007) : System Capacity (L) Type Lubrication (W Filter)Walakulu Arachchige Lasantha IndralalNo ratings yet

- AVEO 2007-2010/wave - 07-10/engine Mechanical - 1.5L/Repair Instructions - Off VehicleDocument39 pagesAVEO 2007-2010/wave - 07-10/engine Mechanical - 1.5L/Repair Instructions - Off VehicleArley Hernandez100% (1)

- BeltsDocument89 pagesBeltszul100% (2)

- Installation Instructions For 30-1910: Fuel Ignition Controller (F/IC)Document24 pagesInstallation Instructions For 30-1910: Fuel Ignition Controller (F/IC)Dmentall IllNo ratings yet

- OpelDocument8 pagesOpelCristi NaNo ratings yet

- 0 Park 0 ShuntDocument4 pages0 Park 0 ShuntGligorijević DarkoNo ratings yet

- File 2Document6 pagesFile 2ipejasinovic6804No ratings yet

- Volvo 850 ODB A1 Automatic Transmission DiagnosticDocument9 pagesVolvo 850 ODB A1 Automatic Transmission DiagnosticBartłomiej KilianNo ratings yet

- Touareg No. 72 / 1: 3.0 l/165 KW TDI, Engine Code BKS 3.0 l/155 KW TDI, Engine Code BUNDocument17 pagesTouareg No. 72 / 1: 3.0 l/165 KW TDI, Engine Code BKS 3.0 l/155 KW TDI, Engine Code BUNG GNo ratings yet

- TCM JourneyDocument1 pageTCM JourneyUju OikNo ratings yet

- Mystique-1 Shark Bay Block Diagram: Project Code: 91.4LY01.001 PCB (Raw Card) : 12298-2Document80 pagesMystique-1 Shark Bay Block Diagram: Project Code: 91.4LY01.001 PCB (Raw Card) : 12298-2Ion PetruscaNo ratings yet

- Climatronic Current Flow DiagramDocument11 pagesClimatronic Current Flow DiagramNapo Bere100% (1)

- Obd-Ii: RS-232 Serial CableDocument5 pagesObd-Ii: RS-232 Serial CableAmir EmraniNo ratings yet

- 2009 Nissan Maxima SV 3.5L, V6, USADocument1 page2009 Nissan Maxima SV 3.5L, V6, USAMisa GamezNo ratings yet

- sb0341t09 PDFDocument7 pagessb0341t09 PDFZool Car زول كارNo ratings yet

- Engine Control SystemDocument7 pagesEngine Control SystemFaisal Al HusainanNo ratings yet

- Ms3pro ManualDocument274 pagesMs3pro ManualTiago FrisonNo ratings yet

- Engine Temperature Control Actuator - N493-, CHECKING: General DescriptionDocument3 pagesEngine Temperature Control Actuator - N493-, CHECKING: General Descriptionbyungchul kimNo ratings yet

- OCM500 SCHDocument1 pageOCM500 SCHNosdan LemosNo ratings yet

- CaptureTutorial SchematicSmartPDFDocument1 pageCaptureTutorial SchematicSmartPDFAaron HernandezNo ratings yet

- Maximizing signal reception with an adjustable LNA circuitDocument1 pageMaximizing signal reception with an adjustable LNA circuitALFONZO DANIELNo ratings yet

- weatherSTAMP - UnknownDocument1 pageweatherSTAMP - UnknownJony DarkoNo ratings yet

- 2.-Guia de Tranponders Clonables Y EquivalentesDocument2 pages2.-Guia de Tranponders Clonables Y EquivalentesPablo Nuñez100% (1)

- Instruction lance20NA - PDFDocument1 pageInstruction lance20NA - PDFnelson linceNo ratings yet

- 08-CHERY - Tips Inmobilizador.Document24 pages08-CHERY - Tips Inmobilizador.Santiago Henao VillegasNo ratings yet

- Manual Zed Bull PDFDocument30 pagesManual Zed Bull PDFnelson linceNo ratings yet

- Suzuki GSX 1400 0508 PDFDocument1 pageSuzuki GSX 1400 0508 PDFnelson linceNo ratings yet

- Nissan Navarra 25dci 174cv PDFDocument4 pagesNissan Navarra 25dci 174cv PDFnelson linceNo ratings yet

- Instruction Outlander - Turbo - PDFDocument1 pageInstruction Outlander - Turbo - PDFnelson linceNo ratings yet

- Kawasaki - Jetski Ultra-08-09Document1 pageKawasaki - Jetski Ultra-08-09nelson linceNo ratings yet

- Document overviewDocument1 pageDocument overviewnelson linceNo ratings yet

- Suzuki GSX-R1000 07 09 READ WRITE PLUG PDFDocument1 pageSuzuki GSX-R1000 07 09 READ WRITE PLUG PDFnelson linceNo ratings yet

- Instruction Lancer - Evo9 - PDFDocument1 pageInstruction Lancer - Evo9 - PDFnelson linceNo ratings yet

- Jaguar 1Document4 pagesJaguar 1nelson linceNo ratings yet

- Delphi DCM 1.2 ECU Pinout & Bootstrap Pin GuideDocument2 pagesDelphi DCM 1.2 ECU Pinout & Bootstrap Pin GuideAlexandre Da Silva PintoNo ratings yet

- Instruction Mitsubishi Grandis - PDFDocument1 pageInstruction Mitsubishi Grandis - PDFnelson linceNo ratings yet

- Instruction lance20NA - PDFDocument1 pageInstruction lance20NA - PDFnelson linceNo ratings yet

- Jonson Valeo PDFDocument2 pagesJonson Valeo PDFnelson linceNo ratings yet

- Pin Out Fiat - ME7 5 20 PDFDocument2 pagesPin Out Fiat - ME7 5 20 PDFnelson linceNo ratings yet

- Suzuki Swift 1.3 Ignis 1.5 ECU wiringDocument4 pagesSuzuki Swift 1.3 Ignis 1.5 ECU wiringnelson linceNo ratings yet

- Opel Astra 17cdti 125Document4 pagesOpel Astra 17cdti 125nelson linceNo ratings yet

- Nissan 3plug Long Var5 GTRDocument4 pagesNissan 3plug Long Var5 GTRnelson linceNo ratings yet

- Suzuki Swift 13 IgnisDocument4 pagesSuzuki Swift 13 Ignisnelson linceNo ratings yet

- Nissan Navarra 2.5DCi 174cv ECU Connection GuideDocument4 pagesNissan Navarra 2.5DCi 174cv ECU Connection Guidenelson linceNo ratings yet

- Suzuki Swift 16 08 PDFDocument4 pagesSuzuki Swift 16 08 PDFnelson linceNo ratings yet