Professional Documents

Culture Documents

16

16

Uploaded by

SANTOSH KUMARCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

16

16

Uploaded by

SANTOSH KUMARCopyright:

Available Formats

International Journal of Innovations in Engineering and Technology (IJIET)

http://dx.doi.org/10.21172/ijiet.134.16

Design and analysis of (2x1) and (4x1)

Multiplexer circuit in Quantum Dot Cellular

Automata

Snehal Bhakre1, Aishwarya Tambe2, Sankit Kassa3

1

Snehal Bhakre, Usha Mittal Institute of Technology

2

Aishwarya Tambe, Usha Mittal Institute of Technology

3

Prof Dr. Sankit. R. Kassa, Dept. of Electronic and communication Engineering,

Usha mittal institute of Technology, Mumbai, Maharashtra, India

Abstract – Quantum dot Cellular Automata is novel nanotechnology that promise low-power, extremely dense and high speed

structure for construction of logical circuit at Nano-scale. One of such important logic circuit is Multiplexer. Multiplexer are

useful component for designing many important logic circuit. In this paper, we have presented the design of quantum dot

cellular automata (2x1) and schematic (4x1) multiplexer. The proposed design saves upto 63.15% number of QCA cells and

66% of area compared to previous design approaches. The simulations have been carried out using the QCA Designer, a

layout and simulation tool for QCA.

Key Words: Multiplexer, QCA cell, simulation, technology

I. INTRODUCTION

The ruling of CMOS transistors has enormous growth of the semiconductor industry for last fourty years. However, this

ruling boundary are meeting to its end now which leads in inventing new ways and technologies to size this ruling

problem. To seize this barrier of ruling there is one of the emerging technologies that is Quantum Dot Cellular Automata.

Fundamentally, QCA cell form an array or wire of cells which store information using electrons.

The fundamental unit of QCA cell is the OCA cell created with four Quantum Dots positioned at the vertices of a square

[4]. Coulomb repulsion between electrons will force them to occupy antipodal sides in the square. In this paper the

design and simulation of a (2x1) Multiplexer is presented. This QCA multiplexer is designed and simulated by using the

QCA Designer Tool.

1.1. QCA basic concept

1.1.1 QCA Cell

This technology is developed in cell. In each single cell there consists of four dots in which two electrons are present.

However, due to coulomb‟s law of electric repulsion the electrons acquire only two states in these dots. This complete

using the tunnels which are connected to the dots. This is connected to dots. Due to these tunnel electron can move from

one dot to another dot. So, these electron acquire two logic state that is logic‟0‟and logic‟1‟‟.

Figure 1: QCA cell and its logic

1.1.2. Basic Gates

1.1.2.1 Inverter:

The inverter gate is basically a not gate which is designed using QCA cell by placing two cells inverse to each other

(shown in figure.3). By putting the cell inversely we obtained output inverted of given input.

1.1.2.2 Majority Gate:

The most important gate of QCA cell is Majority gate. The majority gate consists three input and one output as shown in

figure 2. As the name implies, in these gate output is depend upon the majority of similar logic states of inputs. For

example. If two inputs are logic‟1‟, then output is logic‟1‟. This happens due to the electric field effect of input on the

Volume 13 Issue 4 July 2019 111 ISSN: 2319-1058

International Journal of Innovations in Engineering and Technology (IJIET)

http://dx.doi.org/10.21172/ijiet.134.16

output. By, fixing the polarization of one input as logic‟1‟or „0‟, we can obtain an OR gate and AND gate respectively.

The equation for majority gate is given as follows:

„Y=AB+BC+AC‟ (1)

Figure 2: Majority gate Figure 3: Inverter

1.1.2.3 Clock:

Clock in QCA cell play the most important role. Clock not only synchronize and control information flow but also

provide Power to the cell.

There are four phase in “Clock” signal that is, Switch, Hold, Release and Relax.

Figure 4: Clock stages in QCA

II. DESIGNING OF MULTIPLEXER USING QCA APPROACH

2.1. Definition:

Multiplexer is digital combinational circuit. An electronic multiplexer (MUX) allows a system to select one of several

input signals and forward it to the output. Due to these Mux can operated as a Switch. The input selection is done by

select line in multiplexer. As Multiplexer play an important role in Digital electronic.

Figure 5: Multiplexer

2.2. Design of (2x1) Multiplexer:

The given figure 5. Shows (2x1) Multiplexer having two inputs A and B, one selection line as S and one output line Y.

The equation for (2x1) Multiplexer is:

Y=AS‟+BS (2)

Volume 13 Issue 4 July 2019 112 ISSN: 2319-1058

International Journal of Innovations in Engineering and Technology (IJIET)

http://dx.doi.org/10.21172/ijiet.134.16

Table -1: Truth Table of (2x1) multiplexer

S A B Y

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 0

1 1 1 1

Figure 6: Schematic of (2x1)

Multiplexer

The schematic and layout in QCA for proposed (2x1) Multiplexer is as shown in Figure 6 and 7 respectively. The logic

diagram is shown in figure 8.

Figure 7: Proposed (2x1) Multiplexer Layout

Figure 8: Logic Diagram of (2x1) Multiplexer

Volume 13 Issue 4 July 2019 113 ISSN: 2319-1058

International Journal of Innovations in Engineering and Technology (IJIET)

http://dx.doi.org/10.21172/ijiet.134.16

The output for the layout of (2x1) Multiplexer using QCA simulation software is as shown in figure 9.

Figure 9

III. DESIGN OF (4X1) MULTIPLEXER

The Schematic (4x1) Mux is shown in figure 10. The design of (4x1) have same logic based on (2x1) Mux. It has four

input signal from A to D and two selection line i.e. S0 and S1.

The equation for (4x1) Multiplexer is:

Y=A.S0‟S1‟+B.S0‟S1+C.S0‟S1+D.S0S1 (3)

The truth table for (4x1) Multiplexer is as follow:

Table 2: Truth table for (4x1) Multiplexer is as follow:

S0 S1 A B C D Y

0 0 A 0 0 0 A

0 1 0 B 0 0 B

1 0 0 0 C 0 C

1 1 0 0 0 D D

The schematic for (4x1) Multiplexer is as shown in Figure10.

Volume 13 Issue 4 July 2019 114 ISSN: 2319-1058

International Journal of Innovations in Engineering and Technology (IJIET)

http://dx.doi.org/10.21172/ijiet.134.16

Figure 10: Schematic of (4x1) Multiplexer

IV. RESULT AND DISCUSSION

The simulation of proposed (2x1) Mux is done with help of QCA Designer simulation tool. The schematic and layout in

QCA for proposed (2x1) Multiplexer is as shown in figure 6 and 7 respectively. The simulation result of proposed (2x1)

Mux is shown in figure 9. These results are substantiated with the original truth table. From table 1, we can be see that

when S=0, then output we get is A and when S=1 then output is B. The proposed (2x1) Multiplexer requires 3 majority

gates, 1 inverter, 3 clock zones and total number of cells used are 28. The comparison shows that the proposed (2x1)

Multiplexer has 63.15% reduced cell count than that of existing designs. The (4x1) multiplexer can be designed using the

proposed (2x1) multiplexer design.

V. CONCLUSION

Multiplexers is an extremely important part of signal control system, as well as in Nanoelectronic because it allows the

system to choose one of several inputs to be forwarded to one output. The proposed designs are simulated using QCA

designer tool and is efficient in terms of cell count and area. The proposed design saves upto 63.15 % number of QCA

cells and 66 % of area compared to previous design approaches.

VI. ACKNOWLEDGEMENT

We would like to express our sincere thanks to our Principal, Dr. Sanjay Pawar and our Head of Department, Dr.

Shikha Nema for supporting and encouraging us to complete this work.

VII. REFERENCES

[1] Mukhopadhyay, D., Dinda, S. and Dutta, P. (2011). Designing and Implementation of Quantum Cellular Automata 2:1 Multiplexer Circuit.

International Journal of Computer Applications, 25(1), pp.21-24.

[2] Design and Implementation of Efficient Combinational Logic Circuits with Minimum Area and Circuit Complexity Using Quantum- dot Cellular

Automata (QCA). (2017). International Journal of Science and Research (IJSR), 6(1), pp.115-120

[3] C.S. Lent, P.D. Tougaw, W. Porod, and G.H.Bernstein, Quantum cellular automata,Nanotechnology, Vol.4, 1993, pp. 49–57.

[4] Sankit R Kassa, R.K.Nagaria, R. Karthik, “Energy efficient neoteric design of a 3-input Majority Gate with its implementation and physical proof

in Quantum dot Cellular Automata”, Nano Communication Networks, Elsevier Publication, vol. 15, pp.28-40, Feb 2018.

[5] Bilal, B., Ahmed, S. and Kakkar, V. (2018). An Insight into Beyond CMOS Next Generation Computing using Quantum-dot Cellular Automata

Nanotechnology. International Journal of Engineering and Manufacturing, 8(1), pp.25-3.

[6] Amlani, I., A.O. Orlov, G.H. Bernstein, C. S.Lent, G. L. Snider, Realization of a Functional Cell for Quantum-Dot Cellular Automata,Science,

Vol.227, No.5328, 1997, pp. 928-930.

[7] P. D. Tougaw and C. S. Lent, Logical devices implemented using quantum cellular automata,Applied Physics, Vol. 75, No.3, 1994, pp. 1818-

1825.

[8] Meurer, D. Heitmann, and K. Ploog,Excitation of three dimensional quantum dots,Physical Review, Vol.68, 1992, p.p. 137.

[9] Sankit R Kassa, R.K.Nagaria, “A novel design of quantum dot cellular automata 5-input majority gate with some physical proofs”, Journal of

Computational Electronics, Springer Publication, vol. 15 (1), pp.324-334, Mar 2016.

[10] Sankit R Kassa, R. K. Nagaria, “An innovative low power Full Adder design in Nano Technology based Quantum Dot Cellular Automata”,

Journal of Low Power Electronics , Vol. 12, no. 2, pp. 107-111. Impact Factor: 0.70.

Volume 13 Issue 4 July 2019 115 ISSN: 2319-1058

International Journal of Innovations in Engineering and Technology (IJIET)

http://dx.doi.org/10.21172/ijiet.134.16

[11] K Kim, K. Wu, and R. Karri, Towards Designing Robust QCA Architectures in the Presence of Sneak Noise Paths, Design Automation and Test

in Europe Proceedings,Vol. 2, 2005, pp.1214–19.

[12] Sankit R Kassa, R. K. Nagaria, “A Novel Design for 4-Bit Code Converters in Quantum Dot Cellular Automata”, Journal of Low Power

Electronics (American Scientific Publishers), Vol. 13, no. 3, pp. 482-489. Impact Factor: 0.70 (ESCI and Scopus Indexed Journal)

[13] Gin, S. Williams, H. Meng, and P. D.Tougaw, Hierarchical design of quantum-dotcellular automata devices, Applied Physics,Vol.85, No.7, 1999,

pp. 3713-20.

[14] V. Vankamamidi, M. Ottavi, and F. Lombardi Two-Dimensional Schemes for Clocking/Timing of QCA Circuits, Computer-Aided Design of

Integrated Circuits and SystemsIEEE Transactions, Vol.27, No.1, 2008, pp. 3.

[15] Karthik R, Sankit R Kassa, “Implementation of flip flops using QCA tool”, Journal of Fundamental and Applied Sciences, vol. 10, Issue 6S, pp.

2332-2341, (2018).

[16] M.Mustafa and M.R.Beigh, ―Design and implementation of Quantum Cellular Automata based novel Parity generator and checker circuits with

minimum complexity and cell count‖ ,Indian Journal of Pure & Applied Physics, vol. 451, pp. 60–60, Jan 2013.

[17] Francesco Bruschi, Francesco Perini,Vincenzo Rana and Donatella Sciuto ,― An Efficient Quantum-Dot Cellular Automata Adder,978-3-

9810801-7-9/DATE11/@2011 EDAA.

Volume 13 Issue 4 July 2019 116 ISSN: 2319-1058

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Ee3311 SyllabusDocument6 pagesEe3311 Syllabuskumarsanjeev.net9511No ratings yet

- Datasheet M3816nDocument8 pagesDatasheet M3816nRoberto SilvaNo ratings yet

- GRZ100D 6F2S0851 0.8rDocument462 pagesGRZ100D 6F2S0851 0.8rTiffany BeachNo ratings yet

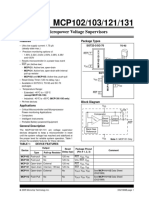

- Microchip MCP102T 315E - LB DatasheetDocument28 pagesMicrochip MCP102T 315E - LB DatasheetSebastian ChaileNo ratings yet

- Electronic Devices and Circuits Part 2Document9 pagesElectronic Devices and Circuits Part 2Renz Benhar Ocon BobadillaNo ratings yet

- 10 - DME 415-435 Vol 2 Ing Sect 09 TKW Thales March 03Document26 pages10 - DME 415-435 Vol 2 Ing Sect 09 TKW Thales March 03Vagner AndréNo ratings yet

- Ideas at Projects For QRP: Published by Free E-Magazine AntentopDocument211 pagesIdeas at Projects For QRP: Published by Free E-Magazine AntentopSimona Konyar100% (3)

- Las Week 2 Smaw Grade 9Document8 pagesLas Week 2 Smaw Grade 9Hebe KamaNo ratings yet

- 1N4719-1N4725.1N4997-1N5005: Silicon RectifiersDocument1 page1N4719-1N4725.1N4997-1N5005: Silicon RectifiersbozajaNo ratings yet

- Lab 6Document2 pagesLab 6mohhassonaNo ratings yet

- Indian Institute of Science: BangaloreDocument7 pagesIndian Institute of Science: BangaloreAbhinab MohapatraNo ratings yet

- Joint Course Three Phase Drives Lecture B WDocument19 pagesJoint Course Three Phase Drives Lecture B WS JainNo ratings yet

- Balanced To UnbalancedDocument4 pagesBalanced To Unbalancedbvogeler4007No ratings yet

- Multistage AmplifiersDocument18 pagesMultistage AmplifiersSaurabhSinghNo ratings yet

- Single Stage Solar PV Fed Brushless DC Motor Driven Water PumpDocument7 pagesSingle Stage Solar PV Fed Brushless DC Motor Driven Water PumpkrishnaNo ratings yet

- Input ModuleDocument19 pagesInput ModuleanantsraoNo ratings yet

- Tms 320 C 6711 BDocument132 pagesTms 320 C 6711 BKalyan ChakravarthyNo ratings yet

- 117 Practical Ic Projects You Can BuildDocument100 pages117 Practical Ic Projects You Can BuildPopa Andreytza AndreeaNo ratings yet

- Chloride FP 40r Ds en GL 0616 Rev6Document2 pagesChloride FP 40r Ds en GL 0616 Rev6Tanveer Ahmed100% (1)

- Transistor-To-Transistor Logic (TTL) :-: Noise MarginDocument5 pagesTransistor-To-Transistor Logic (TTL) :-: Noise MarginDulichand SainiNo ratings yet

- Rs 400-ManualDocument11 pagesRs 400-Manualbabaisandip50% (8)

- How Do Leds WorkDocument7 pagesHow Do Leds WorkeveltoncNo ratings yet

- Small DC Motor Control by PWM Method Using Atmega8Document4 pagesSmall DC Motor Control by PWM Method Using Atmega8Emin KültürelNo ratings yet

- Good TextDocument74 pagesGood TextlightfantacyNo ratings yet

- 32pfl4508 PDFDocument50 pages32pfl4508 PDFStevenson GodoyNo ratings yet

- Soldadora UTC3843DDocument9 pagesSoldadora UTC3843DChristian ormeñoNo ratings yet

- 9702 m17 Ms 42Document11 pages9702 m17 Ms 42Imran ZafarNo ratings yet

- Solutions AIATS Med-2020 (OYMCF) Test-01 (Code-A&B) 28-07-2019Document32 pagesSolutions AIATS Med-2020 (OYMCF) Test-01 (Code-A&B) 28-07-2019Aditya LalNo ratings yet

- Esh 1 BDocument5 pagesEsh 1 Basam youssefNo ratings yet

- Homemade 3kW Induction Heater - First Prototype Test - YouTubeDocument9 pagesHomemade 3kW Induction Heater - First Prototype Test - YouTubeJoel Antonio Lopez LopezNo ratings yet