Professional Documents

Culture Documents

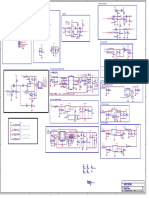

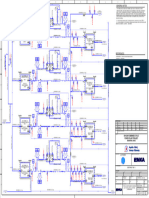

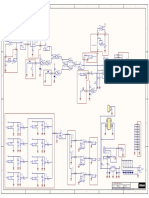

Antennas SIM7600 Host Connector: (Optional, For FW Update)

Uploaded by

salasugo5751Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Antennas SIM7600 Host Connector: (Optional, For FW Update)

Uploaded by

salasugo5751Copyright:

Available Formats

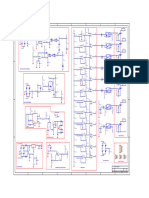

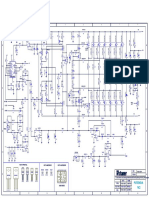

1 2 3 4 5 6 7 8

Antennas Host connector

SIM7600 5v

MAIN_ANT

R12

0R

R13

0R

1 J4

Maj version The version resistor forms a voltage divider with a

40.2K resistor on the host board. The host then can

U1A sim7600 D4 IPX 0 Dev read the version as an analog voltage value.

LXES15AAA1-153

J5

LED_B

2

1 Check out the table.

D6 TVS

A 22 82 MAIN_ANT IPX C6 C9 A

SD_DATA0 MAIN__ANT 2 2 2G

23 79 GNSS_ANT DNP DNP

SD_DATA1 GNSS_ANT 3

24 59 AUX_ANT R10 DNP DNP

SD_DATA2 AUX_ANT GND 4 4G

25 470R

SD_DATA3 Test point 5

21

SD_CMD

3

Place close to the chip 6

NMOS

GND GND GND GND WiFi

26

WST3400S

SD_CLK 51 7

48 NETLIGHT

SD_DET 54 TestPoint 1 8

FLIGHTMODE R11

TP2 R14 R15

2

49 9

SIM_IO 17 STATUS 40.2k

USIM_DATA 52 0R 0R

Q1

SIM_RST 18 GPIO41 AUX_ANT 1 J6

USIM_RST 50

SIM_CLK 19 GPIO43 IPX

LXES15AAA1-153

USIM_CLK 33

GPIO3

2

SIM_VCC 20

D7 TVS

USIM_VDD 34 GND C10 C11

53 GPIO6

USIM_DET 87 DNP DNP

GPIO77 VER_1 = 0 R1 R2 VER_2 = 1

DNP DNP J2

VBUS 11 DNP 340k

USB_VBUS Host

D_P 13 45 DNP

USB_DP ISINK 3v3 1 2 VER_1 3v3

D_N 12 47 GND GND GND GND

USB_DN ADC1 3 4 VER_2

16 46 GND

USB_ID ADC2 5v 5 6

83

COEX1 7 8 POWER

UART_RX_1v8 68 84 R16 L1 GND

RXD COEX2 SPI_MISO_3v3 9 10 SPI_CLK_3v3

B 10R 47nH B

GND

UART_TX_1v8 71 86

TXD COEX3 5v SPI_MOSI_3v3 11 12 UART_RX_3v3

67 TP1

CTS UART_TX_3v3 13 14 nCS_WIFI

66 TestPoint

RTS nCS_3G_3v3 15 16 nRST

70 85

DCD BOOT_CFG0

72 42

DNP

C13

C12

DTR NC

DNP

69 33pF C0G

RI

1 1v8 GNSS_ANT 1 J8

J7

Conn_01x04

2 55

SCL

PWRKEY

3

GND

0402CG330J500NT

IPX

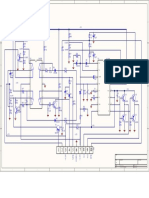

Level shifters

2

3 56

SDA 4 L2 L3

DNP 4 RESET

TVS

TVS

DNP DNP

2

30 3v3 level

1.8v <-> 3.3v

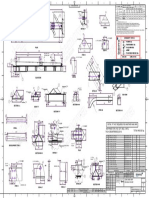

Mounting

SDIO_DATA0 Q3 DNP DNP

MP

27 nRST

GND SDIO_DATA1 PMOS

D8

D9

28 6 SPI_CLK_1v8 1

AO3401

ESD5Z3V3

SDIO_DATA2 SPI_CLK

TVS

ESD5Z3V3

ESD5Z3V3

3

GND 31 7 SPI_MISO_1v8 GND GND GND

SDIO_DATA3 SPI_MISO 1v8 3v3

29 8 SPI_MOSI_1v8

SDIO_CMD SPI_MOSI

32 9 SPI_CS_1v8

D5

SDIO_CLK SPI_CS R3 R4

USB

1

GND 4.7k 4.7k

73

PCM_OUT UART_RX_1v8 UART_RX_3v3

74 35 GND GND 2 3

PCM_IN HSIC_STROBE

75 36

C

76

PCM_SYNC

PCM_CLK

HSIC_DATA

(Optional, for FW update) Q4 NMOS

WST3400S

Vth < 1.8v C

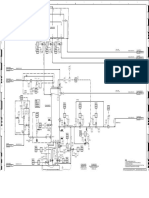

D10

SS14 VBUS 1v8 3v3

SS14F

VBUS

J3 5v U2

5

R5 R6

USBLC6-2SC6

1

USB_OTG 4.7k 4.7k

USBLC6-2SC6

1 VBUS UART_TX_1v8 UART_TX_3v3

VBUS D_N IO1 IO2 D_P 2 3

6 4

3 D_P Q2 NMOS Vth < 1.8v

D+ IO1 IO2

2 D_N WST3400S

1 3

Shield

D-

GND

H1 H2 4

ID 1v8 3v3

MountingHole_Pad MountingHole_Pad

GND

6

5

2

R17 R18

1

4.7k 4.7k

SPI_MISO_1v8 SPI_MISO_3v3

GND GND 2 3

Q5 NMOS Vth < 1.8v

WST3400S

D 1v8 3v3 D

R20 R21

1

USIM Card SPI_MOSI_1v8

4.7k

2 3

4.7k

SPI_MOSI_3v3

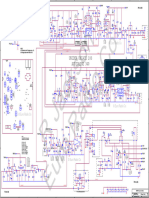

Power supply

330uF 6.3v C14

330uF 6.3v C15

1uF 16v X5R C16

0.1uF 50v X5R C17

Q6 NMOS Vth < 1.8v

C1 WST3400S

0.1uF 50v X5R

1v8 3v3

22uF 16v X5R C19

GND SIM_VCC 1

VCC R24 R25

suggests 10uF

1

6 8

0.1uF 50v X5R

VPP GND 4.7k 4.7k

SIM_RST R7 22R 2 9

22uF 16v X5R C22

Datasheet

RST GND SPI_CLK_1v8 SPI_CLK_3v3

SIM_IO R8 22R 7 10

U1B I/O GND 2 3

sim7600 SIM_CLK R9 22R 3 11

0.1uF 50v X5R

Datasheet CLK GND Q7 NMOS Vth < 1.8v

5

100pF C0G

suggests 4.7uF V_BATT GND WST3400S

C18

38 1

VBAT GND GND

5v 39 2 P1 GND

VBAT GND

U3 5 SK-C793

C20

L4 GND 1v8 3v3

M3406-ADJ

4

C21

62 10

ESD5Z3V3

ESD5Z3V3

ESD5Z3V3

E 3.3uH 1A VBAT GND E

VIN

3 63 14

SW VBAT GND R26 R27

GND GND

1

POWER 1 37

TVS

TVS

TVS

RUN GND 4.7k 4.7k

33pF C0G

33pF C0G

33pF C0G

FB R19

GND

5 44 40

GND GND R22 VOUT VDD_AUX GND SPI_CS_1v8 nCS_3G_3v3

40.2k 1v8 15 41

D1

D2

D3

40.2k VDD_1V8 GND 2 3

2

43

GND Q8 NMOS Vth < 1.8v

R23 57

GND WST3400S

0.1uF 50v X5R

C2

C4

C3

GND 6.98k GND GND 58

1uF 16v X5R

GND GND

330uF 6.3v

C23 330uF 6.3v

77 60

GND GND GND

78 61

GND GND

GND 80 64

GND GND

Vout = 0.6 * (R1 + R2) / R2 81 65

GND GND

C5

C7

C8

Vout = 0.6 * (40.2 + 6.98) / 6.98

Alexey Zaytsev / Okra Solar

Vout = 4.06

Sheet: /

GND

GND File: cicada-4g.sch

Title: Ciacada 4G

Size: A3 Date: 2019-04-02 Rev: 0.1

KiCad E.D.A. kicad (5.1.0-10-g6006703) Id: 1/1

F F

1 2 3 4 5 6 7 8

You might also like

- Kidnap The ArchpriestDocument52 pagesKidnap The Archpriestgmvasco67% (3)

- Post Building Techniques NX8Document267 pagesPost Building Techniques NX8Dolvando Ferreira Alves Filho100% (1)

- TP - MS338.PB801 A15513 Schematic PDFDocument11 pagesTP - MS338.PB801 A15513 Schematic PDFsachin57% (14)

- Bridge Design Sample Autocad-2Document1 pageBridge Design Sample Autocad-2DINESHNo ratings yet

- CR-10 SchematicDocument1 pageCR-10 SchematicNguyễn TâmNo ratings yet

- 17IPS20Document2 pages17IPS20Antonio Verdu AlfonsoNo ratings yet

- 40 Mt56ee Mad2hgDocument11 pages40 Mt56ee Mad2hgcharly36100% (5)

- Orgonium Orgone Energy ResearchDocument37 pagesOrgonium Orgone Energy Researchlnln462ln100% (1)

- PC 2 Route For Mach Rev 1-9Document18 pagesPC 2 Route For Mach Rev 1-9Kenn FerroNo ratings yet

- "The Day The Saucers Came" by Neil GaimanDocument6 pages"The Day The Saucers Came" by Neil GaimanMadeup NamezNo ratings yet

- Rsag7 820 4900Document10 pagesRsag7 820 4900Isabel GarciaNo ratings yet

- Gamp SchematicDocument2 pagesGamp SchematicStratoNo ratings yet

- 电气原理图Document1 page电气原理图Ruimin Cheng100% (1)

- Multislope 3IDocument1 pageMultislope 3Iessen999No ratings yet

- (14-21"color TV Basic Schematic Diagram) : CRT BoardDocument1 page(14-21"color TV Basic Schematic Diagram) : CRT BoardAndrei Blas Azaña100% (1)

- Ka7500 PDFDocument1 pageKa7500 PDFValerică Hizanu100% (1)

- Diagrama Electrico Thorben HTR SlimDocument1 pageDiagrama Electrico Thorben HTR SlimFelipe Andres Lizana BastiasNo ratings yet

- Minimot (2R5) - Bivolt (1) 10 12 07Document1 pageMinimot (2R5) - Bivolt (1) 10 12 07Cezao DoidãoNo ratings yet

- Schematics Uv82Document1 pageSchematics Uv82Imo AntennaNo ratings yet

- P0167 Schematic Diagram Main RevF 2009-03-26 Rev.0Document6 pagesP0167 Schematic Diagram Main RevF 2009-03-26 Rev.0Jorge MuñozNo ratings yet

- VESTEL 17MB45m-2Document9 pagesVESTEL 17MB45m-2eduardoNo ratings yet

- Vga Input: Scart Video Output AmplifierDocument9 pagesVga Input: Scart Video Output AmplifierHoson AkNo ratings yet

- Schema ReceptorDocument1 pageSchema ReceptorDaniel TaradaciucNo ratings yet

- General NotesDocument1 pageGeneral Notesmustafa1989ocNo ratings yet

- 96pcaa00003-Amp PcbaDocument2 pages96pcaa00003-Amp PcbaassistenzadavidoffstoreNo ratings yet

- Uniace 100 SCHDocument1 pageUniace 100 SCHGabor BodnarNo ratings yet

- 6 7 1 2 5 6 7 8 + + TR1 R443 C83 L7 C9 L2: L2 Must Be Placed and Soldered by HandDocument8 pages6 7 1 2 5 6 7 8 + + TR1 R443 C83 L7 C9 L2: L2 Must Be Placed and Soldered by HandBetriebs RatNo ratings yet

- Sis 8670 WDDocument1 pageSis 8670 WDtomekawa1967No ratings yet

- 5f6a ApproachDocument1 page5f6a Approachdisse_detiNo ratings yet

- Stark 3.2Document1 pageStark 3.2Matheus GustavoNo ratings yet

- Maixduino 2832 (Schematic)Document1 pageMaixduino 2832 (Schematic)luis1983tiagoNo ratings yet

- Diagrama Esquematico Rossi KXH 30 v1 PDF FreeDocument1 pageDiagrama Esquematico Rossi KXH 30 v1 PDF FreeDaniel aguiar soaresNo ratings yet

- Makita dc18sf Battery Charger SCHDocument3 pagesMakita dc18sf Battery Charger SCHNorberto GonzalezNo ratings yet

- President Lincoln II Version 3 SchematicDocument13 pagesPresident Lincoln II Version 3 Schematicalf100% (1)

- TP MT5507 PC821+Schematics+DiagramDocument12 pagesTP MT5507 PC821+Schematics+DiagramHumberto AguilarNo ratings yet

- Power Input: IN GND BS Comp EN SS SWDocument10 pagesPower Input: IN GND BS Comp EN SS SWjesurajanNo ratings yet

- Css Delay CF Rfmin Stby Isen Line Dis Pfc-Stop GND LVG VCC NC Out HVG VbootDocument1 pageCss Delay CF Rfmin Stby Isen Line Dis Pfc-Stop GND LVG VCC NC Out HVG VbootMarcos KettlNo ratings yet

- Clayton A2 Sheet 06Document1 pageClayton A2 Sheet 06deejay dvaidNo ratings yet

- Behringer B215DDocument3 pagesBehringer B215DEdgar PadillaNo ratings yet

- General Notes:: Dhi Qar Combined Cycle Power Plant ProjectDocument1 pageGeneral Notes:: Dhi Qar Combined Cycle Power Plant Projectmustafa1989ocNo ratings yet

- ss3900 Ept360015c MosfetDocument1 pagess3900 Ept360015c MosfetANSELMO LIMA0% (1)

- OUT VIN: Gnd/AdjDocument15 pagesOUT VIN: Gnd/AdjJose radhames ColladoNo ratings yet

- Fuelino p4 SchematicsDocument1 pageFuelino p4 SchematicsAhmad Azriel DaffarisandiNo ratings yet

- Despi-M02 - SCH V1.0Document1 pageDespi-M02 - SCH V1.0Nguyen Vu Hoang ThachNo ratings yet

- ESP32-PoE Rev B2 ColorDocument1 pageESP32-PoE Rev B2 ColorAlexNo ratings yet

- Vendor:: Column Cell No.1 Column Cell Feed DistributorDocument1 pageVendor:: Column Cell No.1 Column Cell Feed DistributorJoseph Junior Jahuira TaparaNo ratings yet

- Power Supply Inverter Vestel 17IPS20P-R3Document2 pagesPower Supply Inverter Vestel 17IPS20P-R3maciekreNo ratings yet

- Vestel 17ips20p-R5 SCHDocument2 pagesVestel 17ips20p-R5 SCHAnonymous XoW23y58O100% (1)

- Nb-Solis 3.0 - Aut - Biv - Rev04Document1 pageNb-Solis 3.0 - Aut - Biv - Rev04Fernando SilvaNo ratings yet

- Schematis MIMO1Document1 pageSchematis MIMO1Trần Thái BảoNo ratings yet

- EDC17C44-1.1 SchaltbildDocument9 pagesEDC17C44-1.1 SchaltbildT HNo ratings yet

- Epcc05 MDR 421 STR DWG 000 0072 16Document1 pageEpcc05 MDR 421 STR DWG 000 0072 16RANJEET PRATAP SINGHNo ratings yet

- TPD - MS638.PB735 A16047 Schematic DiagramDocument11 pagesTPD - MS638.PB735 A16047 Schematic DiagramGeovanny SanjuanNo ratings yet

- TPD - MS338.PB792 Schematic DiagramDocument11 pagesTPD - MS338.PB792 Schematic DiagramPedro GoisNo ratings yet

- China TD21P8 M61266, M37160, Tea1506p, La9302Document1 pageChina TD21P8 M61266, M37160, Tea1506p, La9302Luis Liammas PerezNo ratings yet

- X0231 PDW Eut DG 20007 AaDocument1 pageX0231 PDW Eut DG 20007 AajianranrenNo ratings yet

- Document Status: If in Doubt AskDocument1 pageDocument Status: If in Doubt AskNitinNo ratings yet

- 01 B276e5 MaaDocument1 page01 B276e5 MaaRenxio KahuaNo ratings yet

- 1K2 PotDocument1 page1K2 PotcbsomtecladosNo ratings yet

- Sequence 8 SchematicDocument1 pageSequence 8 SchematicMaarfy CZNo ratings yet

- Fill Your Glass With Gold-When It's Half-Full or Even Completely ShatteredFrom EverandFill Your Glass With Gold-When It's Half-Full or Even Completely ShatteredNo ratings yet

- Instant Assessments for Data Tracking, Grade 5: Language ArtsFrom EverandInstant Assessments for Data Tracking, Grade 5: Language ArtsNo ratings yet

- February Monthly Collection, Grade 5From EverandFebruary Monthly Collection, Grade 5Rating: 3 out of 5 stars3/5 (1)

- Literature Review Template UnisaDocument7 pagesLiterature Review Template Unisaafmzvjvjzoeqtg100% (1)

- J. R. D. Tata - Google SearchDocument5 pagesJ. R. D. Tata - Google SearchoffyNo ratings yet

- Some Websites To LearnDocument7 pagesSome Websites To LearnNanh NabiNo ratings yet

- CAF 8 AUD Autumn 2022Document3 pagesCAF 8 AUD Autumn 2022Huma BashirNo ratings yet

- 3D Laser ScannerDocument100 pages3D Laser ScannerVojta5100% (1)

- Ketan Parekh ScamDocument13 pagesKetan Parekh ScamUttam Kr PatraNo ratings yet

- Route Oct 2019Document445 pagesRoute Oct 2019Alex AndruNo ratings yet

- Dragon Magazine #237Document124 pagesDragon Magazine #237Anonymous OwiutM4l50% (2)

- Advances in Energy Research, Vol. 1: Suneet Singh Venkatasailanathan Ramadesigan EditorsDocument734 pagesAdvances in Energy Research, Vol. 1: Suneet Singh Venkatasailanathan Ramadesigan EditorsVishnuShantanNo ratings yet

- Ketogenic Diet PresentationDocument64 pagesKetogenic Diet Presentationstefanie_561186832100% (2)

- Valeroso vs. CA Case DigestDocument1 pageValeroso vs. CA Case DigestMarivic Veneracion100% (2)

- Information TechnologyDocument9 pagesInformation TechnologyyadawadsbNo ratings yet

- Literature Review PiezoelectricDocument5 pagesLiterature Review Piezoelectricfihynakalej2100% (1)

- PH13-5C-228-33-0050 - 66kV CABLE FEEDER - R0 - 1Document42 pagesPH13-5C-228-33-0050 - 66kV CABLE FEEDER - R0 - 1prakashNo ratings yet

- Evaporative Emission Control System: GeneralDocument5 pagesEvaporative Emission Control System: Generalbob loblawNo ratings yet

- Your Partner For Offshore Floating ProductionDocument20 pagesYour Partner For Offshore Floating ProductionHmidaNo ratings yet

- Proceedure and Macros - More ExplanationsDocument2 pagesProceedure and Macros - More ExplanationsShantanu BhattacharyaNo ratings yet

- Sony Kv-29cl10k Chassis Fe2 (ET)Document52 pagesSony Kv-29cl10k Chassis Fe2 (ET)khafjiNo ratings yet

- Pharmacology of Vitamins: DR - Datten Bangun MSC - SPFK Dept - Farmakologi & Therapeutik Fak - Kedokteran Uhn MedanDocument41 pagesPharmacology of Vitamins: DR - Datten Bangun MSC - SPFK Dept - Farmakologi & Therapeutik Fak - Kedokteran Uhn Medanraranaomi29No ratings yet

- Adverbs of IntensityDocument23 pagesAdverbs of IntensityRose D GuzmanNo ratings yet

- Pelicano Dalmata InstDocument9 pagesPelicano Dalmata InstEsteban NichoNo ratings yet

- Clinical InterviewDocument29 pagesClinical InterviewVasundhara RanaNo ratings yet

- Oracle9i Database - Advanced Backup and Recovery Using RMAN - Student GuideDocument328 pagesOracle9i Database - Advanced Backup and Recovery Using RMAN - Student Guideacsabo_14521769No ratings yet

- Bending Tools RF-A English - OriginalDocument116 pagesBending Tools RF-A English - OriginalGunnie PandherNo ratings yet

- Ksa 2211 Kiswahili Sociolinguisticscu 4CH 60Document2 pagesKsa 2211 Kiswahili Sociolinguisticscu 4CH 60Akandwanaho FagilNo ratings yet