Professional Documents

Culture Documents

FV-1 Reverb IC: ADC DAC

FV-1 Reverb IC: ADC DAC

Uploaded by

Chandrashekhar KulkarniOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FV-1 Reverb IC: ADC DAC

FV-1 Reverb IC: ADC DAC

Uploaded by

Chandrashekhar KulkarniCopyright:

Available Formats

Spin

Semiconductor

FV-1 Reverb IC

Featuring Spin Semiconductor Virtual Analog Technology

Spin Semiconductor FV-1 Reverb IC PN: SPN1001

FEATURES APPLICATIONS

○ Integrated stereo ADC and DAC

○ 8 internal demonstration programs + 8 external ○ Guitar Amps

programs ○ Mixers

○ Easy customization with external EEPROM ○ Effects Equipment

○ 3 potentiometer inputs for real-time parameter ○ Karaoke

adjustment ○ Consumer electronics

○ 3.3V operation ○ Car audio

○ 6 MIPS operation at Fs=48KHz ○ Active loudspeaker crossover and flattening

○ 128 instructions/sample clock ○ Industrial processes

○ 32K words of delay RAM

○ Internal PLL for Fs input clock

○ Integrated Power-On-Reset circuit

○ LOG and EXP instructions for dynamics

○ Green assembly/RoHS compliant

Power On

Reset

Delay

Memory

Analog Left In Analog Left Out

ADC DSP CORE DAC

Analog Right In Analog Right Out

Potentiometer Potentiometer

Program Select ROM and

interface

Program Inputs

ROM/EEPROM Control

Select PLL

EEPROM Interface

EEPROM FV1

Interface XTAL Drvr

SPN1001

XTAL

Spin

Semiconductor

www.spinsemi.com SPN1001-DS-170829 – 29 August 2017

Spin

Semiconductor

FV-1 Reverb IC

Featuring Spin Semiconductor Virtual Analog Technology

LIN 1 28 LOUT

RIN

MID FV-1 ROUT

REFP

GND

CLIP

SPN1001 REFN

GND

AVDD 28 SOIC DVDD

GND POT2

DVDD POT1

X2 POT0

X1 GND

GND S2

T1 S1

T0 S0

SCK 14 15 SDA

Pin Name Description

1 LIN Left analog in

2 RIN Right analog in

3 MID Mid reference

4 GND Ground

5 CLIP Clip LED output

6 AVDD Analog power (3.3V)

7 GND Ground

8 DVDD Digital power (3.3V)

9 X2 Crystal oscillator input

10 X1 Crystal oscillator input

11 GND Ground

12 T1 Tie to GND for normal operation

13 T0 0: Use internal ROM programs, 1: Use programs from external EEPROM

14 SCK EEPROM clock (Internal pull up)

15 SDA EEPROM data (Internal pull up)

16 S0 Program select LSB

17 S1 Program select

18 S2 Program select MSB

19 GND Ground

10 POT0 Potentiometer 0 analog input

21 POT1 Potentiometer 1 analog input

22 POT2 Potentiometer 2 analog input

23 DVDD Digital power (3.3V)

24 GND Ground

25 REFN Negative reference

26 REFP Positive reference

27 ROUT Right analog out

28 LOUT Left analog out

Spin

Semiconductor

www.spinsemi.com SPN1001-DS-170829 – 29 August 2017

Spin

Semiconductor

FV-1 Reverb IC

Featuring Spin Semiconductor Virtual Analog Technology

Absolute Maximum Ratings1

MIN MAX UNIT

AVDD Analog supply voltage -0.5 3.5 V

DVDD Digital supply voltage -0.5 3.5 V

AVI Analog input voltage range -0.5 AVDD+0.5 V

DVI Digital input voltage range -0.5 DVDD+0.5 V

IIC Input signal current ±20 mA

IOC Output clamp current ±20 mA

IO Continuous output current ±20 mA

Continuous current through VDD or GND ±100 mA

Maximum power dissipation 300 mW

Storage temperature range -50 150 °C

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Operation of the device at these or

any other conditions beyond those indicated under "Recommended Operating Conditions" is not guaranteed. Exposure to absolute-maximum-rated

conditions for extended periods may affect device reliability.

Recommended Operating Conditions

AVDD Analog supply voltage 3.3V

DVDD Digital supply voltage 3.3V

REFP Positive reference 3.3V

REFN Negative reference 0V

TOP Operating temperature 0 – 70 °C

Electrical Characteristics (X1, X2 = 32768Hz crystal, DVDD=AVDD=REFP=3.3V, REFN=0v, measurements over 20-16Khz band)

Characteristic Min Typ Max Units

Analog input impedance 80 120 KΩ

Analog output impedance 50 200 Ω

Allowable load resistance 10 KΩ

Maximum input signal level 2.6 3.0 VP-P

Maximum output signal level 2.6 3.0 VP-P

Channel gain mismatch 0.2 dB

ADC equivalent input noise (A weighted) -97 -93 dB

DAC output noise (A weighted) -97 -93 dB

THD (1KHz, -1db from clipping) 0.015 0.03 %

ADC-DAC HF response (-3dB) 14.5 15.5 KHz

Passband flatness ±0.5 dB

Total internal memory delay (@32.768KHz sample rate) 1.0 seconds

Potentiometer control input impedance 10 20 MΩ

X1, X2 internal capacitance 8 15 pF

X1, X2 internal bias resistance 7 14 MΩ

Supply current (AVDD + DVDD) 40 55 70 mA

REFP supply current 30 50 μA

SDA and SCK internal pull up - Typical 3.75 KΩ

Spin

Semiconductor

www.spinsemi.com SPN1001-DS-170829 – 29 August 2017

Spin

Semiconductor

FV-1 Reverb IC

Featuring Spin Semiconductor Virtual Analog Technology

General Description

The Spin Semiconductor FV-1 is a complete reverb solution in a single IC. With integrated stereo ADC and DACs, the FV-

1 can be treated like any other analog component in your products signal path.

The FV-1 can access a total of 16 programs, 8 programs are built in to the internal ROM and the designer may elect to

connect a serial EEPROM with 8 additional programs. By using an external EEPROM, the designer can distinguish his

product from others by creating a custom program set without the need for a microprocessor in the system.

With 3 potentiometer inputs, programs may have real time variable parameters such as decay time in a reverb, rate and

depth in a chorus or frequency in a filter. These inputs are available as coefficients to your program and may be used

independently of each other.

The rich instruction set allows users to program effects of all kinds. With instructions like LOG and EXP, users can easily

program audio expansion and compression routines. Integrated digital LFOs and ramp generators allow for programming

chorus, flange and pitch shift.

A complete development system including assembler and development board with USB interface are available from Spin

Semiconductor. The assembler and instruction set documentation are available free from the Spin web site along with

example code that may be freely used in your product.

ROM Programs

The FV-1 includes 8 programs in the internal ROM, these programs and the assigned potentiometer input controls are

detailed in Table 1.

Table 1 - ROM Programs

Prg # Description POT0 POT1 POT2

0 Chorus-reverb Reverb mix Chorus rate Chorus mix

1 Flange-reverb Reverb mix Flange rate Flange mix

2 Tremolo-reverb Reverb mix Tremolo rate Tremolo mix

3 Pitch shift Pitch +/-4 semitones - -

4 Pitch-echo Pitch shift Echo delay Echo mix

5 Test - - -

6 Reverb 1 Reverb time HF filter LF filter

7 Reverb 2 Reverb time HF filter LF filter

DSP Core

The DSP core of the FV-1 provides many advanced features and instructions that allow you to create advanced programs

to make your product stand out. The DSP core consists of the MAC/ALU where all math and logic instructions take place,

the LOG and EXP blocks that perform the log and exponential functions, a 32-register bank separate from the delay RAM

and LFO and ramp generators that can offset memory addressing.

A complete list and description of instructions is available in the assembly language manual that is included on the CD in

the development kit or may be downloaded from the Spin Semiconductor web site.

Spin

Semiconductor

www.spinsemi.com SPN1001-DS-170829 – 29 August 2017

Spin

Semiconductor

FV-1 Reverb IC

Featuring Spin Semiconductor Virtual Analog Technology

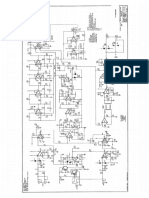

Typical Application

The FV-1 is extremely easy to include in any audio system, but certain details should be considered. For all practical

purposes, the FV-1 can be treated as an analog part. Although the FV-1 is fully digital internally, it has been designed with

internal power supply bypassing and careful attention to signal pin protection devices so that only a clean power supply

and expected analog techniques are required at the PCB level.

Figure 1 – Typical application

15p

See

Not e

NOTE: The actual value of this

capacitor can range from 15pf

to 27pf. This depends on the

manufacturer you use as the

characteristics of the crystals vary

from one manufacturer to another.

The inputs should be conducted through coupling capacitors, as the inputs are internally biased to a VDD/2 potential. The

input signals should be led through 1K resistances with 1nF capacitors directly to ground as close as possible to the input

pins. These bypass capacitors should be of good quality, either film capacitors or NP0 (COG) ceramic. The purpose of

Spin

Semiconductor

www.spinsemi.com SPN1001-DS-170829 – 29 August 2017

Spin

Semiconductor

FV-1 Reverb IC

Featuring Spin Semiconductor Virtual Analog Technology

this input bypassing is to remove any high frequency noise from the input signals, and to provide a low impedance at very

high frequencies.

The outputs may contain out of band noise that can be more fully removed through the use of a two-pole active filter, but

for most applications this noise is both inaudible and of no consequence to following circuitry. A simple RC filter is

sufficient to remove any high frequency components, if required.

The output mute circuit, internal to the device, inserts a 100K ohm resistance in series with output pins during device

power-up, which allows the output coupling capacitors to slowly become biased to the nominal output voltage of VDD/2.

The load resistance on the outputs should be no less than 10K ohms so as to not overload the output drivers, and the

coupling capacitor should have a time constant with the load resistance of about 20 to 50ms. The power up delay will be

approximately 0.5 to 1 second, depending on crystal properties.

The clip LED is optional, but will flash for approximately 30mS if the internal ADC or the DAC are driven to within a few

tenths of a dB of full scale. Any overflow from internal processing that does not produce a near full scale output will not

light the clip LED.

Digital power should be bypassed with a ceramic capacitor to ground with very short leads to the part. Ideally, the design

will be onto a double sided PCB with the lower layer as a solid pour, connected to ground. This provides a convenient low

inductance connection for bypass capacitors through vias. A single sided PCB can be used provided that a large ground

area is included beneath the chip and surface mount bypass capacitors are connected from supply pins to this ground as

close to the chip as possible.

Likewise, the REFP and REFN pins should have a bypass cap attached close to the part, with a resistor to supply from

VDD. The current drawn by the REFP terminal is small, on the order of 30uA, so there will be only a slight voltage drop

across the reference series resistor. The input and output signal levels however, will be a function of the potential across

the REFP and REFN pins. Be careful to not make the series filter resistor between VDD and the REFP pin too large, or

signal levels will be affected.

The input resistance of the potentiometer control inputs is on the order of 10 megohms, and these terminals are quite

resistant to noise. No bypass capacitors should be required on these terminals. If not required, these terminals may be left

open, or if the program includes the use of a potentiometer function, it may be connected to MID if a centered

potentiometer position is desired, but an actual control is not intended in the design.

The crystal oscillator is designed for the standard 32768 Hz watch crystal, as this is particularly inexpensive, but any logic

level clock source can be attached to the X1 terminal directly. The sample rate of the system will be at this applied rate. At

32768Hz, the ADC and DAC bandwidth will be 15KHz, at a clock frequency of 48KHz, the bandwidth will expand to

beyond 20KHz. Watch crystals have a very high Q factor, and require significant time to develop full level oscillation. All

support components for the crystal are included internal to the device, including a 10Meg bias resistor and two 12pF

capacitors. The lead length however, between the crystal and the part must be as short as possible. Further, beware that

the loading of a scope probe on the X1 pin may cause the oscillator to stop. If you wish to check the oscillator's operation,

use X2 as a measurement point. Depending on the supplier of the crystal there can be a startup problem with the crystal,

it is recommended that all designs include a 15pf capacitor between X2 and ground.

The use of an external EEPROM is optional, and in the case of designs that do not make use of this expansion option, the

SCK and SDA pins may be left open. T1 however must be grounded, and T0 must be connected to ground (internal

programs) or VDD (EEPROM programs).

Spin

Semiconductor

www.spinsemi.com SPN1001-DS-170829 – 29 August 2017

Spin

Semiconductor

FV-1 Reverb IC

Featuring Spin Semiconductor Virtual Analog Technology

Outline Dimensions

Dimensions shown in inches (mm)

.4065 (10.32) TYP

.296 (7.51) TYP

.050 (1.27) TYP

.045 (1.14) TYP

.016 (.41)TYP

PIN #1 ID

.050 (1.27) TYP

28 SOIC

300 MIL .704 (17.88) TYP

7 deg. TYP

.099 (2.51) TYP

Spin

Semiconductor

www.spinsemi.com SPN1001-DS-170829 – 29 August 2017

Spin

Semiconductor

FV-1 Reverb IC

Featuring Spin Semiconductor Virtual Analog Technology

Notice

Spin Semiconductor reserves the right to make changes to, or to discontinue availability of, any product or service without

notice.

Spin Semiconductor assumes no liability for applications assistance or customer product design. Customers are

responsible for their products and applications using any Spin Semiconductor product or service. To minimize the risks

associated with customer products or applications, customers should provide adequate design and operating safeguards.

Spin Semiconductor make no warranty, expressed or implied, of the fitness of any product or service for any particular

application.

Contact Information

Spin Semiconductor

Phone: (310) 417-4956

Web: www.spinsemi.com

© 2017 Spin Semiconductor

All Rights Reserved

Spin

Semiconductor

www.spinsemi.com SPN1001-DS-170829 – 29 August 2017

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (843)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5808)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Phase Shift in TransformersDocument23 pagesPhase Shift in Transformersraza239No ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (346)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- How To Select MCB MCCBDocument4 pagesHow To Select MCB MCCBguddu1348150% (2)

- Quality Manager or Quality EngineerDocument3 pagesQuality Manager or Quality Engineerapi-77217896No ratings yet

- SMD Code BookDocument111 pagesSMD Code BookEnzo Auditore50% (2)

- Back EMF Detection Method For Sensorless Brushless DCDocument91 pagesBack EMF Detection Method For Sensorless Brushless DCnicoletabytaxNo ratings yet

- Peavey Classic VTDocument4 pagesPeavey Classic VTAlvise D'EsteNo ratings yet

- ZTX 753Document3 pagesZTX 753Alvise D'EsteNo ratings yet

- AD100VT Service ManualDocument7 pagesAD100VT Service ManualKyleRBNo ratings yet

- ELECTRONICS Multiple Choice QuestionsDocument182 pagesELECTRONICS Multiple Choice Questionsangelo_lopez1993No ratings yet

- Shindengen: Stepping Motor Driver IcsDocument2 pagesShindengen: Stepping Motor Driver IcsEngin UzunNo ratings yet

- SM572 190 210WDocument2 pagesSM572 190 210Wwalter_lopezvNo ratings yet

- LC700 User's Guide: Maintenance and Operation ManualDocument192 pagesLC700 User's Guide: Maintenance and Operation Manualsuhai miNo ratings yet

- Puente Gbu6aDocument4 pagesPuente Gbu6aJESSAMYN GUERRERO MONTOYANo ratings yet

- Module 4 PDFDocument20 pagesModule 4 PDFDheemanth DNo ratings yet

- Research On Copper Electroplating Technology For High Density TSV FillingDocument3 pagesResearch On Copper Electroplating Technology For High Density TSV FillingIvan HuNo ratings yet

- LCD Screens ExplainedDocument6 pagesLCD Screens ExplaineddimitrijeilicNo ratings yet

- Cmosedu Com Jbaker Courses Ee421L f13 Students Wolvert9 LabDocument15 pagesCmosedu Com Jbaker Courses Ee421L f13 Students Wolvert9 LabPerumal NamasivayamNo ratings yet

- Network TheoremsDocument5 pagesNetwork TheoremsSandeep SarmahNo ratings yet

- High Voltage EngineeringDocument37 pagesHigh Voltage EngineeringMihaelaNo ratings yet

- Results in Physics: K. Miura, T. Osawa, T. Suzuki, Y. Yokota, O. HanaizumiDocument2 pagesResults in Physics: K. Miura, T. Osawa, T. Suzuki, Y. Yokota, O. HanaizumiSarlita NugrahaNo ratings yet

- Varistors Based in The ZnO-Bi2O3 System, Microstructure Control and PropertiesDocument6 pagesVaristors Based in The ZnO-Bi2O3 System, Microstructure Control and PropertiesJanja TothNo ratings yet

- Pfisterer Cat.Document80 pagesPfisterer Cat.drsh81100% (1)

- ECE105 SyllabusDocument6 pagesECE105 SyllabusNamer NoNo ratings yet

- Neuro Controlled Seven Level Shunt Active Power Filter For Power Quality EnhancementDocument9 pagesNeuro Controlled Seven Level Shunt Active Power Filter For Power Quality EnhancementInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- EDC Unit I 2 MarksDocument4 pagesEDC Unit I 2 MarksmuthaiNo ratings yet

- BF2030 Data SheetsDocument11 pagesBF2030 Data SheetstarpinoNo ratings yet

- A Very Low-Power CMOS Mixed-SignalDocument10 pagesA Very Low-Power CMOS Mixed-SignalKarim H. MohamedNo ratings yet

- Aircraft DisplaysDocument87 pagesAircraft DisplaysDinesh CNo ratings yet

- Metrosil Current Transformer Protection Units: June 2013 Page 1 of 3Document3 pagesMetrosil Current Transformer Protection Units: June 2013 Page 1 of 3Stephen Bridges100% (1)

- ECE18R171 Electronic Devices ECE18R171 Electronic Devices: Course Objective(s)Document2 pagesECE18R171 Electronic Devices ECE18R171 Electronic Devices: Course Objective(s)Jeya Prakash KNo ratings yet

- High Voltage EngineeringDocument2 pagesHigh Voltage EngineeringNandan Gowda0% (1)

- Discipline Build GuideDocument12 pagesDiscipline Build Guidekatherine bellmanNo ratings yet

- Heartbreaker OD BuildDocument4 pagesHeartbreaker OD Buildsaul palafoxNo ratings yet

- Microwave SLC'S: General InformationDocument2 pagesMicrowave SLC'S: General InformationrolandseNo ratings yet