Professional Documents

Culture Documents

VLSI Project

Uploaded by

Amira GalalOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI Project

Uploaded by

Amira GalalCopyright:

Available Formats

CAIRO UNIVERSITY Elective Course :VLSI Design

FACULTY OF ENGINEERING Dr. Serag Eldin Habib

Electronics and Communications. DEPT., Fouth Year, Fall 2006

Final Project

________________________________________________________________

Introduction :

In Prob. Set 2 of this course, you developed a library of primitive gates using the

standard cell layout approach. This cell library is based on the scalable N well

CMOS process. This library is hence fourth named CUSCLIB1 ( Cairo

University Standard Cell LIBrary 1). The aim of the final project of the course is

to further use this standard cell library. Each student shall:

Use his/her cell together with CUSCLIB1 cells to build a circuit of his/her

choice (hence named Mycircuit) using the standard cell approach. The

number of cells used in Mycircuit should be at least four cells.

Project Inputs

CUSCLIB1 cell library

N well process description and design rules

Standard cell specifications

The standard cells should satisfy the same guidelines given in Prob. Set 2.

These guidelines are duplicated below for ease of reference. :

i ) Cell height 40 λ

ii ) VDD runs on a 5λ strip of Metal 1 located at height 34.5 λ to 39.5 λ

iii ) GND runs on a 5λ strip of Metal 1 located at height 0.5 λ to 5.5 λ

iv ) Inputs and outputs of each cell are available via vertical Metal 2

wires as shown in Fig. 1

Strict adherence to these guidelines should be observed. Any deviation

from these rules would simply lead to the rejection of your design.

VDD

I/O ports GND

for cell

Fig. 1

Project Outputs Each student should submit a report organized as follows :

1. Abstract

2. One page summary of Mycell specifications. These specifications include

Truth Table, Symbol, Pin Capacitance, cell area, power dissipation, and

delays. This specification should take the format given below.

3. Block diagram of Mycircuit showing how the Mycell and the other used

standard cells are connected.

4. CIF file that builds Mycircuit layout by instantating the CIF files of the

standard cells used Mycircuit.

5. One page summary of Mycircuit specifications. These specifications are

similar to Mycell specifications.

6. SPICE simulation of Mycircuit.

The output of this project should be submitted to Eng. Mohammed Khairy in

Electronic form no later than Thursday Feb 15, 2007.

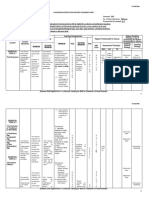

Template for Mycell specification

Asssume VDD = 3.3, and Cload = 150 fF

Cell Name

Truth Table Symbol Pin Capacitance

A B C F Pin Cap[pf]

A

B

C

Size µm2

Static power dissipation µWatt/ MHz

Propagation delays

Rise Fall

LH transition HL transition

Input Slope [ns] 0.05 2 0.05 2

Delay A =>F

Delay B=>F

Delay C =>F

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Question of Autonomy in ArchitectureDocument9 pagesThe Question of Autonomy in ArchitecturehnqueNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hybrid Structures PDFDocument3 pagesHybrid Structures PDFEmanuel FelisbertoNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Design Principles For Usability in The JAS 39 GripenDocument87 pagesDesign Principles For Usability in The JAS 39 GripenLeiser HartbeckNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- ACE REVIEWED - Submittal - TAS Concrete - Concrete Column Reinforcement - Shop Drawings - Reviewed PDFDocument5 pagesACE REVIEWED - Submittal - TAS Concrete - Concrete Column Reinforcement - Shop Drawings - Reviewed PDFTyler StoneNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- 1-EFL/ ESL Teaching and Learning Materials EvaluationDocument23 pages1-EFL/ ESL Teaching and Learning Materials EvaluationsoumiaNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Robust Design: Experiments For Better Products: Product Design and DevelopmentDocument31 pagesRobust Design: Experiments For Better Products: Product Design and DevelopmentAbdulaziz Bin AbdulrahmanNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Sai Final Project Team1Document67 pagesSai Final Project Team1Nagireddy KalluriNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- COBIM - S3 - Architectural - Design - v1Document27 pagesCOBIM - S3 - Architectural - Design - v1UkashaRaufNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Textile Influence:: Exploring The Role of Textiles in The Product Design ProcessDocument103 pagesTextile Influence:: Exploring The Role of Textiles in The Product Design ProcessJordan SmithNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Hannes Meyer Claude Schnaidt PDFDocument52 pagesHannes Meyer Claude Schnaidt PDFnisivocciaNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Data ProjectDocument16 pagesData ProjectamyNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Adigrat University Final Report NWDocument45 pagesAdigrat University Final Report NWlutaNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Eapp CidamsDocument13 pagesEapp CidamsMargielyn AguilandoNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- UX RefDocument3 pagesUX RefkratosNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Product and Service DesignDocument48 pagesProduct and Service Designbugzmio0% (1)

- Capability Based Planning PDFDocument65 pagesCapability Based Planning PDFdante981No ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Empowerment Technologies Contextualized Online Search and Research Skills / Developing Ict Content For Specific PurposesDocument3 pagesEmpowerment Technologies Contextualized Online Search and Research Skills / Developing Ict Content For Specific PurposesHannah MajadoNo ratings yet

- A Holistic Approach To Ship Design Volume 1 Optimisation of Ship Design and Operation For Life CycleDocument501 pagesA Holistic Approach To Ship Design Volume 1 Optimisation of Ship Design and Operation For Life CycleJejo TumambingNo ratings yet

- Top Ten Problems in Siebel Projects and How To Avoid ThemDocument4 pagesTop Ten Problems in Siebel Projects and How To Avoid Themapi-19477595No ratings yet

- Laptop Holder ReportDocument38 pagesLaptop Holder ReportZumuruDa Al HashliNo ratings yet

- Online FDP On VLSI SoC Design From 06th - 10th May, 2020Document2 pagesOnline FDP On VLSI SoC Design From 06th - 10th May, 2020devendiran3No ratings yet

- Datos FacebookDocument33 pagesDatos FacebookAgustina CabralNo ratings yet

- Client ListDocument89 pagesClient ListYogesh WadhwaNo ratings yet

- 50 Top Design Engineering Software Tools and Apps - PannamDocument43 pages50 Top Design Engineering Software Tools and Apps - PannamAgniva DuttaNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Elements PDFDocument1 pageElements PDFRene HasoonNo ratings yet

- Group Number Group Category Group Coordinator Module Code Name/Duration Module Coordinator/department Credit Details L T P CDocument2 pagesGroup Number Group Category Group Coordinator Module Code Name/Duration Module Coordinator/department Credit Details L T P CKalai ArasanNo ratings yet

- Handshake Brand Guidelines University ToolkitDocument14 pagesHandshake Brand Guidelines University Toolkitnaveed khan100% (1)

- Parametric Modeling A Simple ToolDocument6 pagesParametric Modeling A Simple ToolFatimeh ShahinNo ratings yet

- Semet CatalogoDocument436 pagesSemet CatalogoCesar Bedoya YustyNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- 2 - Estimation of General Characteristics of Fishing Vessels ADocument16 pages2 - Estimation of General Characteristics of Fishing Vessels AJuan SilvaNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)