Professional Documents

Culture Documents

DSS-1 Service Manual PDF

DSS-1 Service Manual PDF

Uploaded by

jbwilts0 ratings0% found this document useful (0 votes)

140 views74 pagesOriginal Title

DSS-1_SERVICE_MANUAL.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

140 views74 pagesDSS-1 Service Manual PDF

DSS-1 Service Manual PDF

Uploaded by

jbwiltsCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 74

MEGA,

DIGITAL SAMPLING SYNTHESIZER

SERVICE MANUAL

CONTENTS

29, SYSTEM EXPLANATION.

10. MAIN CIRCUIT EXPLANATION

11. CHECK AND ADJUSTMENT

ai SPECIFICATIONS...

2. ERROR MESSAGES.

pea BAU)

© KEYBOARD:

‘© CONTROLLERS:

© CONFIGURATION:

© SOUND SOURCES:

‘© NUMBER OF SOUND SOURCES:

© EFFECTS:

© NUMBER OF PROGRAMS:

‘© BUILT-IN DISK DRIVE:

‘© SUPPLIED ACCESSORIES:

‘© DIMENSIONS:

© WEIGHT:

‘© OPTIONS:

C~C 61 Keys, Velocity, After Touch

Joystick (X Asix: OSC/VCF FC Bend, + Axis: OSC Modulation,

=Y Axis: VCF Modulation), Program Up Jack, Sustain Damper

Jack

'8 Voices, 16 Oscillators, (2 Oscillators per Voice), 8 VCF

Modules, 8 VCA Modules

Waveforms Obtained by Sampling, 128 Harmonic Synthesis, or

“Drawing” can be edited, assigned to sections of the keyboard

and looped. 12-bit quantization. Sampling Frequencies and

Times: 16KH2, 16s, 24KHz, 118, 32KHz, 8s, 48KHz, 5.55 (can be

used together as one sound source), Number of Keyboard Split

Points: Up to 16

Up to 16 in internal wave RAM, Up to 120 per Disk

Digital Delay x2, Equalizer HIGH & LOW (All Programmable)

32 in memory, 128 on disk

Takes 3.5-inch, Double Sided, Double Density (1MB unformatted)

Floppy Disks, 770K PCM Data Storage Capacity per Disk

Floppy Disks x4, AC Power Cord

1171 (W) x 436 (0) x 123 (H) mm

18.5kg

PS-1 PEDAL SWITCH, PS-2 PEDAL SWITCH, TWC-030 TWIN

CABLE (3m), DS-1 DAMPER SWITCH, KH-1000 DYNAMIC

STEREO HEADPHONES, HC-DSS HARD CASE, MIDI CABLE

(7m/10m/12m), MF-2DD MICRO FLOPPY DISKS, SOUND.

PROGRAM LIBRARY

2. ERROR MESSAGES

Wessage Weaning Message Weaning

be ns Raat? ; no mswos | Theeaeme mations te en. oter

stira”| Ramin tnt iv, ttt ens | were: he sso hat ott td

cance

79 SOUNOE | There ata Sole sud one

The dk ne ve tas pot nn tomate or

JUNFORMATED/| the DSS-1. You must format the disk in the NOMSNDS | There is not a single muttsound on the disk.

OSS ederto wet ms ove poaaeg | weenie aparece

7 | Fema, se, and dee cons cn a be | toot nto tk

baal ‘carried out because the disk’s write protect tab

‘Sin the protector wt sable (ead ony) pos

tion, Reset the tab to the wite enable (ead/

wi) positon. Then try aga

PROTECTED!

(SOFT)

The disks eto the write protect made, so you

an not perform save or delete operations. Use

7 oe eamacnrene ro] et fae

vrmoe wp = es ronan eass ro] oO 3 ferwcmm

per conan wai] = 3 a oc wea reco] = oa

er eurrr om) 6 5 wim] facwearnea nil = oa

— JO0L-1 Tae oran| “6 9~S00,NOTE 3)

vor resowwoe rm] * . oa x00 =

|VoF KBOTRAGK —(F33)| 2 ’ o~ 68 Joo. FEEDaacK (Fe2)| “ ons

horworrwwoeviran) no oo reo eva | a = a

ferwooetay rao) « oa Fa enenortto|e a oe

herseeroem roo] ® serena] s

fer coaraoe em) a a reer 0] =

fer eooeowr — 8) ‘tow a

Joos me orm) se

fer eomeacro 5) oo =

[vor ecs.oPe (Fs) 6 * JOOL2 FEEDBACK (F32)| 2 ss

lercoumn em) 7 Freon "0] =

[Vor eoneLease (rs) = POE wrens), 7

i * Ps noe] 6

[von Tom EVEL Fan] 20 = POS went sw] #

[woa EG-arTAGK (F38)) 2 a [0801 MA SOUND Ma. (2) se oo

von cooecar a0) = lcrmanavon en] a esse

fescooexron on) a a [asa sooner « @ | e-wooree

von eoaioe ran] ™ ‘wo woor sw re] er @ ae

veaconisan on) = oaresouron v0] et «| ebm

1633

oa cone.ense oan] x rae

a Stosca

Ener] @ ieee

lor curorr (Fe2)| a oe osc cower] ny sue

Fe acco] = = ff

eres occur | » losozccmwe ri wt = 68)

Pea | > »t | is

eoteven C40] __ = lesoeoctme rin] = oe

ees cz) 2 3 se

Ti ara ese renal] = en

es tras] ™ *

Ti ocom { sow seuecr rm) @ | torn

FSS se ro] =I en

eteen eo!» [= sone

EAS morn "| __ > 7 oe eso verneauenvirin| we 7

as rotate (301) Es ae =. [056 moanTENsiTY (17) a ”

ee nazienser "torn

ProssaapanaMcreR | (wore!) | wworen) | (OECMAL)

foscmooetar Frnt ®

[aura weno seuecr rie)] 11 3

a ™

[auTo score inf 13 5

lumsowoenne ors 6

Bowmore] 7 7

[key assion wove ren] 6 © ‘owpour2)

eoty 0)

UNO

lowsow voces ren] 17 7 om

t

2

[0

Note:

|” Parameter No. Parameter number used for program parameter cheng.

lst: Bye oftat wit program parameter dump.

[Numbers within parentheses are parameter numbers used when esting

‘wahin th 085-1

12 Must be tat fr botn oscars so that OSCT + OSC2 = 100,

8, DOL TIME Format

won To Telelel[ele[wlw

44 Tea MAX BEND RANGE values mtd othe range of O10 12, drve by

subuacting rom 12 the larger MAK INTERVAL value of to rutlounas

sssgnedte OSC1 and OSCE Tus must be eet there lem change the

tmattound MAX WTERVAL.

Fa

n

=

Ps]

i—

o

+

ce

=]

P=

-

=

>

cg)

=]

P=

4

z

uy

ad

(or)

oO

4

4

inal

ir)

at

oS

==)

og

_

cP)

==]

Pd

EJ

ws) C 1

ea He ~ WE

Be a

aonb 4 a

on.1 | xim-o36 | rower sw [on 12] xum7ez | Kum760 | cn,

on, 2 | kum-toae | ac socxeT | GN, 13 | Kim-7a0 | KLm7e2 on,

23] Kuw7er | KBD (GLY) [oN,o+] KUM7es | KLN-I050 ON, 48 | KuNeio¥o | KBD

24) Kure: | KBD(OR) Jon, 35 | KuM-7e4 | KLM-1050 | ON, 46 | KLM-1019 | LOD

25| xum7er | KBD (6) [cn 96 | KuM7es | Kum-7ae —|CN, 47 | KLM7e2 | KLMAO16

2%

2

ons | kune-ro36 | P.1 on, 14] kume7as | Km7e2 | CN,

on.¢ | kuneves | Kure [on.15 | kum7aa | Kum7e2 cn, 26| xiatver | KuM706 [cn 97 | KuM7ea | Kv-7e4 [ON 48 | KLMe7e2 | KLMAO16

con,s | KuM-7e0 | Lcd BOARD | CN. 16 | Kum7er | KLMm7e2 © |.cn.27| KUn—1 | JovsTIC on, 36 | KuM7es | KLw7e5 CN, 49 | KLM-7e2 | KLM-I016

on,6 | Kuneveo | xuwras [oN 17 | xunerea | Kumore: on. 20| Kumar | KuM7e¢ [cn 20 | umes | KLmio12 [CN 50 | Kure | KLMAO16

cn, 7 | Kinere0 | xumeres | ON, 18 | Kune7es | Kum-1061 | CN, 29 | KLm7e1 | KuM-1050 Jon, 40| KuM-7es | KLMi013 |cN, 51 | KLM-t061 | KUM783

cn.e | kunerer | xumera0 [oN 19 | xun-7ea | Kum7se oN, 20| Kemer | KuM-to49 Jon, 41 | xuneras | KLmi012 |cN, 52 | KLM-061 | KLM-783

con.o | Kuw-780 | Foo CN, 20 | xum-7es | KLm7es |GN.31 | Kum7e1 | KuM-1050 [N, 42 | KUM-796. | FOO en. 53 | kunetoes | KLM-782

oN, 10 Kun-7e0 | xumree —|CN,21 | Kine | xum7es cn. 32 | Kum-7es | KLw-1050 [N43 | KuM-7e6 | KLM-1014

cn.t1 | Kum-7eo | xum7e2 CN, 22| Kim7es | Kum7e1 [cn 93 | Kum7es | KLM-1050 |.ON, 44 | KLM-726 | KLMASO14

e

>

wo

oo

=

i)

Es

=

>

2

Es)

>

=

KLM-780,

7. CIRCUIT DIAGRAM

KLM-781

‘KLM-782,

4

ne fener

Ib RES

4

a

a

a

cot

KLM-783 (OLD)

3 KLM-783 (NEW)

ier]

encey ru) avassvssgenee Ce KuM-783 Vora

, se

reg, te 3":

1020 3:

KLM-7a1_cov2

ac i 3:

TSS:

= KLM-782 TG

vet veer sas :

y ; oo

oO i mor 1 KUM~784 PANEL,

wove cal | ———— oo

— BS

“ . me

oun, rye ge ECW $08 cpu

ae easeet

ma:

er, fn Foo

ws + cS

100r _|200v he oe

FStlasven scores a ora

a wef oe HB

aa |sorti ea seuh eo fs

et

KLM-1061

g2a

SESSS5355 a595555

eRe BS

Phat as

pcsone ne So 68 Se oe

8 KEYBOARD MATRIX

3

ase T23838 ewe: 88

KLM-784. 785. 788. 1012. 1013

ests

eo

a ies

= oes!

4:

oe

a ates

KLM-1036 Power sw

D0-val

oe

“is

AC = 3-

Bee ig 5-9 vo masromuer

‘KLM-1049

— er

ne Ms224P

24

CAR AP UN)

KLM-783

KLM-781

a

KLM-1049

KLM-780

==) ana as

See Ne

a, iH Z| WARS — x ;

cam iE al sae

———]

rere!

jaecea as

KP AB82\ sous \so1s

9. SYSTEM EXPLANATION

1. CPU SYSTEM

‘The DSS-" digital sampling synthesizer has 8 voices (16

oscillators), all functions are controlled by software.

A dual CPU system is employed. The division of labor

between the CPU is as follows.

(© CPU 1 (085A-2, KLM-780) © CPU 2 (63B03X, KLM-761)

1,LCD and LED indicators 1. KEY scan, KEY assign,

2. Panel switch input processing 2. MIDI processing

3. FDD control ‘3. VCFIVCA control

4. Tone generator processing 4. DDL control

5 Interface with CPU 2 ‘5. Foot switch input processing

6: interface with CPU 1

‘The followings are examples of the division of labor in

specific operations.

Sound data processing

Sound data such as waveform data and VCFA data

are all stored on a floppy disk (FD). CPU 1 supervises

this storage operation. In addition, waveform data are

transferred to a DRAM under the supervision of CPU

1. VCFA data are transferred to CPU 2.

{KEY input processing

CPU 2 does KEY scanning and KEY assigning.

Whenever KEY goes ON or OFF, CPU 2 performs

VCFA ONIOFF processing, and, at the same time,

output to MIDI is performed. Data are also transferred

to CPU 1, and CPU 1 performs TG ON processing,

IEPITCH BEND, MASTER TUNE processing

CPU 2 performs A/D conversion of CV from the

bender and TUNE VA. If there is a change, the

changed values are transferred to CPU 1, CPU 1 ac-

cesses TG and the musical interval is changed ac-

cordingly.

2. Explanation of custom LSI

In the DSS-1, since it is necessary to transfer a large

quantity of data at high speed, the DMA (DIRECT

MEMORY ACCESS) system is adopted. In this system,

data are transferred directly between VO and memory

without going through the CPU registers. The LSis

developed for this purpose are the custom GATE AR-

RAY uPD650306-043 (GA) and .PD65040G-099 (GA-

11). The GAd receives DMA requests on 16 channels

(maximum of 24 channels), encodes them and gener-

ates timing. The GAdI stores 8 channels worth of

3. FDD (FLOPPY DISK DRIVE)

A FDD (M0350) is used to READ/WRITE sound

parameter data on an FD (3.5-inch FLOPPY DISK).

The basic mechanical movement in the FDD is that

when the DISK rotates the HEAD moves in the radial

direction. It is made up of a great many mechanical

parts

2

Panel switch input processing; LCD And LED in-

dications

CPU 1 performs a switch scan and gives the

necessary LCD and LED indications.

DATA ENTRY A, B potentiometer value inputs

CPU 2 performs AD conversion of CV and then

changes values as necessary. The changed values

are transferred to CPU 1 and then processed by CPU

1

Hf a cutoff is edited in PROGRAM/PARAMETER

mode, when DATA ENTRY B is moved CPU 2 trans-

{ers that value to CPU 1 and the processing is per-

formed by CPU 1. Then the value is transferred back

to CPU 2, and CPU 2 changes the VCF CUTOFF CV.

Sampling

The length of the sampling frequency is controlled by

CPU 1. Sampling start trigger level data are then

transferred to CPU 2, and CPU 2 controls the CV in

accordance with those data.

Hand drawing

‘After hand drawing is started, CPU 2 performs A/D

conversion of DATA ENTRY A data every 16 ms. The

resulting values are transferred to CPU 1. CPU 1

stores those values in the RAM. When 512 values

have been transferred, the operation terminates.

CPU 1 produces 8 waveforms (for 8 octaves) from

those data and transfers them to the DRAM.

Sine synthesis

CPU 1 performs the synthesis based on the sine

table in the EPROM, produces 8 waveforms (for 8

octaves) and transfers them to the DRAM.

generates timing. The GALI stores 8 channels worth of

memory addresses, increments addresses in response

to requests and outputs in accordance with the GA

timing,

In the DSS-1, two GAMIs are needed for each GA to

cover 16 channels.

Caution

Both the GA and GAdI use 80-pin flat packages.

Use caution in repair and replacement.

‘Special jigs developed by the manufacturer are needed

for repair and adjustment, so repair by anyone other

than the manufacturer is impossible. Consequently,

complete units must be replaced.

Judge whether an FDD is malfunctioning by swapping

4. CPU 1 MEMORY MAP

wri

EP-ROM 27256 (BANK EP-ROM 27256 (BANK 1)

m a a

Co ame Tine Wo bin ies Za Sc

eng Basen coe

feet ah

a Sagan a

ane, za

— oan

ms ene

of, any

oe || re |

RE [eae

ea a

BANK SWITCH PORT HC74 GATE ARRAY TI (1)

wr aman

al = al par

BR, rane

ows real

eae Ci aT EO PRT

ae nT

7 oe =

i A aE eno Pon wa

ae aT

oe von

=a evened

= ry rer

= fae

eae ers ST oat

oe au

a fa

oar 8, ees

ie

[DMA RAM LOW BYTE WRITE PORT HC374| EO00H RAM 4364

mee = ones

bi ama es wae ont

nea

MCPU1 PROGRAM ROM MAP

Ta56 BANK or ean

0000 CPU UF CPUIF 0000 CPU LF ‘CPUIF

0520 | TG JUMP TABLE 0520 | Ta 6

rane

0570 DMA ADDRESS SET 1920 DOS + FOD UTILITY FDOS:

‘0500 HARMONICS TABLES HTBL 3890 MIDI EX Ex

0680 EDITOR MAIN & SUB MAIN 45B5 ‘NOT USED (4BH)

_ iaooj mivesT Mone TeSTnODE

48E0 EDITOR SUB ‘sus

Pinion

ral =

8000 | BANK CHANGE ROUTINES BNKSW

8053 | VERSION No. DISPLAY ver

8070 | EDITOR UTILITIES DUTL

on

(EDSS-1 SOFTWARE DOCUMENT

CPU-1 MEMORY MAP AND COMMON USE VCE VCA EF SELECT

WORKING AREA a

(RAM MEMORY MAP 765210

‘ADDRESS: CONTENTS port2 ]@ 0 0 — — —|VOrFc 1-8

TG Controlr Work Area oost |g 1 1 — — —|war-s

DOS Wo, Awe 10-1 0 0 0| oourmoocv

ity Work rea

‘Arron Aver | OPU- ial Work Aros 10 1 0 0 1] opzMmo0 cv

CPU-1== CPU interlace Work Ava

azeot- aren | EOD Test Work Area eee el sees

‘Aa0oH = AGorH | FDOS Work Area 40 4 0 4 1| SAMPL START TAG CY

‘S10 -esor | Program Parameter

Common Use Work Area 101 1 0 0} KOBE

Editor Wor Area (1) 40 4 1 0 1| RESONANCE

tio xcs eco Work Aes 40444 often

tor Wore Ava (2) so44 4 tf uve

00 Data But

FaroH-FcerH | Estor Work Area (3)

Foron-Frern | Stack Area

FFFOH-FFFFH | Spare mead SELECT etc.

Tos4a2ie

ECPU ROM MAP PoRT 6 = > + | AD SELECT

conon aaa corm © 0 0) BenoeR

INTERNAL ANTAL

REGISTER oo 1|mc

Port eat 01 0 TUNE

ore a 011] DATA ENTRY A

a 10. 0| para enrny 8

0408

INTERNAL — 10 1] NOP

RAN 11 0| AFTER ToucH

one a 414] INPUT SiG LEVEL

rE . VF MODE tabi)

00H .

aaa com SERIAL GLX

DOL CONTROL . SERIAL DATA

ie~7 mo . SERIAL £0 STB

ce oe eae . ‘SERIAL ODL 1

200K ry ‘SERIAL LEVEL ST8

Dac 4— tt ooo

3008 mot beac

cpus vo soon ane

ou bt

a Tes4s2re

00H «| pou MUTE

taps . DELI TIME STB

Hots 18 . Lz LEVEL STB

eae : Lz TME STB

ons 17 wees AG bit o~3

0H

0004

RAM

aK ics

ore

con0t

EP ROM

16K 1615

ern

5. TEST program Explanation

(MOUTLINE OF DSS-1 INTERNAL INSPECTION MODE

The inspection program given below is stored in the

DSS-1 system ROM. When the power switch is switched

{rom OFF to ON while pressing both the DATA ENTRY A

section UP and DOWN keys (4 V) simultaneously, the

‘TEST MODE is activated. In this mode, the system runs

in the following sequence, and inspection is carried out.

Software: version indication and date indication

FO function test

WeRAM test

Panel switch confmation

itis convenient for one FD to be set aside to be used ex-

clusively for FDO tests.

(Caution) For FDD tests, use one that has already been

formatted. Also, when an FDD testis run, all of the data,

are erased,

Note 1

Afler entering “SYSTEM MODE”, everything is in

normal status except for the following conditions:

[MASTER TUNE, PITCH BENDER, AUTO BEND, and PITCH

MODULATION ae inetetve,

VOICE NO. dta ae output to MDL-OUT.

VOICE NO is inated on LCD in PLAY MODE

Note 2, MIDI

MIDI is “90", “3C" and “40” note-on data signals.

Every time the voice changes from 1 to 8, conversion.

to the following data is performed (the lower 4 digits of

the status change).

WOE 30,30, @

2 voKE 31,30,

‘3 vOICe %, 30,

‘4VOKE 300

‘5 Voce Ce

‘6 YOKE 5,90, 40

T VOICE 1%, %,

‘8 voKe 9.00

38

INTEST PROGRAM CHART

WORDS =

SAMPLING SYNTHESCZER]

T

ee

Ver 86,9

1

= TEST MONE *

00 TEST? (yt)

= TEST MODE “==

WRAKY CHECK OK 00

TEST MODE ***

ERROR LOW: 000mm

T

*** TEST MODE ***

a

aresr anne

ERROR HGH: monn

READ ERROR (rn),

FOO TEST” (yn)

‘SEEK ERROR (ona)

FDO TEST? (yn)

“= TEST MODE “==

RAM CHECK? (yn)

t

7 Probe suey cs

Pres Coen gu | MOS coed on

‘(MTEST MODE EXPLANATION

1. Turn power ON (of course while simultaneously

pressing section A data entry switches 4s a) and

select the DSS-1 internal inspection mode.

Note:

Hf this indication appears, you can assume that CPU

‘1 and the LCD are operating normally.

2. One to two seconds later an indication that the test

‘mode has been entered appears. The internal ROM

version No. and the creation data are indicated

simultaneously.

“Note:

Hf there are problems on the TG circuit board, the

system does not proceed to the TEST MODE indica-

tion.

3. Use the cursor (Y/N) to select whether or not the

floppy disk drive is to be inspected. If NO, proceed

to step 12.

‘4, Cursor (YIN) key judgment

5. Insert a previously formatted medium and ask the

‘system whether itis ll right to write in (save) test

data for that medium. This is also selected by the

‘cursor (Y/N).

6. Cursor (VIN) key judgement

7. Save test data for the m

(while weitng in).

9. Errors: “refer to S-1”

10. From the results of reading and writing the test data

for the medium, an indication that the FDD is normal

is given. Asks’ whether it is necessary to try one

more time.

mS-1” FDD ERROR MESSAGES

11, Cursor (YIN) key judgment

12, Asks whether to perform a TG (KLM-782) WAVE

RAM check.

19. Cursor (Y/N) key judgment

14, The data 0000 0000 00008 are written in to the

12-bit WAVE RAM on the TG circuit board 1 bit at a

time; if the writing can be done until the last ad-

dress, the fact that they are 0000 0000 00008 is,

read in.

18. The data 1111 1111 1111B are written in to the

12-bit WAVE RAM on the TG circuit board 1 bit at a

time; if the writing is completed to the last address,

then the fact that they are 1111 1111 1111B is read

21. Each write/read operation is performed, and the fact

that the WAVE RAM is normal is indicated.

22. Check whether or not the “DELICANCEL" works.

It it doesn't work when pressed (system does

‘ot proceed to the next step) then the switch is bad.

24, Similarly, check whether the “COMPARE” switch

works.

26. The checks in the internal inspection mode shall be

1 | DRIVE NOT READY! ‘There is no disk in the drive, or it is not in securely.

9-2 | UNFORMATED! ‘The disk is not formatted,

93 | PROTECTED! (HARD)! Wile orton ile oft The aka oh ho slo In ervert

9-4 | WRITE ERROR (O—OOH-D)!

‘A write-in error has occurred in the (C-OOH-0) section.

95 | READ ERROR (Q—OOH-()!

‘A readin error has occurred in the (C-COH-D) section.

96 | SEEK ERROR (Q—OOH-D)!

‘A head movement error has occurred in the (C- GOH-G)

section.

Not

(O—OOk-D) = (O—O0H-D)!

‘ ye CHT es arent

Cyinder address (00 to 4A)

Head number (001)

“$-2" WeRAM DATA ERROR INDICATIONS

‘% The IC number is classified as low or high (W=RAM on TS

circuit board)

‘© Assume that 00H (0000 0000 00008) has been writtan inthe

WeRRAM, and that one of the bits is no good.

Low =1c25 oH = 1c29 ad oe

leas te30 *** TEST MODE ***

teas ie ERROR LOW 000,011

cua 1 the Indication in Fg. 1 ap-

PS Serene 1% fm),

Fig. 2 *** TEST MODE ***

ERROR High 0170 9100

Stew te nga nF. 2

apne let a

ies

(MEXPLANATION OF VOICE NO. INDICATIONS

‘When the system is rising in TEST MODE, the VOICE

‘number is indicated on the LCD in “PLAY MODE”.

Example: When the VOICE No. is “1”

SYSA P01: TEST-1

VOICE No. 1

The VOICE numbers are 1 to 8. Every time the first gate

turns ON, the indication changes.

* When this function is being used, make sure that

system loading is not done by program change by the

MIDI

MIDI PGM CHANGE MODE to “OFF” or “MODE

)

If this is not done then the second digit of the LCD in-

ication will go off.

10. MAIN CIRCUIT EXPLANATION

1. KLM-780

‘The CPU employs an 8085A-2 (IC21) Bit micro-

computer; the system clock is 10 MHz. The clock output

is frequency divided by about 2 to give an output fre-

quency of about § MHz and input to the counter timer in-

ut terminal of 8185 (IC17). A 1.14 kHz rectangular

waveform is output from 8155 TIMER OUT (PIN 6), 50,

that interrupt processing is performed for musical scale

data sets for 8 voices, BEND processing, LFO period

etc. (Processing is done 9 times per period.)

‘The EPROM consists of two 32 KB ICs (IC18 and IC19)

and one 8 KB IC (IC12). The CPU memory space is a

maximum of 64 KB, so the HC74 (IC30) controls

‘changeover between the two 32 KB EPROMSs (IC18,

Ic19)

‘Two 8 KB RAMs (IC11 and C19) are used. These are

used for program parameter storage and working, and

{for multisound parameter storage and working.

‘An 8155 (IC17) and 8256 (IC14) are used for VO. The

functions of the ports are as follows.

PORTC! Input signal GAIN, ATT contol clock

output

PORTC2 inp signal GAIN, strobe output

PORT C3 TG A/D MODE SELECT signal output

PORT C4 PCM DATA TRANSFER MODE output

(CPU 1 — DRAM)

PORT CS PCM DATA TRANSFER MODE output

(CPU 1 — DRAM)

PORT C6 TG RESET

PORT C7 ‘Not used

LS139 (1028) and L138 ((C15) respectively have address.

‘decoder functions. 1C28 uses the two high-order address

bits A14 and A15, and selects the ROM and RAM chips.

C15 similarly uses the 3 bits A10 to A12, and outputs the

chipselection YO to Y7 for other chips.

‘The interface with TG (KLM-782) consists of IC8 (LS245),

C9 (18367) and 1C10 (L367).

1025 (LS374) and 1C26 (LS374) from a D TYPE FLIP-

FLOP, configuring 2 complete input/output systems to

ms155 the interface circuit with CPU 2 (KLM-781). In addition,

PORT AO~A7 LCD control data input/output port C32 (LS74) performs CPU interrupt control.

PORT 80~87 Pane LED contol signal cutput Since the FDD cannot be connecied diecy tothe CPU

PORT Co-G2_ LCD contro scien 0 bus, an FOC. (FLOPPY DRIVE CONTROLLER). is

7 contro signal output necessary nthe KLM-780 cult ciagram, [CB (;PO7BSA)

8255 corresponds to the FDC. Also, data read out from the disk

include bath CLOGK and DATA which must be separated

PORT A0-A7_ Panaonch DATAINPUT PORT A SEPRWATOR IT (SEDSNEOG sed ut

PORT B4~B7 TG WAVEFORM RESOLUTION Lenees

PORT CO Input signal GAIN, ATT contol data The principal functions are as flows, (The FOD contol

ouput signal output bythe FDC ts defined as OUT)

ele Signal name tan Function

8 INDEX IN Outputs 1 pulse every rotation of the FDO.

10 DRIVE SELECT 0 | out | “1” aie when teat accesses

2 DRIVE SELECT 1 | OUT | Worse ony comin)

16 MOTOR ON OUT | ven ("mito tes

18 DIRECTION IN OUT | "Us Feed moves rom oie tard cere of

20 STEP OUT | "1" pike fread mover

‘When ages fon “Hw 1" can ewan TRS SOTO

22 WRITE DATA out | Verte ster We Ga 6 a

When", READ ATA foci

24 WRITE GATE QUT | when “L"; WRITE DATA is tiecve

=U" (RAGE) wien ad sh eT Ta Oo Wl

26 TRACK 00 1 | teste heatpusten when pave med Ot. ‘

Togs 0 WATE PROTEC

28 WRITE PROTECT | ww | “wrt wre pnorecr eased an wien becomes posse

WATE PROTECT 6 tec. ad ten peed

30 READ DATA TN | POOR eatin

3 SIDE SELECT our |W: s0e 0" S0ET

= wn | TE I eed a iS roma We Der & Te

Y athervise. A"

39

2. KLM-781

KLM.781 is a CPU2 board.

‘The CPU2 is 8 bit Microcomputer HD63B03x (IC11) and

each port function is as follows.

‘Additionally Program ROM (IC16) is 16K byte, Work

RAM (IC14) is 8K byte.

(ECPU2 PORT FUNCTION

Port P20 GV, S/H Channel control Output Port

Port P21. GV, S/H Channel control Output Port

Port P22 GV, S/H Channel control Output Port,

Port P23. MIDI IN

Port P24 MIDI OUT

Port P25 CV, S/H INHIBIT 0 - 2 Output Port

Port P28 CV, SIH INHIBIT 0 - 2 Output Port

Port P27 CV, SIH INHIBIT 0 - 2 Output Port

Note:

INHIBITO VOF 0-7

INHIBIT1 VCA0-7

INHIBIT20 DDL CV

21 ccLacy

22 NOP

23 SAMPLE START

| 24 NOISE

| 25 RESONANCE

26 LEVEL2

27 LEVEL1

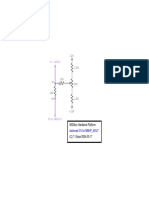

3. KLM-782

KLM.782 Is combined with the SAMPLE AND HOLD

(SIH) circuit board KLM-1061 to form the DSS-1 TONE

GENERATOR (TG) section. The block configuration is,

as shown in Fig. 1.

OUTLINE OF FUNCTIONS

1. Creation of DMA request clock in accordance with

‘command from CPU 1.

ICs 1,2, 3,6, 7 and 8 are CMOS programmable inter-

val timers which have 3 independent 16-bit counters

inside one chip. in combination with the custom gate

array 4PD85011C-023 (GA) (IC4, 5) predivider,

they form a 18-bit divider. The master clock is 32

MHz. TO to 17, which are produced from it, are rec-

tangular waveforms with approximately 50% duty

cycles. The frequencies of TO 10 T15 vary from 64 Hz

1064 kiiz depending on conditions and determine the

musical intervals.

T16 is the ADC system clock with a frequency of

about 500 kHz. T17 is a clock with a frequency of

about 31 kHz for refreshing DRAM.

0 and T1 are the EOC of ADC respectively. In com-

bination with CPU WRITE (Y7), CPU READ (¥14)

and the logic formed by IC58, 1C60, ICB1 and IC62,

become DREGO and DREGH signals only when

selected.

40

Port P54 PROGRAM UP (by FOOT SW) Input Port

Port P55. DAMPER (by FOOT SW) Input Port

Port P60 AID Input Channel control Output

Port P61 AID Input Channel control Output

Port P62. A/D Input Channel control Output

Port P63. VCF MODE (24dB/OCT, 12dB/0CT switch)

Port P64 SERIAL CONTROL CLOCK

Port P65 SERIAL CONTROL DATA

Port P66 EQ, DOL LEVEL STB

Port P67. DDL2 INPUT SELECT

By Keyboard Scan, lower address (AO - A3) 4 bit is

latched at C3 (HG77), and is decoded at 1C6, IC7

(HC138) and is output to Keyboard Matrix. IC6 is to out-

ut address forthe first contact, and IC7 is to output ad-

dress for the second contact.

Keyboard data, such as Note Data, key Velocity Data are

‘ead to CPU2 after through Octal Butfer HC240 (ICS).

CV for VCFIA (KLM-789) latches Data Bus DO - D7 at IC12

(4 bit) and 1C13 (8 bit) to control 12 bt DAC BAS221(IC16).

‘Also, Reference voltage (15V) at DAC is generated at

OP AMP 4558 (IG19).

Analog voltage of Slide VRs on the panel goes through

Multiplexer 4051 (IC 3) and is converted AID by CPU2.

(C4 is two-way Data Bus Buffer IC and constructs Interface

Circuit with CPU

Fig. 1

—

tooo

Sehre te

}

[tin bil L im

~T

2. Producing timing and addresses for the DRAM

(256 K bits x 12)

The above clocks TO to T15 are input from the GAT

DMA request clock input terminals DREQO to

DREQIS.

‘A 16-channel DMA request received by GAT is on-

‘coded by addresses used to specify 3 channels (CHO

to CH2) and three GALI chip select signals.

‘Channels 0 to 7 are processed by CSL1 and chan-

nels 8 to 15 by CSL2. CSL3 uses the IC15 NAND

the ROW address for refreshing. GALI processing is.

done by outputting an acknowledgment (ACK) cor-

responding to the DREQ channel on GAL timing,

specitying the address in memory by address infor-

mation, and incrementing the address (DMA AD-

DRESS CONTROL).

3, Transter of PCM DATA read out by the DMA from

the DRAM to CPU 1

PCM data are latched from CPU 1 to the DRAM by

the respective interface circuits listed below, then

connected to the data bus.

To the DAC, among the 12 bits from SDO to SD11 the

low-order 6 bits from SD0 to SO5 pass through the

logic HC 08 (IC17 and IC18) for resolution to be

latched, then are connected to the 12-bit DAC

BA9221 (IC37).

DIA resolution is for the purpose of controlling the

resolution of the reproduced sound and is controlled

by CPU 1 (panel switch parameter 16).

4, KLM-783

This circuit board consists of the DSS-1 VOF and VCA

sections, and equalizer and noise generator sections. Its

outline is as follows.

The VCFIVCA circuit employs 8 custom IC.

NJM20698Ds (IC101 to ICE01) and operates upon

receiving control voltage (CV) from CPU 2 (KLM-781),

ICMS201 (IC102 to 1C802) selects the VCF output format

with software, selects 12 JBIOCT or 24 dB/OCT and in-

puts VCF output to the 2069 VCA INPUT terminal.

Voice processing of the MULTIPLEX CVs from CPU 2 is.

performed by the following respective exclusive multi

plexers:

vor:

IC9 (4051) output voltage =5V; ICS and IC (M5224)

form the SIH.

5. KLM-786

This circuit board, which forms the power supply circut,

consists of the following.

1. Regulators 7805 (IC1) and 7908 (IC2)

this is a + 5V power supply used principally

for VOFA and DDL.

2, Regulators 7812 (IC3) and 7912 (IC4)

this is a + 12V power supply used mainly

for the operational amplifiers.

4, SAMPLE AND HOLD (S/H)

‘The DAC signal output type is converted from current

{ype to voltage type by OP AMP 5534 (C38).

‘This output contains a mixture of 16 channels, 50 S/H

is performed for each channel by the ACK signal pro-

duced by GAL the high-speed analogue switches

(HC4066) of IC41, 1644, IC47 and IC5O, and the

OP AMP.

Connectors CN49 and CNSO can observe wave-

forms; S/H is performed again by KLM-1061 and

noise is removed (the CLOCKs are 2 to T15 and

DRI).

5. Audio input signal contro!

The signal that is input for sampling from connector

CN15 enters the fer circuit (panel control by CPU 1)

with the GAIN and ATT determined by IC64.

This filter circuit is an LPF formed by operational

amplifiers IC87 and 1C88; the frequency is 20 kHz.

IC87 and IC70 form an absolute value circuit the out-

put of which is read into CPU 2 as an LCD level

meter.

1C5B and IC63 produce a trigger which starts sampl-

ing. The transition from “H” to “L" is observed at the

start of sampling by connector CN12A-9. While the

level is “H", GAT Dy to D, DATA are not read into

GA—I (GH).

1C54, IC55, IC58 and ICS7 form SAR (Successive Ap-

proximation Registers).

vea:

1C8 (4051) output voltage 0 to 10V; IC3 and IC4 (M5224)

form the SIH.

IMINOISE, RESONANCE

‘OSC MIX RATIO and s0 on for the other CVs: 1G7 (4051)

uapat voiage Oto OV; C1 and IC2 (M6224) form the

‘The VCA output for each voice is mixed by a mixer cir

cuit (1C15), enters the equalizer TC31S6P (IC16) con-

trolled by CPU 2; then equalizing processing is per-

formed and the result is output from OP AMP 4556

(C14).

The noise generator is formed by transistor 2802785

selected and OP AMP 4558 (IC12). The noise VCA cor-

responds to transistors Q1 and Q2, and operational

amplifier 4558 (IC13).

3, Regulators 7812 (IC5)

this is a +12V power supply used for the

FDD motor.

4. Power transistor 258533 (Q1)

this is a +5V 2.54 power supply used for

the digital system.

a

IESEMI-FIXED RESISTOR LOCATION DIAGRAM

DIGITAL DELAY BOARD KLM-1050

@vvi (+50 ADH

TPs (uD)

VF fo LEVEL ADI

‘OSCt LEVEL ADS

\VOF RESONANCE ADJ,

(NOISE LEVEL ADJ, Oseiloscope

Que

vee

VCF-A BOARD KLM-787 KL-1049

2

11. CHECK AND ADJUSTMENT PROCEDURE

(CAUTION

1. This product has been throughly adjusted at the fac-

tory before shipment. Thereore never turn any Semi-

Fixed VAs other than those required for repair. When

adjust Semi Fixed VRs, please refer to Semi-Fixed

VR Location Diagram.

2. After turning on Power, wait at least 15 minutes

before beginning test and adjustment.

Necessary equipments for the procedure are as

follows

© Oscilloscope @) Digital Volt Meter (DVM) @) Fre-

‘quency Counter @ Noise Meter

© Power Supply Voltage Check and Adjustment

(KLM-786)

1, Connect a Digital Voltmeter (DVM) to Connector CN4

1 pin (red wire) of KLM-786. (GND to GND on the

board)

2. Confirm if the DVM value is within +5V +0.2V

3, Adjust VAI if necessary.

Note:

‘As other Power Supplies + SV, + 12V are produced

by three terminal regulators, adjustment is not

necessary.

Deviation of the regulator is less than 20%.

DAC Power Supply Check and Adjustment

(KLM-781)

1. Connect a DVM to IC18 1 pin of CPU2 board

KLM-781. (GND to GND of the board)

2. Confirm if the DVM value is within +5V.+0.2V,

3. Adjust VAI if necessary.

© TG Board A/D Check and Adjustment (KLM-782)

1. Connect an oscilloscope (DC, 2Vidiv, Sysecidlv) to

‘TPS. (GND to TPA)

Note:

Probe is 10:

4, Press Enter Key

Fig. 3

F1 SMPL-NO. MEN DIV

01 01

5. Press No. 2 Key

Fig. 4

ATTN=00dB GAIN-00dB

6. Confirm waveform of Fig. 5.

7. Adjust VR 1 if necessary.

Fig. 5

Not synchronized with tig-

92" ofthe oscloscope.

Fig. 6

No coo

Synchronized with tigger ot

the osciloscope. Pulsewave-

fom from "H* to °L" is

observed.

Fig. 7 TTT

2. Press Sample Key. LED is lt and Display shows as

Fig. 1

Fig. 1

*** SAMPLE MODE ***

SELECT S.Frq = 32KHZ

3. Press Enter Key

SELECT TOTAL TIME

4.0 or 8.0 (sec)

aan

i No e000

t 17] Simchonied with tigger of

I the oscilscope. Pusewave-

form from "L" 2 “His

observed.

Note:

Though it may be difficult, you can get it by ad-

justing TIME/div value of ‘the oscilloscope within

| 2ousec. ~ 2usec.

3

ETEST DATA DISK

For testing DSS-1, load test data from this disk at first

‘and make it according to following procdure. When data

is loaded, display shows as Fig. 8.

(PROCEDURE 1.

1. Press System Sw. (LED becomes it) to call test pro-

‘gram. Display shows as Fig. 9

Fig. 9

SYSA P01: VCA1-R1

VOICE No.1

Now itis in OSC t Level Check Mode

© OSC 1 Level Check and Adjustment (KLM-783)

1. Connect an oscilloscope (DC, 0.1Vidiv., 0.5mSiciv) to

‘TP2 (ICIS 7 pin). (GND to TP1)

Note:

While checking KLM-783, connect an oscilloscope

as above unless specified.

2, Play C4 key to confirm waveform of Fig. 10.

PROCEDURE 2.

Fig. 8

Fi SYS: A Completed

Select (1-9):

3, Adjust VR101 if necessary.

4, Repeat above 2), 3) to check Voice 2 — Voice 8 and

adjust VR201 —'VR801 if necessary.

5. Among the 8 voices, difference of Max. and Min.

value must be less than 40mVp-p.

Press up key (A) of Data Entry to advance program

‘number. Display shows as Fig. 11.

SYSA P02: VCA2-R5

VOICE No.1

Fig. 11

"Now it sin OSC 2 Level Check Mode

© OSC 2 Level Check and Adjustment (KLM-783)

1. Play C4 key to confirm waveform of Fig. 12 (Fig. 10)

2. Adjust VR105 if necessary.

3, Repeat above 1, 2 to check Voice 2 — Voice 8 and

adjust VR205 — VR80S if necessary.

‘4, Among the 8 voices, difference between Max. and

Min. value must be less than 40mVp-p.

PROCEDURE 3

Press Up Key (4) of Data Entry to advance program

number. Display shows as Fig. 13.

Fig. 13

SYSA P03: VCFO-R3

VOICE No.1

Note:

‘The point of the widest amplitude of the waveform is

{or adjustment. However as the point of each voice

is not completely same, select one point of a voice

as a standard adjusting point and adjust other 7

voices with it.

Now itis in VOF fo Check Mode.

© VCF fo level check and Adjustment (KLM-783)

1, Play C4 key and confirm wavetorm of Fig. 14 (Voice

»

Fig. 14

0.4. D4sy|

2. Adjust VR103 if necessary.

3, Repeat above 1, 2 to check Voice 2— Voice 8 and

adjust VR203 - VR80S if necessary.

MEPROCEDURE 4

Press Up Key (A) of Data Entry to advance Program

Number. Display shows as Fig. 15.

Pa-'8 ("SYSA PO4: RESO-R4

VOICE No.1

‘Now it in Resorance Oneck Mode,

‘© Resonance Check and Adjustment (KLM-783)

1. Play C4 key to confirm waveform as Fig. 16 (Voice 1)

Fig. 16

4. Among the 8 voices, difference between Max. and,

Min. value must be less than 40mVp-p.

5. Play C6 key to confirm if level is as Fig. 14 (Voice 1).

(Frequency is about 4 times as much)

6. Adjust VR102 if necessary.

7. Repeat above 5, 6 to check Voice 2 — Voice 8 and

adjust VR202 — VR802 if necessary.

‘8. Among the 8 voices, difference between Max. and

Min. value must be less than 40mVp-p.

2. Confirm if the value of the envelope of resonance

oscillation waveorm is 2mS. Adjust VR104 if

necessary.

3. Repeat above 1, 2 to check Voice 2— Voice 8, Ad-

just VR204 — VR804 if necessary.

4 Also confirm if there is no irregular oscillation in each

voice.

WEPROCEDURE 5

Press Up Key (A) of Data Entry to advance Program

Number. Display shows as Fig. 17.

SYSA P05: NOISE

Fig. 17

VOICE No.1

Tow it Note Lovel Check Mode

© Noise Level Check and Adjustment (KLM-783)

1. Connect a Noise Meter (1HF-A, —10d8m) to TP1.

(GND to TP2)

(PROCEDURE 6

Press Up Key (A) of Data Entry to advance Program

Number. Display shows as Fig. 19.

Fig. 18

about

T

2, Play any single key to confirm if the meter value is

—15dBm.

3. Adjust VAL if necessary.

Fig. 20

Fig. 19

SYSA P06: Offset

VOICE No.1

Now itis in OC Ofset Check

© DC Offset Check (KLM-783)

1, Setting of the oscilloscope is DC, SmV/div, 10mS/div.

2. Play Cz, Dy, Ex, Fp, Gr, Ap, Ba, C3 in order, and confirm

waveform of Fig. 20.

MEPROCEDURE 7

Press Up Key (4) of Data Entry to advance Program

Number. Display shows as Fig. 21

"9-2" ( SysA PO7: CENTER-1

VOICE No. 1

Tow Tein tO eee

Note

There are two KLM-1050s for DDLs. Placed in the

left side of the panel is for DDL-1 and right side is for

DOL-2

© DDL-1 Clock Check and Adjustment (KLM-1050)

1. Connect a Frequency Counter to TP-CLK of

KLM-1050 fixed in the lett side of the panel. (GND to

TP-AG),

2. Confirm if the value is 20.0kHz,

46

2p

KEY-ON KEY-OFF

Alteration of the signal at Key ON/OFF must be less

than 20mV. (With new version, Semi-Fixed VRs for ad-

justing each voice will be added. VR106 ~ VR806)

8, Adjust VRS if necessary.

4. Connect an oscilloscope (DC, 0.2V/div, SmSidiv) to

‘TP-EXP. (GND to TP-AG).

5, Play C4 key to confirm waveform of Fig. 22.

6. Adjust VR2 if necessary.

Fig. 22

Not

‘Adjust lit line of the oscilloscope to the center and

then play C4 key to confirm center of amplitude of

the waveform is on the Iit fine.

(PROCEDURE 8

Press Up key (A) to advance Program Number. Display

shows as Fig. 23.

SYSA P08: DDL1-Sho

VOICE No.1

"Now & isin ODL-1 Short Delay Feedback Check ode

Fig. 23

© DDL-1 Short Delay Feedback Check and Adjust-

ment

41. Connect an oscilloscope (DC, 0.2Vidiv, SOmSidiv) to

‘TP-EXP. (GND to AG).

MEPROCEDURE 9

Press Up key (4) of Data Entry to advance Program

Number. Display shows as Fig. 25.

2. Play C4 key to confirm ifthe decay time of wavetorm

is less than 250ms 50ms as Fig. 24.

Fig. 24

250ms + 50ms

3. Adjust VA1 if necessary.

Note:

Refer to Procedure 7 as everything is quite same

except DDL-2 board (KLM-1050) being in the right

Fla. 25 [S76 POO: CENTERD side Of the panel

VOICE No.1

Notts ODL-2 Check Mode

MEPROCEDURE 10

Press Up key (A) of Data Entry to advance Program

Number. Display shows as Fig. 26.

@DDL-2 Short Delay Feedback Check Mode

(KLM-1050)

Fig. 26

SYSA P10: DDL2-Sho

VOICE No.1

‘Now isn DDL2 Short Delay Feedback Check Mode.

(PROCEDURE 11

Press Up key (A) of Data Entry to advance Program

Number. Display shows as Fig. 27.

Fig. 27

SYSA P1

VOICE No.1

"Now tis in DDL-1 Long Delay Check Mode

DDL1-Lon

Note:

Refer to Procedure 8 as everything is quite same.

© DDL-1 Long Delay Check Mode (KLM-1050)

1. Play C5 key to confirm delay sound of line-out “L"

starts to decay atter about 2 sec. without oscillation.

a7

MEPROCEDURE 12

Press Up key (A) of Data Entry to advance Program

Number. Display shows as Fig. 28.

© DDL-2 Long Delay Check Mode (KLM-1050)

1. As Procedure 11, play C4 key to confirm if delay

sound of line-out “R” starts to decay after about 2

Fig. 28 [~VGq P12: DDL2-Lon sec. (Sound check just by listening is enough.)

VOICE No.1

Now tis in OOL2 Long Daly Geek Wode

MPROCEDURE 13

Press Up key (&.) of Data Entry to advance Program

Number. Display shows as Fig. 29.

"1-2 (" SYSA P13: DDL-MUT

VOICE No.1

‘Now Bs in Delay Time Mute Check Mode

8

‘© Delay Time Mute Check Mode

1 Press Mode Sw. (Program/Parameter) and select

Parameter No. 81 (Delay Time).

2 While pressing any single key, move Data Entry B

Slider randamly.

3 Confirm if Delay Time is changed following the

Slider's move, and if the mute is on the sound when

the time is changed.

4 Repeat above 1 ~ 3 to check DDL-2 with Parameter

Number 92.

UPA sa AN

REFERENCE DATA

Here we are introducing newly adopted parts for DSS-1 mainly. However, please note, though they are same name,

‘such as CPU8085, processing speed of the one for DSS-1 is much faster than the one for POLY-800 and not compat-

ble each other. if misused, malfunction will happen. For those parts in replacing and ordering, please refer to our parts

list. They are listed separately with different code number.

1. PROGRAMMABLE FLOPPY DISK CONTROLLER »PD-765A

1m PIN CONFIGURATION IBLOCK DIAGRAM

reser, cafe wes

mo—i2 38} —~0 RWISEEK

Who— 3 ‘38/2 LETIOIR

So 4 37} —-o FLTRISTEP-

eels [sia ox

08,0-—+| § 35 |+-—0 READY over) ‘BUFFER

08, 0-—- ‘4]-—e WPRTI2 SIDE

oe] 3sf—s rum

eels ufone

DBO 19 31}-—0 Pst

ee 3 tomn

one [oun bee

ao 13, 2}-—-o ust ve

oie [one

into] z{ soe _ sm [on

oko —fi8 | —-own twwace [re

ono—| comer

wane fn [oem = vow

o—r [san 4

oo 19, 22}-—winoow - ‘READ! “WINDOW

endo—z0 2i-—ewcun 4 ia SINC

we

covet

ame reso

[= Wn soe

F KS rom f= noe:

nser—| [pre

ae ae

ewe

sora vs

te un [ew

outer

— |

= Ky fore” | =rawsee

|-=t0e

[tron

[-nnster

49

TERMINAL DESCRIPTION

#PD7265 terminal functions,

Terminal Condition

name een when reset

Pals the FC ining coon.

+ Sets ihe dive inertace oust LOW" except for PSO, PSY and WOATA

‘RESE) 1 (undetermined),

‘+ nthe main ite sie, ets IT and DRG to "LOW" and 8, to 08 inn-

put conden,

RO 1 | (arto! Sorat for aking the main syste ead ot data from FDC o data bus,

wa 1 | onto’ srl or making te man system we data trom data bus in FC.

cs ' ‘Makes RD and WR signals effective.

‘Sara forte purpose a selecing sas restr or data ops sie 0

A 1 ‘through the address bus. When 0 the status register is selected; when 1 the

‘tart selected

‘DB, ~DB, wo ‘Data bus for 3 states in both directions. Input

‘Sgnal to request data transfer in DMA mode. A pullup resistor is required ex

Ra ‘capt for the xPO7B5AC-2. low

‘ACK 1 DMA cycle permission signal.

1 1 | ta anster completion ication sina -

woex 1 | Slnalo inte hat ive reat ead as ached physal staring pos-

tom of rack on medium

0 | Sia to eqvest he main system to perfor processing of transtered data

wt ‘and execution resus for main system. Cal

|_| Stletase, TTL let coc egos pabup rest. Standard enor. 8

* ‘MHz; mini floppy: 4 MHz

Timing signal or data transfered ding wing, Must abo be int dung

wo 1 | aang tor sbsequent use, Pease scone ise wih se of 6. FM: 16:

(MFM: 8¢., (: period of ¢ input)

‘Sal wich storm by VFO cet. Used to sample ROATA ck Bit and

wooo 1 | data Jadgment sto whether clock io stabs tobe sampled cone

‘ste te FOC

wou © | Sina to set ve readwrte ead nd contin,

“This sgn becomes FLT when RWs specie as RWISEEKsigraleases

ureter o_| sive FAUL conten

‘When SEEK i specif as RWISEEK signa, is becomes STEP, anda seek

pulse i genet.

‘When RW is specified as RWISEEK signal this becomes LCT and indicates that a

the ve read head has slece the 4d or a subceavent yer. When

tern © | SEEKis pected as FWISEEK sal ths bcaes OR and incase es

fon of the seek con. When is away fom the center when 1s tard

the cnt.

nwaseex 0 | feng te dve erace Sarl, is denies tase which can ao be used

for east or for sek. hen inate RW: when 1, nates SEEK

vee = _| +5¥ power soniy

ono — | Gone

CMOS DATA SEPARATOR SED 9420C

1 BLOCK DIAGRAM

sinc ted | 00 as

‘tecton cat orp

ind ouae

gle i)

Ti

mom oil 22 LHS i

rea 2

i 3

Fl 2

EH —$OWm

Hy $102) Frequency

s ier erat

7 Fa>— > 0

Pree

gel =| 32 | |

ww

Frequency FEED BAoK| Switching ting Data output i a

ool divider circuit (or wan Setection circuit |_WIND | circuit =

cs Tt cig

z a O-O

ge age z a: A

a: = EE

PIN CONFIGURATION

‘SED 94206

0501 2 Wan

2oscz 31m our

sox) ema m

anst2 arcu

sw cn

sme wou

27 RO OATH v8 TEST

‘wanoow 97 ure

somneurrs

mewn 15 oF eT

i mwsto 4 corm

s2¥n 9M

araveraratavavetetetatd

seb b EFS sh sh

51

EXPLANATION OF TERMINALS

Terminal

Terminal

Kee —_ Function

= (1) Inversion ampli gat put terial for crystal oscltor creat

Z ” {@) Input terminal for 16 MHZ extemal lock input.

2 oscz ‘nverson ample rain ouput eminal for crystal osciltor creat

(ek P0765 system ouput eminal used for FOC

3 cut “= Binch foo: frequency {= 8 MZ

+ Sinch fopy: frequency 1 = 4 M2

‘ Test" “Test terminal ith pulbup resto) or function confirmation,

5 nc ot connected

. ‘onl input Spal rom FOG forte purpose of detecting the GAP region and SYNC exon

- Lid (with pul-up resistor.

7 TRO DATA’ | input terminal for read data sna Kom fopoy disk drive (FDO) (with pup resistor

8 ‘Wivoow | Ouout terminal for DATA WHVDOW signal used to divide DATA sgnalino data pulse and cock pub.

‘Output ein! or data inl produced om AD DATA Sigal. Read into FC together wih WINDOW

2 ATA signal, thn separated into data pulse and dock pulse.

“Termial or switching between double density and single dens recording format (with pubup essa).

0 tmrwirm | + Double deny (MEM): hgh level

«Single densty (FM): ow level

Terminal for switching between Sich fopy disk and Binch foppy dsk (ih pup resis)

" munssto* | Sich floppy: high level

* Binchfoppy: low evel

2 Wen Digital system ground tein

13 Ven “analoge system ground teminal (VOD secon ground).

4 CONTROL | Input minal for VOD (Vage Contoled Oscar) secon contol votage

' aa Input erina for apting fst votae forthe purpose of correcting the VOO section oscaton center

frequency (ost votage is generated using extemal capaci)

“Terminal for conectng oop itera PLL sytem. Selcied when requency piled i folow ing Sk Fed

" vr setcton

7 1 Terminal for connecting lop fitrinPLL system selected when readingIDand data afer e quency is puedin|

8 TesTt Test terminal used for func cheng. (ormaly not connected.

Wien dock for FDO (@POTSS syst).

1 Binh foppyIMEM: 5 = 1 6S

® ‘weux

+ Siac foppyFM T= 4 nS

2 a CCA extemaly attached terminal used for Ser cut

(look used for FOG (MBBB7? system, FOTTEX system)

a cue ‘= Binch floppy: frequency { = 2 Ni

+ Sinch fopy:fequency t= 1 Nitz

2 TRIG IN* | Tégge pt terminal or mer crcuit (wih pultup reso

2 TH OUT Timer cut ouput einal (mer used o set head load tie, motor stop tine, ete)

24 Veo +54 ne vate trina

DRAM MSM4256L (256K x 1 bit)

1 PIN CONFIGURATION

_———

O & msmazseL Oo

igo a

@ ®

AA WA A A

CETL Te Poe Te T8\ ls

WW Ws ths iS

Q Ve D RAS A, Voc As Ay ia

(BOTTOM VIEW)

TC 9154 AP BLOCK DIAGRAM

roi ag i

©—@ O- é

von,

INTC 9153AP/TCSIS4AP EXPLANATION OF TERMINAL FUNCTIONS

Terminal | gymbot Explanation of function Remarks

7 ¥. Tera oar (-) poe

1048 step attenuator output. Signal applied to IN is attenuated from 0 to — 60 symmetry

: ven dB in seven 10 08 steps. ee

3 uM, 10.68 sp ater pt

‘ ana | 86 guns tina

5 um, 2.08 sp steno pt

i. ar 28 step atentor cut, Sal apd to Nis tenuate rom O10 8 8 in

= five 2 0B steps.

‘Strobe input terminal. Attenuation amount and channel selection signals taken

5 w in at DATA and Cx terminal are atched by puting this terminal at “H” level

er "Hint apes semi eves da ema a ey

vere

‘ evo Cen il ot TODS

’ ow (eat tein. Cock nt x pr of aking tan am data

a oo Aten amount ache alton dts pt tering. pt as CK

Sona congo 8B

1 nour, | 2s8stp ater owt Sra appa Wis stoned tom 01088 in

| fe 2 se,

2 RAN, 2.08 step attenuator input.

" sno | gourd teria

“ nm, 108 sep stent rout

a com 1068 step ateuator ott. Signa apd to IN is ttnuated tom 0 to —60,

«8 in seven 10-08 steps

Terminal for applying (+) power

(SGA-1 TERMINAL DESCRIPTION

no. | fiNye | vo FUNCTION no. | fiNye | vo FUNCTION

1 [mci —| 1 | taster eck 20tn a | Ne. Ne.

2 | wo +5 @ | wo +5¥

3 [oxo ‘eno ‘o_| ow eno

«| ne. c. 4_|_swmar | 1 | zeno cnoss evecron

5 | Ne wc. 6 | owe 0 | ata tout Enable

6 | eset | 1 | Sytem Reset | _oneoo | 1 | OMA reqwes

7_|_ Ree | CONNECT a GNO a7 | oreat | 1 | OMA reqest

| GATE | 1 | tpossibe to wre data white | one | 1 | OMAroqest

@ | Ne. uC. 49 | oneas| 1 | OMA rowest

v0 | NG. no. so | paca | | | OMA request

| MPUE 1_| Timing Clock st RES 1 [OMA request

2 | os 1 | att, read 00-06 and 07 eutpat | [52] ones | 1 | DMA request

13 | _AOWT | 1 | a, 07 ouput “L", ooDeiatn| | 53 | _oREG7 | 1 | OMA request

4 | 00 1 | Bata Bur 34 | oneae| 1 | OMA request

| m1 1 | Data Gur | oneoo | 1 | OMA roqest

16 | 02 1 | Bata Bus 6 | pmeoro | 1 | OMA roqest

7 [08 1 | Data Boe s7_[_oneait | 1 | OMA request z

| 0 1 | oa Boe se | oneorz | 1 | OMAroquest

10 | 05 1 | Bata Bus se | _OREGIS | 1 | OMA request

| | Bata Bus | _oneoe | 1 | OMA roqest

a | 06 | bata Bas a1 | _onears | 1 | OMA request

| eno wo | GN eno

z3_| vo +50 | wo +50

z_| NG. Ne | oreo | 1 | oxo

| sis O_| GAM Rehesh | oreo | 1 | oxo

2% | csi O_| Chin Steet 6 1_| ono

zest 0 | Chip Select 7 _| ow

ze | cHo ‘0 | Address to show OWA Request c| | 68 1_| exo

2 | cw 10_| Adress to stow OMA Request ct| | 69 [ow

[cH (0 | Address to show OMA Request cH] {70 | oneaze | 1 | GND

1 | ALN (| Start to generate CAR latchtining| | 71 | _oneazs | |_| GND

az_| OWEN | 0 | Wt enable for ORAM mz | N ne

| oN [ou 73_| pov | ipand eyle of eadinghwrting

‘aM _| stant | 0 | Timing signal for GATE-ON m4 | _Ne. KC.

| NG 0 [uc 75_| R060 | teterva 50008

se | sur (| Timing tr St Wavelrm dat ct] | 76 | NC. NC.

| _e0P 1 _| DRAM wring Mode cancel 7_| sor 1 _ | Expand eel of eadinghwrting

Waveorm data latch timings | | “73 | _ NC NC.

a | ° | tg et 7 | ws 0 _| terval 5008

wo | _ AAS ‘0 | ROW (RON Adress STROBE hae “

| cas | Column Address STROBE ad

(GA-2 TERMINAL DESCRIPTION

No. | Name | YO FUNCTION no} fiNye | vo FUNCTION

7] ne ne. af ue No.

2_| wo + @ | wo +5

3 [_ exo ono 3 | oo co

+ | ne No. [ne NG.

s | os 1 ‘CHP SELECT active | nc Ne.

oie t FAABLE ® | xe. Ne.

7 | reer [1 ESET acive“L" a | NG. —_[uc.

© | we Me. @ [nc [xe

s |e. No. @ | we ue.

0 | 0 1 ADDRESS BU wo | NG. No.

nfm n ADDRESS BUS st] NG. KG.

|e 1 ‘ADDRESS BUS NG. ue

| 8 1 ADDRESS BUS = [NG us.

| oo 1 Daa Bus se |_acKo (| Sonal for Wavelorm data tes

7% | 1 Data Bus [act (| Signa for Waveform data late

«| 1 Data Bs | ACK © | Signal or Waveorm data ate

a7 | 03 1 Dat Bus s7_| nex (| Signa for Waveform data atew

|b 1 Data Bos se | ace (| Signa or Wavetorm data lateSi

| 0s 1 Data Bos | Aa (O-_| Signal for Waveform deta ten

=| 06 1 Dat Bus | ACK (© | Signa for Waveform data teh

zo 1 | Ar (© | Signal Yor Waveform data te

2_| ow | ow on

a oo +5

2 | os 0_| Astros for DRAM

3 | om (0-__| Adress for ORAM

3 6 | oe (©-_| Adress for ORAM

2 | ms 1

a alae 1 | a i

; 5 or @ | a | DRAM witty mode cancel

= 7 | _ser {| Timing for Si Wavetorm data ath

aH ° ‘adress for DRAM

= : te a T_[_REFSH | 1 [Row adress tor ree

= 72_| START | 1 _| Timing signal for GATE OW

= 7 | KG. xe.

# | _ RE T [Generate WTERWAL Tah ning

$ 7 | NG. NG

= — - ze | _wsze | 1 | Bee Pi momar

a 7 | we 1 [ies se it a

7 a 1 Pes ORT egos

neon 1 | ee ow DA ee

| ows 1 [ip select

FLOPPY DISK DRIVE MD350

(PERFORMANCE SPECIFICATIONS: MEFUNCTIONAL SPECIFICATIONS

M0350 Recording density on

Double densityiSingle nermost track (BP)

density

- (TRAGKISIDE)

Recording capacity ‘1M/SO0K Number of tracks

Disk capacity (Bytes) (TRACKIOISK)

Track capacity (Bytes) 6.25413, 125K

Track density (TP!)

‘Average waiting time 100 msec.

‘Outer circumference

‘Access time ‘Track radius

‘Time for movernent 3 msec. Inner circumference

between tracks

‘Modulation system MFM or FM

‘Average access time 100 msec.

Head setting time 20 msec.

Head loading time

ean 25 msec.

Motor starting time yes

(Note 2)

Data transfer speed

Double density: 250K

bits/sec,

Single density: 125K

bits/sec.

Note 1)

Only when optional accessory solenoid is installed.

Note 2)

Under chucked condition

87

(ENVIRONMENTAL CONDITIONS

POWER ON 400 msec, (max)

me

ncn =) a0 mse, ci) —}

DRIVE

a ee

{HEAD Loa i

—}}— 500 nsec. (nin) |

INDEX

Il (oi) FA 20 ie) wth eo (ain)

‘STEP —T_ hi-r-.ti

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- MBHP Aout Balanced cv-2 PDFDocument1 pageMBHP Aout Balanced cv-2 PDFjbwiltsNo ratings yet

- The Build Process: of (GNU Tools For ARM Embedded Processors) 2013-12Document16 pagesThe Build Process: of (GNU Tools For ARM Embedded Processors) 2013-12jbwiltsNo ratings yet

- LinksDocument2 pagesLinksjbwiltsNo ratings yet

- Yarns v0.3: SMT PartsDocument3 pagesYarns v0.3: SMT PartsjbwiltsNo ratings yet

- Tides 2Document3 pagesTides 2jbwiltsNo ratings yet

- Ripples, v4.0: SMT PartsDocument3 pagesRipples, v4.0: SMT PartsjbwiltsNo ratings yet

- Ripples Quickstart PDFDocument2 pagesRipples Quickstart PDFjbwiltsNo ratings yet

- 4ms Pingable Envelope Generator: Eurorack Module User Manual v2012-06-01 (Rev4.2)Document12 pages4ms Pingable Envelope Generator: Eurorack Module User Manual v2012-06-01 (Rev4.2)jbwiltsNo ratings yet

- Ripples v90 PDFDocument1 pageRipples v90 PDFjbwiltsNo ratings yet

- Larger FormsDocument252 pagesLarger Formsjbwilts100% (1)

- Cu 31924021809797Document192 pagesCu 31924021809797stuiterballetjesNo ratings yet