Professional Documents

Culture Documents

Unit-2 8085 MP

Uploaded by

Gowri Shankar0 ratings0% found this document useful (0 votes)

31 views7 pagesAvionics

Original Title

Unit-2 8085 Mp

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentAvionics

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

31 views7 pagesUnit-2 8085 MP

Uploaded by

Gowri ShankarAvionics

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 7

aa

| Microprocessor ig o Singla TC CIntegvoted civeuit), Copoble of

[Performing avithmetic and Losicak opervotione dadined by

|the Programming -

[poss net

| OLSA 78 oN BbIE microProcasor (MP) Suitable for wide

range OF APPUicetions. Tt is a Gingle-chip,jmog device

implowanted with approximetely 6 200 brYengistors On a e4ni22

milichip Contained in & 40 Pin dusl-in-Line (DIP) Pacteage -

2085 Featuves ¢

ee ae

4: 80BS 16 & BBIL micvoprocssor.

| #T4 7S o 4oPin Dip Couct mitna Package ) TC oPpevotea in

| ysv DC Supply .

ATE Con oferate vith 3mu2 cleck greauancy (9085)

For 8O2SA-2 VErwSTon Com operate at mouxinauws of Sma

TE hog 16 oddvess lings, 8 dotolimes Ond 64kKb Memovy

HTL hosEbIe GPR Coenerat Purpose Registers) and two

lb bit registers (SP oma PC).

ae ide Give haxdwove Interreets |

4 Deane) eeraesresr GS. BSIS:'S ond TnTR

Ik Con SuPPort 74 Tratmection

| & Provides Control Sigvele (LolM,RB,aR D to Control the

bus Cycles ond hence extermat bus contvollay not revived

| & Tt algo hag Geviat Elo Control which oews

| Beviak Communication CSod, $TD)

|

ARCHITECTURE OF BOBS Microprocessor

oe oe eek

The architecture OF BoRS consist aP the Following blocs

4 Registe~s

* Tncvementev nee

Piet

| ae Artitnmetic and losic cunt t

|p Jalepvenestavertlereteconlbe & Tntervert Contvol

and mechina cycle Brody 4 Jevial Ts Contvol

| a Address bugter

4 padvess budiev ond deta

| buster

|

A Timing and Control

Civceitory +

)

[AecuitecwRe OF BOSS [A

pee

)Geweror perpose REaisters +

A enter SPURPe SE. REQTSRS,

> BCD E,Hamd Lave Sbit Registers Canbe ugedos a Seperate

Bbit Reg. ov OS 16 bTE Register Poivs, gc, DE amd HL.

? Wiz ary Capaimmieise Ganction of af CBI polneey

ov memory Pointer

Fig. 12.4 Architocture of 8085

2) SPECIAL Purpose REGISTERS -

Ae EE ee

Astumnaoror CARegister)

sAccumuatoy if tvistate 8 bit Regtster.

STbIs the Part of the Avithmatic [Logic unit , which 75 used

to Stove Bit deta during the Arithmetic amet be gicat

OPewattons: Cmost of the Lime Regutt wilt Store in A Reg)

Flag Regtster

> Flag Register fs an Bbit Register -

> During Avithmartc oPewotions Flogs ave set ov

Reset (1 ove)

Addwess | Doto. Budiey + 2

Bere ee Seer 2

| & Addvess [Data buster 1S am EWE Reaister

4 The Content o& the Stock Pointer (ov) Presram Counter

Combe oadad in to the oddveas budjer anc adaras

dota onder:

#¥ The Zbit Internal deta bus

addvess data buster -

Inte rrert Contyot ¢

Ro

4 Interrupt control a capes the intermet Signals Comming

kya external devias and it.contvol dre interrupt

activity of Be85MP*

BT has Rie Mntecrvet Signal, nawely TRAP, RSTTS,

RSTES: ASTSS ane INTR-

is algo cowected €o the

Te

gesior Ele Contwet + ;

& Tt Provictes Lwe lives, SoD avd 3 for Serial Conn orion

whe gevial OMtPut dake(g on) ling is o3e te Send dote-

gevially ond eviol input dake (S 1D) Une fs Uged to veatve

doke Sevially -

RLOSOeSNa AR RESD

|W e Te algo a gbit vedistey Used to Stove the dake

| Lempormvily , when ALv Performs tha Competing BSunctions

natanaction Reatstesc

Y rgumction Registev is an Bbit Nesistey Used Fo (ood Ere

Ingtruction 1S Retcved

| ingtructton Copcede ), when on

Grom memoyy - |

4)

ltnatrmction Decoder!

|" Decodas the content Of tre 7 nsteuttton Register (ie ot

Gund aceominaly Qives Information boty Efealitg and canbe ‘

Axithmetic cod Cogic yale

as aontthmetic logic Unit PertForms the arithmetic

Opercekions Suchag addition, Swotvec tom ,inCveman |

and logit operations CAND, ORaMA Ex-oRD ee

APPLcATION oF O85 MP

& Used im Colcutotoy A Usedt tw Pro@ss Controt

+ Used In home apPlianas Sere

> ir a USELIM PRowm

used tn date acquistion stems Boel

werk

4 USeA In militorry applicaaions

| # LSet Im ComPuking appliccions

| ® Used in Tndustny cont-roliers

> Tt has Five. Flags Ui) Stan Flaxs) (i) ZexoPlage) (Aw

Corrs Gloag (AC)iv) Parity Ploa(P) WV) Cannd Plog(cy)

De_ 95 Dy 93 Do Ps

Scores Sealer?

SignPles <— sn denin

. oe lag) Coors Fes (Al Parity Cl-fP)

Sign flea G) 2

a ARLET execution of Atithmeric OPerakion , 1f bit Pa of |

the vresult 16 °)', tro sigh Flag is set otherwise FETS veret |

Zev Flas)

A TE bre DS oFthe Resttis zero ( During Avithee ls ow, |

dhe zeve Bleg Is setiothawise ie 1S Reseto>

Auxiliary comm Flog (AC)

a TR Corry fs generated by aiait Da ond Ped to

pisit D4, tha AC Plog ts Sek otherwise Reset - |

Party &lea(P) |

8TH awithnete Operation, TS the vesuit hag an Even number

of 1's, the Parity lag is Set. TH the vesutt hag an odd number

O8 I's fhe Slegis reset co): |

CARRY Fle3(ce |

HK TN avithmetiC SPEVEKION when Carry 15 gererated, Lhe

Corts Plas 1S See CI) Othanwise ie Ts Reset

§kock Pointer (SP)

ee

memory Pointer: C SFR)

* Used to hold Lhe address of the bop elawent of tne

| Stack Cwhich Potlosg LiFfo Clost in Bivst out) bosis)

Program Counter(PC)

| + Pwodtaw, Counter 1S a I6bit SER REgistey

& Used to hold the memory oddvess of the noxt

instyuction to be @xecuted -

‘* DePends onthe execution Program Counter

HenCvewantey /Decementer,

+ Incevementer/Deeremertey 5S an 16-bit register

# TA is used €0 add (ory Subtract one Prom the content

oP any of the lbbit register . CSP oy PC)

% Stack Pointer 15 & Ib bit TEQSter to be UBEd og ov |

|

oF 8085 mP

Pin Detans eA MPSS DARe U

-—S

ae.

10/7% } Sate

| ia5 | sone

}—- WR 1

Recetot

owe

veces, 28

oe

Fig. 1.31 (a) Pin configuration Fig. 1.3.1 (b) Functional pin diagram

VEC &VSS2 Te Requives +5V DC Supely with Ground |

KramaX. 2 A tuned Civeuit Lixe LO, RC ov crystar is

Connected at those two Pins. The interned Clk Jenevator

divides ogCietoy Frequency by 2, Cie internat Clk Freq.

is gmnz, theve Gore Crystal osc. must“ ak Breq .of Smad

Clk OUTS Used os a System Clock For other davies .Tts

Frequency is hol@ the oSciuate+ Prequency.

Dorvbus and Addvessgus

SThe BbIe cletabus (Do-Dr) 75 multiplexed with the ener)

hag (Ao-Ar) of the obit oddvess bas.

DS During 3t Part oF the machine Cycle (Ti) , lower sbits

of Mamors acldvess appear on the bus and remaining

Port of De mochima Cycle (T2 ond Tz) these limes ove

used as @ bidivecttoral data bus

5 |

AgtoAis : The wppey hal of tre 16bit addwess |

appears on the addvess lines As toAis (mse of |

tb bit ody)

Contvol and States Signals +

DAN AS A

(a) ALE! Addwess (etch enable

ls active high Signet used to damuttiple, Ma

addveszs and deotebus seperately daving T, wet

4b TeAines exterrnar lech

Ta Tg mochine cycles Cx

bo SePevate addy. ond dot= bea) |

ee ae =o |

QO) RD LGR : A be on RB indicates that tha date must!

be dead Gre te Gelacted wersrilecstions ov Tle

Port vie date bus

A lew on WR indicates thar the data must be writtey

inte the selacted memory lecotion ov T lo Ports

vie datebus

(C) To] , $0 nds Tradiceees whathaw Tlo operation

‘ We OT mamery oPerekion

Tol +0 , memory oPeration

TolM =1 ,Tlo operextens

Gots) | indicates the type of mechne Cycle in Progyeks.

(WP) READY T Te Ts usecl by tha MicwePwecasser to Sense

wlethey & Peripheral 15 weady ov not €or doty trometer,

TE not, the Promeser Woes Tt is thug Used CO

Synchronize Slowey Peripherals to he microproGsser:

Interrupts SiGwers

the $085 hag five havduarve intevvust SPonats | RST+S

RSTbS, RST SS , TRAP ANA TNR. Tha micvopracaasey Yecognilos

Intertepe Vequegts on loge Lines at the ent o€ the Cuvveht

InStyactiom execution

The INTA CIntevruet Acxnowledge) Signal *5 used to indi

RVG tne) Seema MN oe cote ledlne lite Tenet cet reee

Seviet Tlo Stgnat ®

(A) HeLD: Tndtcotes that anothey master is Vequesting

Pov the Use of addvessbus, clatabus and Cont~at bus

(B)HLDA! This active high Signet Msused te atknow

-ledge Hold Reqwest.

eset Signa

A) RESETINIA low on this pi

DSets the Progvam Counter te 2evo(oeecH) and

Ckovs INTE Plog

ie the Trtewrupe enable ana HULDA Glip_Slees

3) Tri- states the dota fae Shr

contol bug S

4) A ¢tect s

the ©

bo ener eta ee

i ee

f | OReser sy y a

| a aaa OUTS This active high Signet t Poca

ing ¥ *

| opens: ey This Signal fs synchvoniaed to the

pins cK amd i€ Can be used to veset other

Ib vides Covmected in the $ygtem -

NSTRUCTION ExEcUTION AND DATA Flaw Iw goss

dy in order bo execute Prograwn, tha Stovting addwess o8 Cra Prozvom $8 Conded

jneo tha Progam counter (PC) «

\ FAD ats: qoas sends tra Camas ob pc on om oddvets/on-tht-odd woes is and

| * acuveses RB contrat signet

| xuPpon yealvine the addvess ona Bd Signet memory Pues the Contents|

of adbtessed memory Lacation on Une dake lous Which |s am oPcode of

Of cenatraction, Mearwainte PC 1S incvemented to Poiht tha naxt

amary Lecation in the Program seqnenet |

oN ts daactiveseA ond opceda. 78 Loaded into the Instruction

syegister via tatevnel bus of microproassoy

|e Tha Ingernction dacoding unit decodes tne instruction amd

TaRermosion £0 the Uming ond control unit to

# ®D sisi

ovides :

wee Teaser SignlS oy Tngtyaction execetion -

\ eae = ve ¢, 0%

gee MNT C,08K Coa

ascaset ore Ewo OPevation

convert. ID oP es ae

inte Nex

J0e0 TSE l opcede eee!

28 | date

AdT C,08H

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Ec8553 DTSP Unit IDocument37 pagesEc8553 DTSP Unit IGowri ShankarNo ratings yet

- R2021 - B.E.EEE - DronaDocument104 pagesR2021 - B.E.EEE - DronaGowri ShankarNo ratings yet

- Additional GatepassDocument3 pagesAdditional GatepassGowri ShankarNo ratings yet

- Ec8553 DTSP Unit IDocument37 pagesEc8553 DTSP Unit IGowri ShankarNo ratings yet

- Important Dates - Odd SemesterDocument2 pagesImportant Dates - Odd SemesterGowri ShankarNo ratings yet

- University College of Engineering, Panruti Leave / Permission ApplicationDocument1 pageUniversity College of Engineering, Panruti Leave / Permission ApplicationGowri ShankarNo ratings yet

- Possible Viva Question 17AE24703 AVIONICSDocument5 pagesPossible Viva Question 17AE24703 AVIONICSGowri ShankarNo ratings yet

- Theory Course File Content - FormatDocument1 pageTheory Course File Content - FormatGowri ShankarNo ratings yet

- Professional Body Application - Form - BESDocument2 pagesProfessional Body Application - Form - BESGowri ShankarNo ratings yet

- Example 9.6Document4 pagesExample 9.6Gowri ShankarNo ratings yet

- MPMC Lab SyllabusDocument1 pageMPMC Lab SyllabusGowri ShankarNo ratings yet

- MP&MC Lab Manual-2k17 Final (2013r)Document144 pagesMP&MC Lab Manual-2k17 Final (2013r)Gowri ShankarNo ratings yet

- MicroprocessorDocument38 pagesMicroprocessorGowri ShankarNo ratings yet

- Final Avionics Lab Question Pattern With Demo Time SlotDocument2 pagesFinal Avionics Lab Question Pattern With Demo Time SlotGowri ShankarNo ratings yet

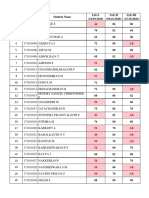

- IAT Theory MarksDocument2 pagesIAT Theory MarksGowri ShankarNo ratings yet

- Example 9-7Document5 pagesExample 9-7Gowri ShankarNo ratings yet

- 17Ae24703-Avionics Laboratory: Email AddressDocument9 pages17Ae24703-Avionics Laboratory: Email AddressGowri ShankarNo ratings yet

- Avionic Systems-ADF, NDB, VOR, LORAN, OMEGA, MLS, DME, TACAN, GPS, ALS, VASIS, DNS, INS, RNAV, VORTACDocument9 pagesAvionic Systems-ADF, NDB, VOR, LORAN, OMEGA, MLS, DME, TACAN, GPS, ALS, VASIS, DNS, INS, RNAV, VORTACGowri ShankarNo ratings yet

- Example 9-4Document7 pagesExample 9-4Gowri ShankarNo ratings yet

- Code Converters - BCD (8421) To - From Excess-3 - GeeksforGeeksDocument9 pagesCode Converters - BCD (8421) To - From Excess-3 - GeeksforGeeksGowri Shankar100% (1)

- Example 9.6Document4 pagesExample 9.6Gowri ShankarNo ratings yet

- Interacting with a Fighter Plane's AvionicsDocument20 pagesInteracting with a Fighter Plane's AvionicsGowri ShankarNo ratings yet

- Example 9-5Document3 pagesExample 9-5Gowri ShankarNo ratings yet

- Interrupts in Microprocessor: Types and FunctionDocument12 pagesInterrupts in Microprocessor: Types and FunctionGowri ShankarNo ratings yet

- Avionics-Ae 2401: Unit - 1 Prepared by Rajarajeswari.M Mohammed Sathak Eng CollegeDocument129 pagesAvionics-Ae 2401: Unit - 1 Prepared by Rajarajeswari.M Mohammed Sathak Eng CollegeGaneshVijay0% (1)

- Avionics Systems Instruments OverviewDocument23 pagesAvionics Systems Instruments OverviewSHERIEFNo ratings yet

- Digital Computers Types SchematicsDocument13 pagesDigital Computers Types SchematicsGowri ShankarNo ratings yet

- Unit 2 MicroprocessorsDocument6 pagesUnit 2 MicroprocessorsGowri ShankarNo ratings yet

- Memory: Major Memories, Distinction, Computer Memory, Volatile and Non Volatile Memory, RAM & ROMDocument32 pagesMemory: Major Memories, Distinction, Computer Memory, Volatile and Non Volatile Memory, RAM & ROMGowri ShankarNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)