Professional Documents

Culture Documents

Vp0104 P-Channel Enhancement-Mode Vertical Dmos Fets: Features General Description

Uploaded by

Anca SterianOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Vp0104 P-Channel Enhancement-Mode Vertical Dmos Fets: Features General Description

Uploaded by

Anca SterianCopyright:

Available Formats

VP0104

P-Channel Enhancement-Mode

Vertical DMOS FETs

Features General Description

► Free from secondary breakdown The Supertex VP0104 is an enhancement-mode (normally-

► Low power drive requirement off) transistor that utilizes a vertical DMOS structure

► Ease of paralleling and Supertex’s well-proven silicon-gate manufacturing

process. This combination produces a device with the

► Low CISS and fast switching speeds

power handling capabilities of bipolar transistors, and the

► High input impedance and high gain high input impedance and positive temperature coefficient

► Excellent thermal stability inherent in MOS devices. Characteristic of all MOS

► Integral source-to-drain diode structures, this device is free from thermal runaway and

thermally-induced secondary breakdown.

Applications

Supertex’s vertical DMOS FETs are ideally suited to a

► Motor controls

wide range of switching and amplifying applications where

► Converters

very low threshold voltage, high breakdown voltage, high

► Amplifiers input impedance, low input capacitance, and fast switching

► Switches speeds are desired.

► Power supply circuits

► Drivers (relays, hammers, solenoids, lamps,

memories, displays, bipolar transistors, etc.)

Ordering Information

Package Option BVDSS/BVDGS RDS(ON) ID(ON)

Device (max) (min)

TO-92 (V)

(Ω) (mA)

VP0104 VP0104N3-G -40 8.0 -500

-G indicates package is RoHS compliant (‘Green’)

Pin Configuration

DRAIN

Absolute Maximum Ratings

SOURCE

GATE

Parameter Value TO-92 (N3)

Drain-to-source voltage BVDSS

Product Marking

Drain-to-gate voltage BVDGS

SiVP YY = Year Sealed

Gate-to-source voltage ±20V 0 1 0 4 WW = Week Sealed

Operating and storage temperature -55°C to +150°C YYWW = “Green” Packaging

Soldering temperature* +300°C Package may or may not include the following marks: Si or

Absolute Maximum Ratings are those values beyond which damage to TO-92 (N3)

the device may occur. Functional operation under these conditions is not

implied. Continuous operation of the device at the absolute rating level

may affect device reliability. All voltages are referenced to device ground.

* Distance of 1.6mm from case for 10 seconds.

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

VP0104

Thermal Characteristics

ID ID Power Dissipation θjc θja IDR† IDRM

Package (continuous)† (pulsed) @TC = 25OC

( C/W)

O

( C/W)

O

(mA) (mA)

(mA) (mA) (W)

TO-92 -250 -800 1.0 125 170 -250 -800

Notes:

† ID (continuous) is limited by max rated Tj .

Electrical Characteristics (T = 25°C unless otherwise specified) A

Sym Parameter Min Typ Max Units Conditions

BVDSS Drain-to-source breakdown voltage -40 - - V VGS = 0V, ID = -1.0mA

VGS(th) Gate threshold voltage -1.5 - -3.5 V VGS = VDS, ID = -1.0mA

ΔVGS(th) Change in VGS(th) with temperature - 5.8 6.5 mV/ C O

VGS = VDS, ID = -1.0mA

IGSS Gate body leakage current - -1.0 -100 nA VGS = ±20V, VDS = 0V

- - -10 µA VGS = 0V, VDS = Max Rating

IDSS Zero gate voltage drain current VDS = 0.8 Max Rating,

- - -1.0 mA

VGS = 0V, TA = 125OC

-0.15 -0.25 - VGS = -5.0V, VDS = -25V

ID(ON) On-state drain current A

-0.5 -1.2 - VGS = -10V, VDS = -25V

Static drain-to-source - 11 15 VGS = -5.0V, ID = -100mA

RDS(ON) Ω

on-state resistance - 6.0 8.0 VGS = -10V, ID = -500mA

ΔRDS(ON) Change in RDS(ON) with temperature - 0.55 1.0 %/ CO

VGS = -10V, ID = -500mA

GFS Forward transconductance 150 190 - mmho VDS = -25V, ID = -500mA

CISS Input capacitance - 45 60 VGS = 0V,

COSS Common source output capacitance - 22 30 pF VDS = -25V,

CRSS Reverse transfer capacitance - 3.0 8.0 f = 1.0MHz

td(ON) Turn-on delay time - 4.0 6.0

tr Rise time - 3.0 10 VDD = -25V,

ns ID = -500mA,

td(OFF) Turn-off delay time - 8.0 12 RGEN = 25Ω

tf Fall time - 4.0 10

VSD Diode forward voltage drop - -1.2 -2.0 V VGS = 0V, ISD = -1.0A

trr Reverse recovery time - 400 - ns VGS = 0V, ISD = -1.0A

Notes:

1. All D.C. parameters 100% tested at 25OC unless otherwise stated. (Pulse test: 300µs pulse, 2% duty cycle.)

2. All A.C. parameters sample tested.

Switching Waveforms and Test Circuit

0V PULSE

10%

INPUT

GENERATOR

-10V 90% RGEN

t(ON) t(OFF)

D.U.T.

td(ON) tr td(OFF) tf

Output

0V INPUT

90% 90% RL

OUTPUT

10% 10% VDD

VDD

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

2

VP0104

Typical Performance Curves

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

3

VP0104

Typical Performance Curves (cont.)

● 1235 Bordeaux Drive, Sunnyvale, CA 94089 ● Tel: 408-222-8888 ● www.supertex.com

4

VP0104

3-Lead TO-92 Package Outline (N3)

D

Seating Plane 1 2 3

b c

e1

e

Front View Side View

E

E1

1 3

2

Bottom View

Symbol A b c D E E1 e e1 L

MIN .170 .014† .014† .175 .125 .080 .095 .045 .500

Dimensions

NOM - - - - - - - - -

(inches)

MAX .210 .022† .022† .205 .165 .105 .105 .055 .610*

JEDEC Registration TO-92.

* This dimension is not specified in the JEDEC drawing.

† This dimension differs from the JEDEC drawing.

Drawings not to scale.

Supertex Doc.#: DSPD-3TO92N3, Version E041009.

(The package drawing (s) in this data sheet may not reflect the most current specifications. For the latest package outline

information go to http://www.supertex.com/packaging.html.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an

adequate “product liability indemnification insurance agreement.” Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the

replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications

are subject to change without notice. For the latest product specifications refer to the Supertex inc. website: http//www.supertex.com.

©2009 All rights reserved. Unauthorized use or reproduction is prohibited.

1235 Bordeaux Drive, Sunnyvale, CA 94089

Doc.# DSFP-VP0104 Tel: 408-222-8888

A052109 www.supertex.com

5

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Modbus Over Serial LineDocument44 pagesModbus Over Serial Linearindammanna123No ratings yet

- Full Download Ebook PDF Introductory Econometrics A Modern Approach 7th Edition by Jeffrey PDFDocument42 pagesFull Download Ebook PDF Introductory Econometrics A Modern Approach 7th Edition by Jeffrey PDFtimothy.mees27497% (39)

- IGCSE 0408 Unseen Poem QuestionsDocument5 pagesIGCSE 0408 Unseen Poem QuestionsMenon HariNo ratings yet

- BS 215-2-1970-Aluminium Conductors and Aluminium Conductors Steel-Reinforced For Overhead Power TransmissionDocument16 pagesBS 215-2-1970-Aluminium Conductors and Aluminium Conductors Steel-Reinforced For Overhead Power TransmissionDayan Yasaranga100% (2)

- Technology ForecastingDocument38 pagesTechnology ForecastingSourabh TandonNo ratings yet

- S2035K-SCR 200 V 35a To-218Document12 pagesS2035K-SCR 200 V 35a To-218Roberto MendesNo ratings yet

- PS223 PDFDocument11 pagesPS223 PDFKoko HamNo ratings yet

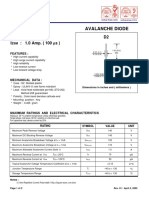

- Avalanche Diode: V: 120 Volts I: 2.0 Amp. (100 S) D2Document2 pagesAvalanche Diode: V: 120 Volts I: 2.0 Amp. (100 S) D2Anca SterianNo ratings yet

- Avalanche Diode: V: 140 Volts I: 1.0 Amp. (100 S) D2Document2 pagesAvalanche Diode: V: 140 Volts I: 1.0 Amp. (100 S) D2Anca SterianNo ratings yet

- (1 A To 70 A) : FeaturesDocument12 pages(1 A To 70 A) : FeaturesAnca SterianNo ratings yet

- 8-Pin PFC and PWM Controller Combo: Features General DescriptionDocument12 pages8-Pin PFC and PWM Controller Combo: Features General DescriptionAnca SterianNo ratings yet

- FSDM311A Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument12 pagesFSDM311A Green Mode Fairchild Power Switch (FPS™) : Features DescriptionZdravets YordanovNo ratings yet

- Features: Vishay SemiconductorsDocument4 pagesFeatures: Vishay SemiconductorsLuiz RvNo ratings yet

- 2n7000 TransistorDocument11 pages2n7000 TransistoramirnasrabadiNo ratings yet

- Isc BU103A: Isc Silicon NPN Power TransistorDocument2 pagesIsc BU103A: Isc Silicon NPN Power TransistorAnca SterianNo ratings yet

- Features: Vishay SemiconductorsDocument4 pagesFeatures: Vishay SemiconductorsAnca SterianNo ratings yet

- Rfg70N06, Rfp70N06, Rf1S70N06, Rf1S70N06Sm: 70A, 60V, Avalanche Rated, N-Channel Enhancement-Mode Power MosfetsDocument6 pagesRfg70N06, Rfp70N06, Rf1S70N06, Rf1S70N06Sm: 70A, 60V, Avalanche Rated, N-Channel Enhancement-Mode Power MosfetsRomário CaribéNo ratings yet

- SMP60N06 PDFDocument5 pagesSMP60N06 PDFAnca SterianNo ratings yet

- Metal Oxide Varistor 7mm Disc Metal Oxide Varistor 7mm DiscDocument1 pageMetal Oxide Varistor 7mm Disc Metal Oxide Varistor 7mm DiscAnca SterianNo ratings yet

- Irf3205 PDFDocument9 pagesIrf3205 PDFJuanito Naxito Jebus ArjonaNo ratings yet

- MC34163P DatasheetDocument16 pagesMC34163P DatasheetAnca SterianNo ratings yet

- GoodDocument35 pagesGoodapi-3721578No ratings yet

- Irf3205 PDFDocument9 pagesIrf3205 PDFJuanito Naxito Jebus ArjonaNo ratings yet

- RFG70N06, RFP70N06, RF1S70N06, RF1S70N06SM: 70A, 60V, 0.014 Ohm, N-Channel Power Mosfets FeaturesDocument9 pagesRFG70N06, RFP70N06, RF1S70N06, RF1S70N06SM: 70A, 60V, 0.014 Ohm, N-Channel Power Mosfets FeaturesAnca SterianNo ratings yet

- SMP60N06Document5 pagesSMP60N06Anca SterianNo ratings yet

- SUP/SUB70N06-14: Vishay SiliconixDocument5 pagesSUP/SUB70N06-14: Vishay SiliconixAnca SterianNo ratings yet

- STP40NF10 STB40NF10 - STB40NF10-1Document12 pagesSTP40NF10 STB40NF10 - STB40NF10-1Anca SterianNo ratings yet

- FRCC - PC.004.B2.22-MT-MTZ-Feb2018 - DanfossDocument40 pagesFRCC - PC.004.B2.22-MT-MTZ-Feb2018 - DanfossAnca SterianNo ratings yet

- MTZ36-4VM - Danfoss CompressorDocument3 pagesMTZ36-4VM - Danfoss CompressorAnca SterianNo ratings yet

- Denfoss ValveDocument3 pagesDenfoss Valvesaifisameer69No ratings yet

- Matrices and Vectors. - . in A Nutshell: AT Patera, M Yano October 9, 2014Document19 pagesMatrices and Vectors. - . in A Nutshell: AT Patera, M Yano October 9, 2014navigareeNo ratings yet

- ADMT Guide: Migrating and Restructuring Active Directory DomainsDocument263 pagesADMT Guide: Migrating and Restructuring Active Directory DomainshtoomaweNo ratings yet

- History of Drilling PDFDocument9 pagesHistory of Drilling PDFNguyen Van TinhNo ratings yet

- ITCNASIA23 - Visitor GuideDocument24 pagesITCNASIA23 - Visitor Guideibrahim shabbirNo ratings yet

- 2021-01-01 - Project (Construction) - One TemplateDocument1,699 pages2021-01-01 - Project (Construction) - One TemplatemayalogamNo ratings yet

- King Saud UniversityDocument10 pagesKing Saud UniversitypganoelNo ratings yet

- 6 - European Cluster Partnership For Excellence - European Cluster Collaboration PlatformDocument5 pages6 - European Cluster Partnership For Excellence - European Cluster Collaboration PlatformDaniela DurducNo ratings yet

- Sinamics g120p Cabinet Catalog d35 en 2018Document246 pagesSinamics g120p Cabinet Catalog d35 en 2018Edgar Lecona MNo ratings yet

- Retailing PPT (Shailwi Nitish)Document14 pagesRetailing PPT (Shailwi Nitish)vinit PatidarNo ratings yet

- Java Edition Data Values - Official Minecraft WikiDocument140 pagesJava Edition Data Values - Official Minecraft WikiCristian Rene SuárezNo ratings yet

- Medical Equipment Quality Assurance For Healthcare FacilitiesDocument5 pagesMedical Equipment Quality Assurance For Healthcare FacilitiesJorge LopezNo ratings yet

- Wood ReportDocument36 pagesWood Reportメルヴリッ クズルエタNo ratings yet

- New Text DocumentDocument13 pagesNew Text DocumentJitendra Karn RajputNo ratings yet

- Chandigarh Distilers N BotlersDocument3 pagesChandigarh Distilers N BotlersNipun GargNo ratings yet

- Salwico CS4000 Fire Detection System: Consilium Marine ABDocument38 pagesSalwico CS4000 Fire Detection System: Consilium Marine ABJexean SañoNo ratings yet

- 5 - Perception and Individual Decision Making in Organizational BehaviorDocument25 pages5 - Perception and Individual Decision Making in Organizational BehaviorJanaVrsalovićNo ratings yet

- TRAVEL POLICY CARLO URRIZA OLIVAR Standard Insurance Co. Inc - Travel Protect - Print CertificateDocument4 pagesTRAVEL POLICY CARLO URRIZA OLIVAR Standard Insurance Co. Inc - Travel Protect - Print CertificateCarlo OlivarNo ratings yet

- Context in TranslationDocument23 pagesContext in TranslationRaluca FloreaNo ratings yet

- How Muslim Inventors Changed The WorldDocument4 pagesHow Muslim Inventors Changed The WorldShadab AnjumNo ratings yet

- Phenomenology of The SelfDocument5 pagesPhenomenology of The SelfGuilherme CastelucciNo ratings yet

- Approved College List: Select University Select College Type Select MediumDocument3 pagesApproved College List: Select University Select College Type Select MediumDinesh GadkariNo ratings yet

- 4D Beijing (Muslim) CHINA MATTA Fair PackageDocument1 page4D Beijing (Muslim) CHINA MATTA Fair PackageSedunia TravelNo ratings yet

- Landcorp FLCC Brochure 2013 v3Document6 pagesLandcorp FLCC Brochure 2013 v3Shadi GarmaNo ratings yet

- Training Course For 2 Class Boiler Proficiency Certificate (Gujarat Ibr)Document3 pagesTraining Course For 2 Class Boiler Proficiency Certificate (Gujarat Ibr)JAY PARIKHNo ratings yet

- Steve Jobs TalkDocument3 pagesSteve Jobs TalkDave CNo ratings yet

- OM Part B - Rev1Document45 pagesOM Part B - Rev1Redouane BelaassiriNo ratings yet