Professional Documents

Culture Documents

Evaluacion Final Sistemas Digitales y Ensambladores PDF

Evaluacion Final Sistemas Digitales y Ensambladores PDF

Uploaded by

Mauro Rodriguez0 ratings0% found this document useful (0 votes)

3 views24 pagesOriginal Title

Evaluacion final sistemas digitales y ensambladores.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

3 views24 pagesEvaluacion Final Sistemas Digitales y Ensambladores PDF

Evaluacion Final Sistemas Digitales y Ensambladores PDF

Uploaded by

Mauro RodriguezCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 24

121572020

Evaluacion final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO?]

Evaluacion final - Escenario 8

Fecha de entrega 12 de mayo en 23:55 Puntos 100

Disponible 9 de mayo en 0:00 - 12 de mayo en 23:55 4 des

Limite de tiempo 90 minutos

Intentos permitidos 2

Preguntas 20

Instrucciones

hitpspolInstucture.comicourses/1390iquizos/40126

28

121512020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO?]

Apreciado estudiante, presenta tus examenes

como SERGIO EL ELEFANTE,

quien con honestidad, usa su sabiduria para mejorar cada dia.

Lee detenidamente las siguientes indicaciones y minimiza inconvenientes

1. Tienes dos intentos para desarrollar 7, Solo. puedes recurrir al si

wuevaluacion fbn caso de un. pr

nologico.

2. Si respordiste uno de fos intentos

sin ningin inconveniente y tuviste 8, Si tuexamenincluye pregun

problemas con el otro, el examen no —_respuestas. abiert:

sera habilitada nuevamente. ealificadas autor

requieren are

3. Cuando estés rescondiendo. la

evaluacién, evita abric_péginas. 9. Si presentas inconvenientes

diferentes'a tu examen. Esto’ pede resentacion del examen,

ocasionar el cierre del mismo y ‘a Crear un caso explicando ba situ

pérdida de un intento, djuntanda siempre imagen

eiidencia, con fecha y hors, pi

4, Asegiirate detener buenaconexién Soporte Tecnologico pueda br

a interRet, cierra cualquier programa _una respuesta entes posible,

que pueda consumireldnchade banca

no utlices internet movil 10. Podrés verificar la soluciér

examen Ginicamente durante

5. Debes empezar a responder el horassiguientesal cerre.

examen por lol menes dos hores antes

del clerra, es decir, maximo a las 9:55 ‘tI, Te recomendamos evitar

p.m. Sillégada les 11:55 p.m.nolohas _telefanos inteligentes o tabletas

arviado, él mismo se cermar y no presentacion “de tus acti

podra ser calif evaluativas

6. El tiempo maximo que tienes para 12. Al_terminar de_ respon

résdlver cada eveluacion es de'90 examen debes dar clic ert el

minutos. “Erviar todo y terminar’ de ot

elexamen permanecerd abierte

{Confiamos en que sigas, paso a paso, en el camino hacia la excelencia acz

Das tu palabra de que reslizaras esta actividad esumiendo de coraznn

PACTO DE HONOR? sy

[vovors entra anon ]

Historial de intentos

Intento Hora Puntaje

hitpspolInstucture.comicourses/1390iquizos/40126 228

12182020 Evaluacion nal -Escenaro 8: PRIMER BL OQUE-TEORICO - PRACTICOISISTEMAS DIGITALES ¥ ENSAMBLADORES{GRUPO?]

Intento Hora Puntaje

MAS RECIENTE Intento 4 40 minutos 95 de 100

@ Las respuestas correctas estardn disponibles del 13 de mayo en 23:55 al 14 de mayo en 23:56.

Puntaje para este intento: 95 de 100

Entregado el 12 de mayo en 2:16

Este intento tuvo una duracién de 40 minutos.

Pregunta 1 0/5 pts

Existen diferentes tipos de Latches y Flip-Flops: S-R y D son algunos de

ellos. La diferencia en su funcionamiento radica en el tipo de sefial de

control utilizada para el cambio de estado, asi como en la diferencia que

las sefiales de entrada pueden generar en esas transiciones. Dados los

siguientes diagramas:

EN

Un flip-flop 5 — R con entrada de habilitacion,

Un flip-flop S-R con entrada de habilitacién.

En este caso, no se trata de un flip-flop, pues la entrada de

habilitacién funciona por nivel y no por flanco. Adicionalmente, es

tipo S-R, pues sus entradas S y R estan sin negar.

Un lal

R con entrada de habilitacién.

Un latch § — Recon entrada de habilit

hitpspolInstucture.comicourses/1390iquizos/40126 28

121572020 Evaluacion final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO?]

Pregunta 2 5/5 pts

Los circuitos légicos pueden dividirse en dos categorias principales,

segiin diferentes aspectos, como la interaccién que las salidas tengan

con sus entradas, de memoria entre otros. Segiin lo anterior, existen

circuits combinacionales y circuitos secuenciales. Para el siguiente

circuito,

Circuito secuencial, dado que las salidas YO y Y1 estan retroalimentadas.

Efectivamente, la retroalimentacién presente en YO y Y1 hacen que

el circuito sea un circuit légico secuencial. En este caso se trala de

Un Flip-Flop tipo D, con entrada de Enable.

Circuito combinacional, pu

ssta formado por la combi

compuertas basicas tipo NOT y NAND.

\dos los elementos estan conectad

hasta la salida

hitpspolInstucture.comicourses/1390iquizz0s/40126 4124

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO2]

Circuito combinacional, pues evidentement

en la salida una compuerta »

Pregunta 3

rata de una compuertz

nla salida Y

5/5 pts

Todos los circuitos combinacionales vistos hasta ahora pueden ser

representados mediante sus tablas de verdad.

De acuerdo con la siguiente tabla de verdad (A y B son entradas, Y1-YO

salidas):

B

S

YO

A

0 | 0

0} 1

L | 0

l/l

Pe Oo;o|o>

0

|

1

0

El circuito es un sumador con acarreo.

Es correcto, pues A+B da respectivamente 0, 1, 1 y 0 (éste tiltimo

con acarreo en Y1).

a YO se puede

hitpspolInstucture.comicourses/1390iquizz0s/40126

5128

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO2]

El circuito es un o, de binario a BCD

El circuito funciona como un compara

is dos salidas

caracteristic

Pregunta 4 5/5 pts

Los circuitos selectores (multiplexores) permiten escoger una de sus

entradas y mostrarla en sus salidas, mientras que los circuitos

distribuidores (demultriplexores) hacen la tarea opuesta, distribuyendo

sus entradas a una de varias salidas.

Usted encuentra un circuito integrado, y en el datasheet puede ver que el

elemento tiene ocho (8) entradas de datos, cuatro (4) salidas de datos y

una (1) entrada de seleccién de un bit. Se podria decir que este circuit

Puede usarse como un demultiplexor, utilizando la entrada de 4 bits y su

8 bits,

Es un multiplexor con 2 entradas de 4 bits, el selector permite escoger

cual de las dos entradas se muestra en los 4 bits de salida,

De acuerdo a lo visto, existen muttiplexores para datos de mas de 1

bit. En este caso se trata de un multiplexor cuyos datos tiene 4 bits,

el selector permite escoger una de las 2 entradas de 4 bits y

representarla en la salida.

Es un multiplexor con 8 entradas de un bit, el selector

una de las 4 salidas para mostrar el dato de entrada

hitpspolInstucture.comicourses/1390iquizz0s/40126 128

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO2]

Es un decodificador de 8 a 4 lineas, cuya entrada de selecci6n per

ager el tipo de decodificacin a usar

Pregunta 5 5/5 pts

Los multiplexores, ademas de ser usados para la seleccién de datos,

pueden funcionar como generadores de funciones légicas. Partiendo de

una tabla de verdad, se seleccionan los mintérminos y se ponen a un

nivel de voltaje ALTO (Conectados a VCC) Las demas entradas se ponen

en BAJO (Conectados a tierra). De esta manera, al poner en las entradas

de seleccién la combinacién adecuada, se puede ver el resultado en la

salida. En el siguiente diagrama, se muestra un generador de funciones

légicas, con la entrada de seleccién en 000

{Qué valor habré en las salidas, si la entrada de selecoién en el

multiplexor se pone en 011?

hitpspolInstucture.comicourses/1390iquizz0s/40126 1124

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO2]

YO esta en 1 y Y1 esté en 0,

Ala salida del multiplexor habra un nivel BAJO con la seleccién en

011, por lo tanto el demultiplexor mostrara el dato de entrada en su

salida YO, mientras que en Y1 mostrara un nivel BAJO.

Oy Y1 esta en 0.

Pregunta 6 5/5 pts

Los circuitos combinacionales estan conformados por la unién de

diferentes compuertas légicas, que combinan sus caracteristicas para

obtener una salida compuesta.

De acuerdo con la siguiente tabla de verdad (A y B son entradas, Y3-Y2-

Y1-Y0 salidas) para el circuito decodificador:

A | B | ¥Y3 | ¥2 | Y1| YO

0

0

1

1

rISolR |S

S/S

0

0

l

0

o|SC|-|o

SS 1S) =

{Cudl de las siguientes afirmaciones es falsa?:

La salida Y:

hitpspolInstucture.comicourses/1390iquizz0s/40126 28

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

La salida Y2 se puede implementar con una AND y un inversor.

La salida YO se pi con una NOR.

La salida Y1 se puede implementar utlizando una XNOR.

Es correcto, la salida Y1 no se podria obtener directamente usando

una XOR.

Pregunta 7 515 pts

Los flip-flops son circuitos multivibradores, que oscilan entre dos estados.

El cambio de estado depende tanto de las entradas de datos, como de

los cambios en los pulsos de la entrada de control (CLK). El control

puede darse por pulsos positivos o negativos, segin la construccién

interna del flip-flop. Para el siguiente flip-flop, dadas las sefiales en las.

entradas J, K y CLK

J

i

pox K

se ab

CLK

Es posible afirmar que la salida tomara la forma:

oT 2 ol [i

hitpspolInstucture.comicourses/1390iquizos/40726 rae

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

4

Pregunta 8 5/5 pts

Las maquinas de estados finitos pueden ser utilizadas para controlar

diferentes actuadores, dadas unas sefiales de control y unos estados

internos del sistema.

usted le piden que analice un circuito digital, y lo tinico que le entregan

es el siguiente diagrama de estados:

Para usted, la aplicacién de! diagrama puede ser:

hitpspolInstucture.comicourses/1390iquizz0s/40126 10128

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO?]

Un sistema de iluminacién con dos bombillos. El sistema permite encender

de manera secuencial una o dos luces, o apagarlas completamente.

Si se toman los estados del sistema como dos sefiales de salida,

funciona perfectamente para la aplicacién mencionada.

Un sistema de conteo entre los numeros 0 y

en binario. Est

requiere una sefial externa para realizar conteo bidireccion

‘a maquina de Mealy, cuyos estados internos son de dos bits y las

iciones de un bit.

Un sistema intermitente, entre Oy 1. D el

na se mantiene en 0.0 cambia a1

Pregunta 9 5/5 pts

Los contadores hacen uso de la divisién de frecuencia, para realizar las

cuentas de forma binaria. Seguin sea el uso de las entradas asincronas,

es posible dividir en dos clases los tipos de contadores: sincronos 0

asincronos.

Si se quisiera realizar una cuenta entre 0 y 7 en binario, utilizando un

contador tipo sincrono, el circuit adecuado seria:

hitpspolInstucture.comicourses/1390iquizz0s/40126 28

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO?]

Pregunta 10 5/5 pts

Las compuertas NAND y NOR tienen la particularidad que pueden ser

usadas como compuertas universales. Esto quiere decir que, usando un

solo tipo de compuerta, es posible generar las funciones basicas AND,

NOT y OR. A partir de estas compuertas basicas es posible construir

circuitos mas complejos.

El siguiente esquema se ha desarrollado usando tinicamente compuertas

NOR:

hitpspolInstucture.comicourses/1390iquizz0s/40126 12R8

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

Cual es la funcionalidad de este circuito?

Es un circuito comparador.

Se trata de un circuito comparador, la salida Y1 indica si A = B, la

salida YO si A > By la salida Y2 si SSA

Es un circuito decodificador de binario a decimal.

Es un circuito semi-sun

Es un circuito multiplexor con una linea de datos y una de sele«

Pregunta 11 515 pts

Junto con los contadores, los registros de desplazamiento son otra de las,

aplicaciones mas usuales para los circuitos secuenciales. En estos, una

sefial se desplaza por el circuito, segiin su construccién:

hitpspolInstucture.comicourses/1390iquizz0s/40126 1328

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

Aun registro de desplazamiento con entrada en serie y salida en paralelo

de 4 bits se le aplica una sefial en su entrada:

ok PLELP LE LLL ELA

ay NS

{Cual es la grafica en la salida?

ern Ann

‘Se puede apreciar que la forma de onda en la salida es la misma

forma de onda en la entrada, desplazada en el tiempo. Ademas fi

Pregunta 12 5/5 pts

Una expresién Suma de Productos -SOP-, (sum of products) esta

conformada por varios términos productos (multiplicacién booleana) de

literales (variable afirmada o negada) que se agrupan en una suma

booleana. Dada la siguiente tabla de verdad:

hitpspolInstucture.comicourses/1390iquizz0s/40126 14128

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

Tabla de verdad

A

B

Cc

Y

0

0

0

0

|

l

1

1

ES So ole | ore

ee ee ee ee)

en

Es posible afirmar que la Suma de Productos asociada es:

hitpspolInstucture.comicourses/1390iquizz0s/40126

19128

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO2]

La que contiene los mintérminos

Y = m(1,2,5,7) = My + Mz + Ms + My

La que contiene los maxtér

minos Mo, M3, My, Ms

Igual alos términos ¥ = ABC + ABC + ABC + ABC

Se trata de la expresién correcta, dadas las salidas de la tabla de

verdad.

Pregunta 13 5/5 pts

Un sumador completo es un tipo de circuito combinacional, que recibe,

ademas de los operandos de entrada, un bit de acarreo de entrada (Cin),

proveniente de otra suma previa. El siguiente circuito sumador se utiliza

en un sumador de 8 bits,

En su operacién, el sumador recibe los siguientes datos: A=1, B=0 y

Cin=1, el resultado en la salida deberia ser:

Y =1yCout =0.

hitpspolInstucture.comicourses/1390iquizz0s/40126 16128

121572020

Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO2]

0 y Cout = 0.

Y =0yCout =1.

ly Cout

Pregunta 14 515 pts

Los latch pueden, o no, tener entrada de habilitacién. Ademds, segun

como sean sus entradas (negadas 0 no) su funcionamiento puede variar.

Para el siguiente latch \bar{S}-\bar{R}.

Se puede afirmar que la sefial en la salida corresponde con la forma de

onda:

3

hitpspolInstucture.comicourses/1390iquizz0s/40126

1728

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

La forma de onda seleccionada cumple con los estados del Latch: t1

SET, (2: No hay cambio, t3: RESET, t4: SET, tS: RESET, t6: No hay

‘cambio, t7: Condicién invalida,

Pregunta 15 5/5 pts

Un programa de computador hace uso de apuntadores para almacenar

las direcciones en memoria de variables, estructura, funciones, entre

otros. Dichas direcciones son mostradas normalmente en formato

hexadecimal.

Alleer dos direcciones en memoria, el computador le entrega la siguiente

informacién AA2C0200 y AA2C0300. Se puede decir que las dos

direcciones:

n direct osiciones una de la otra

n conti

jenen una exte

32 bits.

Se pueden representar en binario como: 10101010 00101100 00000010

00000000 y 10101010 00101100 00000011 00000000

Las conversiones de hexadecimal a binario son correctas,

Pregunta 16 515 pts

Las maquinas de estado se pueden representar mediante sus diagramas

de estado, o mediante las tablas de transiciones correspondientes. Dado

hitpspolInstucture.comicourses/1390iquizz0s/40126 18128

‘a1s2020 Evaluacon fa -Escenaro 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

la siguiente maquina de Mealy:

1/0

SES

oo

( ‘\ O/L

( « }—"

Nee Lo My

" Oe

fo™

: bay 4

\ \

‘|

e

0

\

c

0/1

Se podria decir que una de las siguientes filas NO corresponde con el

diagrama:

1

Estado presente Taira siado siguiente Salida

x 3 D 3

2

Fatado presente Taira stad siguiente Salida

x T B °

3

Tsiado presente Tnivada Fstado siguiente Salida

B ° 5 T

4

stad presente nia Estado siguiente Salida

B T c °

2

hitpspolInstucture.comicourses/1390iquizz0s/40126 t928

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO?]

Este estado no corresponde a un cambio adecuado, pues la salida A

no cambia de manera acorde con la entrada. La salida deberia ser 1

Pregunta 17 515 pts

Una de las aplicaciones en las que mas se utilizan los flip-flops es en el

disefio de contadores, bien sea de tipo sincrono o asincronos. Dado el

siguiente circuito:

Es posible afirmar que se trata de un:

Contador asincrono con médulo 7.

Contador sincrono de 4 bits

Contador asincrono de 4 bits (médulo 1

Contador asincrono con médulo 10.

Es correcto, pues el contador cuenta con un circuito de reseteo, que

pone la cuenta en 0 de manera asincrona cuando el estado del

contador es 1010 (10 en decimal).

hitpspolInstucture.comicourses/1390iquizz0s/40126

20124

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

Pregunta 18 515 pts

Los circuitos combinacionales ven sus salidas afectadas directamente por

los valores en las entradas. La relacién entre las entradas y las salidas de

un circuito combinacional se pueden analizar mediante sus tablas de

verdad. Dado el siguiente circuito combinacional

Es posible afirmar que su funcionamiento es equivalente al de:

Una compuerta XNOR

Una compuerta XOR

Se trata finalmente de una compuerta XOR. Antes de la compuerta

NOT cercana a la salida, funciona como una XNOR, pero esa

negacién al final la vuelve una XOR. Es decir que, para este circuito,

silas dos entradas son iguales, la salida es 0. Silas dos entradas

son diferentes, la salida es 1

Una compu

Una compuerta Negativa-OR

Pregunta 19 5/5 pts

hitpspolInstucture.comicourses/1390iquizz0s/40126 21124

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

Las maquinas de estado se pueden representar mediante sus diagramas

de estado, o mediante las tablas de transiciones correspondientes. Dado

la siguiente maquina de Moore:

Se podria decir que una de las siguientes filas NO corresponde con el

diagrama:

1

Estado presente Earada Estado siguiente Salida

D ° ¢ T

2

Eatado presente Eatiada Estado siguiente Salida

a T a o

3

TEsiado presente Enid Estado siguiente Salida

x 1 B 1

4

Estado presente nirada Estado siguiente Salida

c 1 a 1

3

hitpspolInstucture.comicourses/1390iquizz0s/40126

pares

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAVBLADORES-{GRUPO2]

1

Este estado no corresponde a un cambio adecuado, pues la salida C

estaria cambiando de 0a 1

Pregunta 20 515 pts

Los mapas de Karnaugh permiten realizar agrupacién de expresiones,

con el fin de simplificar la expresién total de un sistema dado. Dado el

siguiente mapa de Kamaugh:

C.D

00 01 11 10

oo/M o o 0

mol| o o 0

= 1

10 o 60

hitpspolInstucture.comicourses/1390iquizz0s/40126 23124

121572020 Evaluacin final -Escenario 8: PRIMER BLOQUE-TEORICO - PRACTICOISISTEMAS DIGITALES Y ENSAMBLADORES-{GRUPO2]

Es posible afirmar entonces que la expresién minima resultante es:

A+B)(A+D)(6+D

Y = AB+ AD+CD.

Y¥ =AB+AD+OD.

La expresién mostrada es la correcta y se obtiene de lo 3 grupos que

se ven olaramente en la imagen.

Y = ACD+ ACD + AB+ ABC

Puntaje del examen: 95 de 100

hitpspolInstucture.comicourses/1390iquizos/40126

24124

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Evaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Virtual - Gerencia de Proyectos Informáticos - (Grupo b02)Document4 pagesEvaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Virtual - Gerencia de Proyectos Informáticos - (Grupo b02)Junnior Stibens Florez CruzNo ratings yet

- Quiz Escenario 8 - EGADocument8 pagesQuiz Escenario 8 - EGAJunnior Stibens Florez CruzNo ratings yet

- Evaluacion Final - Arquitectura Del SoftwareDocument7 pagesEvaluacion Final - Arquitectura Del SoftwareJunnior Stibens Florez CruzNo ratings yet

- Evaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Virtual - Teoría de La Seguridad - (Grupo b02)Document12 pagesEvaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Virtual - Teoría de La Seguridad - (Grupo b02)Junnior Stibens Florez Cruz100% (1)

- Evaluacion Final - Escenario 8 - Arquitectura Del SoftwareDocument8 pagesEvaluacion Final - Escenario 8 - Arquitectura Del SoftwareJunnior Stibens Florez CruzNo ratings yet

- Utilizar MCD para Resolver SituacionesDocument1 pageUtilizar MCD para Resolver SituacionesJunnior Stibens Florez Cruz0% (1)

- Evaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Front-End - (Grupo b01)Document7 pagesEvaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Front-End - (Grupo b01)Junnior Stibens Florez CruzNo ratings yet

- Medidas Del RelojDocument2 pagesMedidas Del RelojJunnior Stibens Florez CruzNo ratings yet

- MamíferosDocument3 pagesMamíferosJunnior Stibens Florez CruzNo ratings yet

- NombersDocument7 pagesNombersJunnior Stibens Florez CruzNo ratings yet

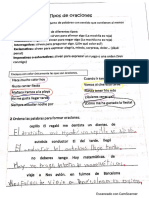

- Tipo de Oraciones y LecturaDocument3 pagesTipo de Oraciones y LecturaJunnior Stibens Florez CruzNo ratings yet

- Colores SecundariosDocument2 pagesColores SecundariosJunnior Stibens Florez CruzNo ratings yet

- RazonamientoDocument1 pageRazonamientoJunnior Stibens Florez CruzNo ratings yet

- Evaluacion Final - Escenario 8 - PRIMER BLOQUE-TEORICO - PRACTICO - SISTEMAS DIGITALES Y ENSAMBLADORESDocument25 pagesEvaluacion Final - Escenario 8 - PRIMER BLOQUE-TEORICO - PRACTICO - SISTEMAS DIGITALES Y ENSAMBLADORESJunnior Stibens Florez CruzNo ratings yet