Professional Documents

Culture Documents

ACA - Syll PDF

ACA - Syll PDF

Uploaded by

Shilpa Shridhar0 ratings0% found this document useful (0 votes)

12 views2 pagesOriginal Title

ACA _syll.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

12 views2 pagesACA - Syll PDF

ACA - Syll PDF

Uploaded by

Shilpa ShridharCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

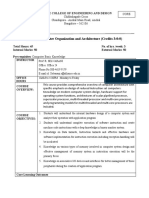

ADVANCED COMPUTER ARCHITECTURES

[As per Choice Based Credit System (CBCS) scheme]

(Effective from the academic year 2017 - 2018)

SEMESTER – VII

Subject Code 17CS72 IA Marks 40

Number of Lecture Hours/Week 4 Exam Marks 60

Total Number of Lecture Hours 50 Exam Hours 03

CREDITS – 04

Module – 1 Teaching

Hours

Theory of Parallelism: Parallel Computer Models, The State of Computing, 10 Hours

Multiprocessors and Multicomputer ,Multivector and SIMD Computers ,PRAM

and VLSI Models, Program and Network Properties ,Conditions of Parallelism,

Program Partitioning and Scheduling, Program Flow Mechanisms, System

Interconnect Architectures, Principles of Scalable Performance, Performance

Metrics and Measures, Parallel Processing Applications, Speedup Performance

Laws, Scalability Analysis and Approaches.

Module – 2

Hardware Technologies: Processors and Memory Hierarchy, Advanced Processor 10 Hours

Technology, Superscalar and Vector Processors, Memory Hierarchy Technology,

Virtual Memory Technology.

Module – 3

Bus, Cache, and Shared Memory ,Bus Systems ,Cache Memory Organizations 10 Hours

,Shared Memory Organizations ,Sequential and Weak Consistency Models

,Pipelining and Superscalar Techniques ,Linear Pipeline Processors ,Nonlinear

Pipeline Processors ,Instruction Pipeline Design ,Arithmetic Pipeline Design

(Upto 6.4).

Module – 4

Parallel and Scalable Architectures: Multiprocessors and Multicomputers 10 Hours

,Multiprocessor System Interconnects, Cache Coherence and Synchronization

Mechanisms, Three Generations of Multicomputers ,Message-Passing

Mechanisms ,Multivector and SIMD Computers ,Vector Processing Principles

,Multivector Multiprocessors ,Compound Vector Processing ,SIMD Computer

Organizations (Upto 8.4),Scalable, Multithreaded, and Dataflow Architectures,

Latency-Hiding Techniques, Principles of Multithreading, Fine-Grain

Multicomputers, Scalable and Multithreaded Architectures, Dataflow and Hybrid

Architectures.

Module – 5

Software for parallel programming: Parallel Models, Languages, and Compilers 10 Hours

,Parallel Programming Models, Parallel Languages and Compilers ,Dependence

Analysis of Data Arrays ,Parallel Program Development and Environments,

Synchronization and Multiprocessing Modes. Instruction and System Level

Parallelism, Instruction Level Parallelism ,Computer Architecture ,Contents,

Basic Design Issues ,Problem Definition ,Model of a Typical Processor

,Compiler-detected Instruction Level Parallelism ,Operand Forwarding ,Reorder

Buffer, Register Renaming ,Tomasulo’s Algorithm ,Branch Prediction,

Limitations in Exploiting Instruction Level Parallelism ,Thread Level

Parallelism.

Course outcomes: The students should be able to:

• Understand the concepts of parallel computing and hardware technologies

• Illustrate and contrast the parallel architectures

• Recall parallel programming concepts

Question paper pattern

The question paper will have ten questions.

There will be 2 questions from each module.

Each question will have questions covering all the topics under a module.

The students will have to answer 5 full questions, selecting one full question from each

module.

Text Books:

1. Kai Hwang and Naresh Jotwani, Advanced Computer Architecture (SIE): Parallelism,

Scalability, Programmability, McGraw Hill Education 3/e. 2015

Reference Books:

1. John L. Hennessy and David A. Patterson, Computer Architecture: A quantitative

approach, 5th edition, Morgan Kaufmann Elseveir, 2013

You might also like

- CSE 7th Sem SyllabusDocument14 pagesCSE 7th Sem SyllabusPujit GangadharNo ratings yet

- Aca CoDocument2 pagesAca Cojoooom100% (1)

- Embedded SystemsDocument2 pagesEmbedded SystemsGanesh GoturNo ratings yet

- VII ISE 2015 SyllabusDocument27 pagesVII ISE 2015 SyllabusHeenaNo ratings yet

- EngineeringDocument139 pagesEngineeringCastro HamiltonNo ratings yet

- 15CS651Document9 pages15CS651Tanmay MukherjeeNo ratings yet

- Advances in Operating SystemsDocument2 pagesAdvances in Operating SystemsRaghavendra PhaydeNo ratings yet

- 15IS72Document2 pages15IS72anamsuhail1432No ratings yet

- 14th SchemeDocument99 pages14th SchemeHEMANTH KUMARNo ratings yet

- Scssyll PDFDocument58 pagesScssyll PDFAsh HNo ratings yet

- Vtu 5th Sem Open ElectivesDocument10 pagesVtu 5th Sem Open ElectivesRamya ShreeNo ratings yet

- IssyllDocument138 pagesIssyllanser pashaNo ratings yet

- Issyll PDFDocument141 pagesIssyll PDFJwkk AjkNo ratings yet

- 17CS834 SMSDocument2 pages17CS834 SMSHarsh KumarNo ratings yet

- Client-Side Web DevelopmentDocument19 pagesClient-Side Web DevelopmentOluwaferanmi SamsonNo ratings yet

- Engineering Mathematics-Iv: This Course Will Enable Students ToDocument28 pagesEngineering Mathematics-Iv: This Course Will Enable Students ToPradeep DeshpandeNo ratings yet

- SSCD SysDocument3 pagesSSCD SysAbhijeet ThamakeNo ratings yet

- Computer Organization: Course ObjectivesDocument2 pagesComputer Organization: Course Objectivesರಘು ಕಟಗಲ್ಲNo ratings yet

- Syllabus of Diploma Engineering Computer Engineering Semester: IV Subject Code: 09CE1405 Subject Name: Operating SystemDocument5 pagesSyllabus of Diploma Engineering Computer Engineering Semester: IV Subject Code: 09CE1405 Subject Name: Operating SystemasgamingNo ratings yet

- OS - 22 SchemeDocument4 pagesOS - 22 Schemenithyamohan82No ratings yet

- CS405 Computer System Architecture PDFDocument3 pagesCS405 Computer System Architecture PDFvonacoc49No ratings yet

- McasyllDocument144 pagesMcasyllNameera NameeraNo ratings yet

- Cctsyll MtechDocument44 pagesCctsyll MtechSunil KumarNo ratings yet

- Course Objectives:: University of Mumbai, Information Technology (Semester V and VI) (Rev-2012)Document4 pagesCourse Objectives:: University of Mumbai, Information Technology (Semester V and VI) (Rev-2012)Falgun PATELNo ratings yet

- Software EngineeringDocument1 pageSoftware EngineeringVijayaraghavan AravamuthanNo ratings yet

- Parallel Computing - Major Elective - IIIDocument3 pagesParallel Computing - Major Elective - IIImuninder ITNo ratings yet

- 15 Cs 63Document424 pages15 Cs 63SARABJEET KEWATNo ratings yet

- IT801-N Distributed and Parallel ComputingDocument4 pagesIT801-N Distributed and Parallel Computingcixiv89132No ratings yet

- 8th Sem Vtu SyllabusDocument15 pages8th Sem Vtu SyllabusshashankNo ratings yet

- COAVITDocument3 pagesCOAVITnikshithNo ratings yet

- Parallel and Distributed SystemsDocument3 pagesParallel and Distributed Systemsarungupta652No ratings yet

- 6 Syllabus ISEDocument22 pages6 Syllabus ISEDHANUSH KILVIDHI VIJAYNo ratings yet

- COS1077B C ProgrammingDocument48 pagesCOS1077B C ProgrammingmahendrasuryavanshiNo ratings yet

- MCA 1st & 2nd FinalDocument12 pagesMCA 1st & 2nd FinalbibekbcNo ratings yet

- Course Description-Computer Organisation and ArchitectureDocument4 pagesCourse Description-Computer Organisation and ArchitectureShivang AgarwalNo ratings yet

- Web SyllabusDocument2 pagesWeb SyllabusRuthwik S GowdaNo ratings yet

- Ce763: Distributed System & Applications (Pe - I) : Teaching Scheme Theory Practical Total CreditDocument5 pagesCe763: Distributed System & Applications (Pe - I) : Teaching Scheme Theory Practical Total CreditpakuNo ratings yet

- Sitsyll PDFDocument57 pagesSitsyll PDFpreranaNo ratings yet

- MCA 5 SemesterDocument9 pagesMCA 5 SemestertimussharmaNo ratings yet

- Discrete Structure: Logic, Induction and ReasoningDocument8 pagesDiscrete Structure: Logic, Induction and ReasoningGovindaNo ratings yet

- VTU Digital Logic DesignDocument2 pagesVTU Digital Logic DesignArighna DebNo ratings yet

- ACA Important TopicDocument2 pagesACA Important TopicDhiraj JhaNo ratings yet

- CS 404 - COA Course PlanDocument8 pagesCS 404 - COA Course PlanAishwarya RajeshNo ratings yet

- 5th Sem Draft SyllDocument22 pages5th Sem Draft Syllhmr4everNo ratings yet

- M.Tech (MVD)Document2 pagesM.Tech (MVD)rishi tejuNo ratings yet

- Computer Organization 01Document22 pagesComputer Organization 01AbhinavNo ratings yet

- Course Plan S2024 CSC-252 Operating Systems (Initial Version)Document3 pagesCourse Plan S2024 CSC-252 Operating Systems (Initial Version)janishab1704No ratings yet

- DS Syllabus PDFDocument4 pagesDS Syllabus PDFBhushan JadhavNo ratings yet

- FOP SyllabusDocument5 pagesFOP SyllabuskhushbuceNo ratings yet

- Bahria University Lahore Campus: Department of Computer SciencesDocument10 pagesBahria University Lahore Campus: Department of Computer SciencesHussainNo ratings yet

- Kerala University s8 Syllabus 2008 SchemeDocument29 pagesKerala University s8 Syllabus 2008 SchemeJijo PJNo ratings yet

- M.Sc. (IT) FIRST YEAR (SEMESTER I & II) 2020-21 AND 2021-22Document23 pagesM.Sc. (IT) FIRST YEAR (SEMESTER I & II) 2020-21 AND 2021-22Harmanpreet KaurNo ratings yet

- 22ESC145 (C Programming)Document5 pages22ESC145 (C Programming)Prasanna M KNo ratings yet

- Comp Arch Syllabus 6-29-2017Document4 pagesComp Arch Syllabus 6-29-2017Karthikeya MamillapalliNo ratings yet

- CSE 115 - 115L Course Objective and OutcomeDocument6 pagesCSE 115 - 115L Course Objective and OutcomeRoksana IslamNo ratings yet

- PG Syllabus 2022Document66 pagesPG Syllabus 2022Anand BankadNo ratings yet

- 22ETC15J SyllabusDocument3 pages22ETC15J SyllabusChetan GhatageNo ratings yet

- Stochastic Modeling: A Thorough Guide to Evaluate, Pre-Process, Model and Compare Time Series with MATLAB SoftwareFrom EverandStochastic Modeling: A Thorough Guide to Evaluate, Pre-Process, Model and Compare Time Series with MATLAB SoftwareNo ratings yet

- Implementing the Stakeholder Based Goal-Question-Metric (Gqm) Measurement Model for Software ProjectsFrom EverandImplementing the Stakeholder Based Goal-Question-Metric (Gqm) Measurement Model for Software ProjectsNo ratings yet

- ACA Notes TechJourney PDFDocument206 pagesACA Notes TechJourney PDFPrakhyath JainNo ratings yet

- ACA Notes Diginotes PDFDocument283 pagesACA Notes Diginotes PDFPrakhyath JainNo ratings yet

- SS&CD Lab SyllabusDocument2 pagesSS&CD Lab SyllabusPrakhyath JainNo ratings yet

- Chat RoomDocument7 pagesChat RoomPrakhyath JainNo ratings yet

- Hawaii (: /HƏ Waɪi/ Listen Hawaiian (HƏ Vɐjʔi) State United StatesDocument3 pagesHawaii (: /HƏ Waɪi/ Listen Hawaiian (HƏ Vɐjʔi) State United StatesPrakhyath JainNo ratings yet

- Journey To The West Xiyou Ji X Yóu Jì: Chinese PinyinDocument3 pagesJourney To The West Xiyou Ji X Yóu Jì: Chinese PinyinPrakhyath JainNo ratings yet

- Research 2Document2 pagesResearch 2Prakhyath JainNo ratings yet

- CaterpillarDocument2 pagesCaterpillarPrakhyath JainNo ratings yet

- Machine Learning PythonDocument48 pagesMachine Learning PythonNarendra WiganaNo ratings yet

- CO - IF - 22412 - CO1: Date: 03 February 2021 Learning at Your DoorstepDocument18 pagesCO - IF - 22412 - CO1: Date: 03 February 2021 Learning at Your DoorstepVinayak KhadeNo ratings yet

- DT AssociateDocument60 pagesDT Associateantony vasquezNo ratings yet

- Challenging Task 5Document5 pagesChallenging Task 5TRISHIT DEVENDER GUPTA 20BIT0374No ratings yet

- Explore Computer Science CareersDocument20 pagesExplore Computer Science CareersIan WrightNo ratings yet

- Singly Linked Iist Programme As in "Understanding Pointers in C"-By Yashwant KanetkarDocument5 pagesSingly Linked Iist Programme As in "Understanding Pointers in C"-By Yashwant Kanetkararunesh198No ratings yet

- CNX200 and Expand Configuration Procedure CH PDFDocument6 pagesCNX200 and Expand Configuration Procedure CH PDFroshan mungurNo ratings yet

- Reduction of ER Model To Relational ModelDocument18 pagesReduction of ER Model To Relational ModelNamanNo ratings yet

- RVCE BE Placement 2023 StatisticsDocument63 pagesRVCE BE Placement 2023 Statisticsbchiranthan95204No ratings yet

- Informatica Error HandlingDocument7 pagesInformatica Error HandlingVikas Sinha100% (1)

- Lesson 2 String in PythonDocument27 pagesLesson 2 String in PythonJennifer Contreras100% (1)

- ASR For SamskrutaDocument8 pagesASR For SamskrutaShashank HollaNo ratings yet

- Proxmon Automating Web Application Penetration Testing: Jonathan WilkinsDocument21 pagesProxmon Automating Web Application Penetration Testing: Jonathan WilkinsDanny AdonisNo ratings yet

- Azure Cosmos DBDocument835 pagesAzure Cosmos DBLachezar VasilevNo ratings yet

- Project Report: Multipurpose PiDocument85 pagesProject Report: Multipurpose PiParth ParikhNo ratings yet

- Howto Rename Managed Target On Oracle EM 12c - DBA - Rodrigo Jorge - Oracle Tips and GuidesDocument1 pageHowto Rename Managed Target On Oracle EM 12c - DBA - Rodrigo Jorge - Oracle Tips and Guidesakammiea AhmedNo ratings yet

- Adb TutorialsDocument4 pagesAdb TutorialschatenileshNo ratings yet

- Lecture Week 11 - ML and Hierarchical PNsDocument31 pagesLecture Week 11 - ML and Hierarchical PNsfelixNo ratings yet

- PWP - Chapter 2Document40 pagesPWP - Chapter 2Mayur NarsaleNo ratings yet

- Delphi - Client ServerDocument9 pagesDelphi - Client Servermnogueira2012No ratings yet

- Rainbow: C/C++ Screening TestDocument4 pagesRainbow: C/C++ Screening TestMartand SinghNo ratings yet

- Google Translate - Google SearchDocument1 pageGoogle Translate - Google SearchNicole Alex Bustamante CamposNo ratings yet

- Kumar Jyotirmay: Technical SkillsDocument1 pageKumar Jyotirmay: Technical SkillsKumar JyotirmayNo ratings yet

- Mynulled - in All Link To Download Nulled PHP Script and Wordpress Theme N Plugin & Much More..Document12 pagesMynulled - in All Link To Download Nulled PHP Script and Wordpress Theme N Plugin & Much More..john mathewNo ratings yet

- Learn X in Y Minutes Where X Eq GroovyDocument8 pagesLearn X in Y Minutes Where X Eq Groovyg_teodorescuNo ratings yet

- Bank Simulator in JAVA (Swings)Document31 pagesBank Simulator in JAVA (Swings)Ankit MainiNo ratings yet

- 01 Ipo Programming ExamplesDocument4 pages01 Ipo Programming ExamplesAfïf SánqArëmániámylánystyNo ratings yet

- Interview QuestionsDocument10 pagesInterview QuestionsVikram VickyNo ratings yet

- COMMSCOPE - Antenna Sharing Configuration Builder ToolDocument6 pagesCOMMSCOPE - Antenna Sharing Configuration Builder Toolyou are awesomeNo ratings yet

- Developing A REST API Service: IBM Integration BusDocument29 pagesDeveloping A REST API Service: IBM Integration BusMinh GiaNo ratings yet